Объектом исследования данной работы является рассмотрение основных существующих подходов и средств к моделированию неисправностей МОП-структур, а также взаимодействия соединений в СБИС.

Цель работы - исследование различных путей повышения адекватности моделирования неисправностей МОП СБИС на переключательном уровне, а также исследование взаимодействия соединений в СБИС.

Возможность параллельных вычислений для булевых выражений позволяет эффективно реализовывать алгоритмы для моделирования неисправностей и псевдослучайной генерации проверяющих тестов.

Логическое моделирование

Моделирование поведения электронных цифровых устройств в настоящее время стало неотъемлемой частью автоматизации проектирования и диагностирования этих устройств. С помощь логического моделирования решаются следующие задачи:

- проверка правильности логического функционирования ДУ,

- проверка временных характеристик цифрового устройства,

- анализ состязания сигналов,

- построение проверяющих тестов,

- проверка полноты проверяющего теста относительно определенного класса неисправностей,

- получение и сокращение диагностической информации для поиска неисправностей цифрового устройства.

В зависимости от требований, предъявляемых практикой, применяются различные методы моделирования ДУ и способы их реализации. Выбор из множества методов и алгоритмов моделирования осуществляется по критериям, основными из которых являются: адекватность и быстродействие. Под адекватностью понимается степень соответствия результатов моделирования реальному поведению рассматриваемого цифрового устройства. Моделирование цифрового устройства можно разделить на задачи статического и динамического анализа. Основой статического анализа является синхронное моделирование, при котором задержки распространения безинерционных элементов равны такту синхронизации устройства.

Под тактом понимается временной промежуток, на котором состояния внешних полюсов устройства не изменяется. Синхронное моделирование позволяет верифицировать логику работы схем.

Для большинства практически важных задач достаточно правильно вычислять установившиеся значения сигналов. Для комбинационных устройств, применяемые алгоритмы моделирования дают полную и точную информацию об установившихся значениях сигналов. Неопределенность начального состояния и возможность состязаний между сигналами в последовательностных схемах существенно усложняют их моделирование.

Адекватность моделирования последовательностных устройств зависит от выбранного метода моделирования, т.е. от принятой модели устройства, моделей элементов и сигналов, учета временных задержек между сигналами. В реальности изменения сигналов на линиях устройства происходят не одновременно, а его логические элементы инерционны, т.е. могут не реагировать на сигналы, длительность которых меньше некоторой граничной величины, характерной для него. Таким образом, изменяя задержки распространения и инерционные задержки для неизменной логической схемы, мы можем получить различные значения сигналов на линиях устройства в рассматриваемые моменты времени.

Большое распространение получили интегральные микросхемы на основе полевых транзисторов структуры металл - окисел - полупроводник (МОП транзисторы). Принципиальные особенности транзисторов этого типа позволяют создавать элементы и целые узлы цифровых устройств с малым потреблением энергии при высокой помехоустойчивости и нагрузочной способности. Сравнительно с биполярными транзисторами они имеют меньшие размеры, что позволяет разместить на единице площади кристалла большее число элементов при более простой технологии. Поэтому МОП транзисторы широко применяются в качестве основных элементов всех современных интегральных микросхем КМОП структуры.

Цифровые устройства, создаваемые по МОП и КМОП технологиям, имеют особенности своего функционирования, которые трудно моделировать при их представлении моделями вентильного уровня. Если с двунаправленностью сигналов при моделировании исправных устройств можно достаточно легко справиться, то моделирование неисправностей ясно показывает недостаточность традиционного вентильного подхода [1-3]. С другой стороны программы аналогового моделирования, способные моделировать все типы МОП-схем на электрическом уровне, требуют большого объема вычислений уже для интегральных микросхем средней степени интеграции. Поэтому с целью адекватности отображения неисправностей переходят на переключательный уровень.

Так как известно, что моделирование неисправностей устройств, изготовленных по МОП-технологиям, при использовании моделей этих устройств, на вентильном уровне имеет значительные трудности [4-7]. Анализ причин дефектов схем, выполненных по МОП-технологии, показывает, что большая их часть может моделироваться неисправностями типа "устойчивый обрыв транзистора" ( SOP ) и "устойчивое замыкание транзистора" ( SON ). Первые переводят схему из класса комбинационных в класс последовательностных, вторые обуславливают выходные неустойчивые сигналы. В обзоре [4] указывается, что процент реальных физических дефектов, которые покрываются этими модельными неисправностями, не менее 75%. Имеются данные, что тесты, построенные для обнаружения константных неисправностей, не проверяют около 10-15% реальных дефектов МОП-стуктур. Переключательные модели являются наиболее известным способом учета особенностей МОП-технологий. Они позволяют ввести единый способ моделирования основных типов неисправностей. Переключательные модели описывают поведение схемы, используя при этом такие основные электронные компоненты, как p-МОП-транзистор, n-МОП-транзистор, нагрузочный транзистор, проводник, логический конденсатор или емкость.

Переход на переключательный уровень

Необходимо отметить, что так как вентильное представление является базовым на этапе логического моделирования, неотьемлемой частью систем моделирования на переключательном уровне является программа экспандера (расширителя), которая осуществляет переход от вентильного представления устройства к его переключательной модели. Основные вентильные примитивы, т.е. элементы инвертора, n-входовые элементы ИЛИ-НЕ (n не больше 8) и т.п., имеют конкретные реализации при различных вариантах их производства по МОП-технологиям. Эти реализации составляют библиотеку, используемую при моделировании неисправностей на переключательном уровне в системе ИКСМ [8].

Моделирование исправного устройства

Параллельное моделирование исправного устройства, которое позволяет успешно использовать методологию [9], изложено в работах [5-7]. В этих работах процесс моделирования представлен итерационным решением системы псевдобулевых уравнений вида  , где

, где  -значение многозначного узла в схеме в n-итерации. Считаем, что M - операция выбора максимального значения из значений сигналов разветвлений узла, F-система булевых уравнений, вид которых зависит от алфавита моделирования и базовых компонентов, составляющих устройство,

-значение многозначного узла в схеме в n-итерации. Считаем, что M - операция выбора максимального значения из значений сигналов разветвлений узла, F-система булевых уравнений, вид которых зависит от алфавита моделирования и базовых компонентов, составляющих устройство,  -операция суперпозиции. Значение X есть двойка (G, H) , где

-операция суперпозиции. Значение X есть двойка (G, H) , где  - соответственно значения логического состояния сигнала и его логической силы, которые можно интерпретировать, как напряжение и сила тока. Упорядочение сигналов, необходимое для выполнения операции M, представлено на решетке сигналов на рис.1 [10].

- соответственно значения логического состояния сигнала и его логической силы, которые можно интерпретировать, как напряжение и сила тока. Упорядочение сигналов, необходимое для выполнения операции M, представлено на решетке сигналов на рис.1 [10].

Рисунок 1 - Решетка сигналов

Приведенные системы булевых уравнений позволяют использовать параллельные вычисления при их решении самым широким образом, так как являются идеальными объектами для этого.

Преобразования МОП-структур

В статье [11] описываются преобразования структур данных для исправной МОП-схемы, благодаря которым моделирование основных неисправностей МОП-схем, соответствующих конкретным физическим дефектам при их изготовлении, сводится к моделированию ассоциированного исправного устройства.

На рис. 2 представлены транзисторы, добавляемые в исправную МОП-схему для моделирования неисправностей различных типов [9]. Их затворы являются дополнительными внешними входами устройства, определяющими наличие или активность конкретной неисправности. Структуру МОП-схемы определяют массивы Q1, Q2, Q3, T, которые описывают для каждого транзистора его сток, затвор, исток и тип соответственно. Поэтому для моделирования этих неисправностей необходимо модифицировать определенным образом для каждого вида неисправности массивы Q1, Q2, Q3, T.

Эта модификация производится в два шага. Первый шаг состоит в добавлении в массивы Q1, Q2, Q3, T информации о новом внешнем входе устройства, соответствующем управляющему входу неисправности (затвору дополнительного транзистора). Этот шаг является общим для всех типов неисправностей. Второй шаг является специфическим для каждого типа неисправности.

Процедура добавления внешнего входа (выхода) в МОП-схему

Считаем, что размерность массивов Q1, Q2, Q3, T равна N. При добавлении нового внешнего вывода во внутренний узел устройства n необходимо:

а) если новый вывод является выходом, то добавить в конец массивов Q1, Q2, Q3, T по два элемента: в Q1 - число N+1, N+1, в Q2 - 1, 2, в Q3 - N+1, n;

б) если новый вывод является входом, то добавить в конец Q1 - N+1, в Q2 - число 2, в Q3 -N+1; добавить элемент в зону узла n: в Q1 - n, в Q2 - 2, в Q3 - N+1.

Рисунок 2 - Добавочные транзисторы для моделирования

а)0-неисправности;

б) 1-неисправности;

в) обрыва транзистора;

г) замыкания сток-исток;

д) замыкания линий;

е) разрыва линии.

Инжекция константных неисправностей  в узел схемы с номером n.

в узел схемы с номером n.

1. Выполнить процедуру добавления нового внешнего входа.

2. Вставить в массивы Q1, Q2, Q3, T справа или слева для любого элемента с номером, таким что Q1[k]=n, следующие данные: в Q1 - вставляем число n, в Q2 - число 2, в Q3 - 1(2) в соответствии с неисправностью  или

или  .

.

Инжекция неисправности короткого замыкания исток-сток транзистора

Считаем, что исток и сток рассматриваемого транзистора имеют соответственно номера n и m.

1. Выполнить процедуру добавления нового внешнего входа.

2. Вставить в массивы Q1, Q2, Q3, T справа и слева для любого элемента с номером k, таким что Q1[k]=n(m) , следующие данные:

а) в Q1 вставляем n(m) ;

б) в Q2 вставляем N+1(N+1) ;

в) в Q3 вставляем m(n) ;

г) в T1 и T2 - 1(1).

Инжекция неисправности обрыва транзистора в узле n.

1.Выполнить процедуру добавления нового внешнего входа.

2.Заменить в массивах Q1, Q2, Q3, T для элементов с номером k, таким, что Q2(k)=t, Q1[k]=n значения Q1[k]=n, Q2[k]=N+1, Q3[k]=N+2.

3.Добавить в конец Q1 - N+2, в конец Q2 - t, в Q3 - l.

Исходный и конечный вид узла представлен на рис. 3.

Рисунок 3 - Обрыв транзистора в узле n.

Инжекция неисправности замыкания линий n и m

1.Выполнить процедуру добавления нового внешнего входа.

2.Добавить в Q1, Q2, Q3, T справа или слева для любого элемента с номером k, такого что Q1[k]=n(m) соответственно в Q1 - n(m) , в Q2 - N+1(N+1) , в Q3 - m(n) в T1 и T2 (1).

Исходный и конечный вид узла представлен на рис.4.

Рисунок 4 - Замыкание линий n, m.

Инжекция неисправности обрыва линии n

Для внутренних узлов инжекция неисправности сводится к процедуре 3, т.е. к инжекции обрыва транзистора в узле n.

На данный момент написана программа моделирования описанных выше неисправностей МОП-структур. Тестирование программы показало, что с ее помощью можно моделировать неисправности СБИС разной степени интеграции, в том числе и некоторых типов СБИС, которые не могли моделировать с помощью написанных ранее алгоритмов и тестов.

Дальнейшие исследования будут направлены улучшения алгоритма моделирования и расширение его возможностей в области тестирования различных СБИС.

Параметрическое моделирование

Быстрый рост рабочей частоты цифровых систем, стал причиной того, что главной задачей проектирования и тестирования, стало обеспечение целостности сигналов.

Паразитные емкости и индуктивности, и их воздействие на соединения в МОП СБИС, сейчас играют основную роль в правильности функционирования и производительности БИС.

Под целостностью сигнала, будем понимать способность сигнала генерировать правильные ответы на схеме. Согласно этим замечаниям, сигнал с хорошей целостностью имеет:

- значение напряжения в требуемых границах;

- выполняет все переходы за требуемый промежуток времени.

Основными проблемами целостности сигналов являются:

- ослабление сигнала, вследствие эффекта взаимодействия между сигналами ;

- чрезвычайно быстрое возрастание напряжения сигнала;

- изменение источника напряжения ;

- срыв сигнала, вследствие различных задержек достижения сигналом различных приемников.

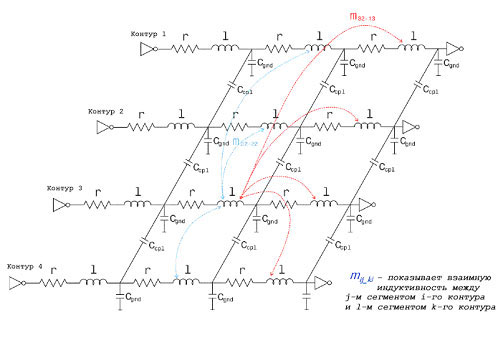

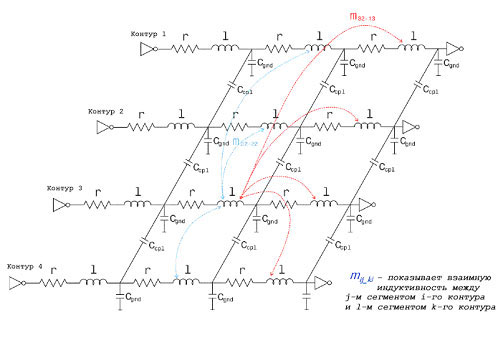

Существует несколько направлений поиска решений этих проблем при проектировании и изготовлении, диагностировании СБИС, среди которых выделяется достаточно точное для практики моделирование СБИС при представлении ее распределенной RLC-моделью. Общий вид такой модели представлен на рис. 5.

В докладе [12] рассматривается влияние индуктивного взаимодействия сигналов на линии СБИС.

Рисунок 5 - Общий вид RLC модели.

Простейшей моделью моделирования взаимного индуктивного взаимодействия соединений в СБИС является модификация известной модели двух связанных колебательных контуров [13]. В работе [12], рассмотрены три таких контура и взаимодействие между этими контурами, которое представлено системой трех дифференциальных уравнений. Решая эту систему и манипулируя некоторыми параметрами, в графическом виде были получены результаты, которые позволяют выполнять первичную оценку силы влияния индуктивного взаимодействия на робастность сигналов на линиях МОП СБИС.

Планируемые дальнейшие исследования будут направлены на моделирование взаимного индуктивного взаимодействия более трех RLC-контуров.

Литература

1. Киносита К., Асада К., Карацу К. Логическое проектирование СБИС / Пер. с япон. М.: Мир, 1988. 309 с.

2. Randel E. Bryant. A switch Level Model and Simulator for MOS Digital Systems // IEEE Trans. On Comp. 1984. V. 33. № 2. P. 160 - 177.

3. Хейс Дж. П. Обобщенная теория переключательных схем и ее применение для проектирования СБИС // Тр. Ин-та инж. по электротехнике и радиоэлектронике. 1982. Т. 70. № 10. 5 - 19.

4. Вейцман И.Н., Кондратьева О. М. Тестирование КМОП-схем //Автоматика и телемеханика. -1991.- N 2. - С.3-34.

5. Андрюхин А.И. Алгоритмы параллельного логического моделирования и псевдослучайной генерации тестов для МОП-структур // Микроэлектроника. -1995.- N 5. - С. 331-336.

6. Андрюхин А.И. Параллельное логическое моделирование МОП-структур на переключательном уровне. // Электронное моделирование. - 1996. - N 2. - С. 88-92.

7. Андрюхин А.И. Параллельное многозначное логическое моделирование исправных и неисправных псевдобулевых схем. // Электронное моделирование -1997. - N 1. - С. 58-63.

8. Андрюхин А.И. Сперанский Д.В. Иерархическая компилятивная система моделирования и генерации тестов // Техническая диагностика и неразрушающий контроль. -1994. - N 2. - С. 71-78.

9. VLSI Testing/Ed. by Williams T.W. Elsevier Science Publishers, B.V.,1986-275 p.

10. Андрюхин А.И., Терещук Д.С.Логический учет динамики в МОП-структурах

11. Андрюхин А.И. Параллельное моделирование неисправностей МОП-структур// УДК 681.326

12. Андрюхин А. И., Клименко И. В. Исследование взаимодействия соединений в СБИС//Информатика и компьютерные технологии 2005 - 15.12.2005

13. Новиков Ю.Н. Электротехника и электроника. Теория цепей и сигналов, методы анализа.

При написании данного автореферата, магистерская работа еще не завершена. Окончательное завершение: январь 2007 года. Полный текст работы и все материалы по теме могут быть получены у автора или его руководителя после указанной даты.

Версия для печати

Версия для печати

Клименко Иван Владимирович

Клименко Иван Владимирович

, где

, где  -значение многозначного узла в схеме в n-итерации. Считаем, что M - операция выбора максимального значения из значений сигналов разветвлений узла, F-система булевых уравнений, вид которых зависит от алфавита моделирования и базовых компонентов, составляющих устройство,

-значение многозначного узла в схеме в n-итерации. Считаем, что M - операция выбора максимального значения из значений сигналов разветвлений узла, F-система булевых уравнений, вид которых зависит от алфавита моделирования и базовых компонентов, составляющих устройство,  -операция суперпозиции. Значение X есть двойка (G, H) , где

-операция суперпозиции. Значение X есть двойка (G, H) , где  - соответственно значения логического состояния сигнала и его логической силы, которые можно интерпретировать, как напряжение и сила тока. Упорядочение сигналов, необходимое для выполнения операции M, представлено на решетке сигналов на рис.1 [10].

- соответственно значения логического состояния сигнала и его логической силы, которые можно интерпретировать, как напряжение и сила тока. Упорядочение сигналов, необходимое для выполнения операции M, представлено на решетке сигналов на рис.1 [10].

в узел схемы с номером n.

в узел схемы с номером n.

или

или  .

.