На конкурс на лучшую научную работу

студентов по разделу

«техническая кибернетика, вычислительная,

микропроцессорная техника и информатика»

СТУДЕНЧЕСКАЯ НАУЧНАЯ РАБОТА

на тему: «Моделирование аналогово-цифровых устройств»

ДЕВИЗ: VHDL-AMS

2006 г .

СВЕДЕНИЯ

об авторе и научном руководителе научно-исследовательской работы

на тему:

МОДЕЛИРОВАНИЕ АНАЛОГОВО-ЦИФРОВЫХ УСТРОЙСТВ

направляемой на проводимый в 2006 году _________________конкурс на лучшую студенческую работу по естественным, техническим, гуманитарным и общественным наукам.

1. Фамилия: Нестеренко

2. Имя : Денис

3. Отчество: Олегович

4. Высшее учебное заведение, в котором обучается автор: Донецкий национальный технический университет (ДонНТУ)

5. Факультет: Вычислительной техники и информатики (ВТИ)

6. Направление: 6.0915 «Компьютерная инженерия»

Специальность: 7.091501 «Компьютерные системы и сети»

7. Курс, группа: 5, КС-06маг

8. Домашний адрес:

9. Гражданство: Украина

НАУЧНЫЙ РУКОВОДИТЕЛЬ

1. Фамилия: Зинченко

2. Имя: Юрий

3. Отчество: Евгеньевич

4. Кафедра, должность: кафедра ЭВМ, доцент

5. Учёная степень: кандидат технических наук

6. Учёное звание: доцент

7. Домашний адрес:

ОТЗЫВ

руководителя на студенческую работу

на тему: «МОДЕЛИРОВАНИЕ АНАЛОГОВО-ЦИФРОВЫХ УСТРОЙСТВ»

Работа автора посвящена исследованию проблемы моделирования аналогово-цифровых устройств. Данная тема является актуальной ввиду необходимости проектирования, отладки и тестирования таких схем.

Объектом разработки данной работы является исследование инструментальной среды, а также разработка алгоритмов моделирования аналогово-цифровых схем на примере реализации аналогово-цифровых узлов системы цифровой обработки данных.

Аппаратным средством исследований является персональная ЭВМ ( IBM PC ).

Программной средой для разработки является САПР OrCAD .

Положительными сторонами данной работы является её новизна в условиях развития современной техники, а также слабая исследованность данной области.

Работа может быть использована при дальнейшем исследовании данной области, а также при проектировании поста контроля для поиска неисправностей аналоговых и аналогово-цифровых схем.

Руководитель ____________ Зинченко Ю.Е.

РЕФЕРАТ

стр. 21, рис. 14, прил. 3.

Объектом исследования данной работы является способ описания и моделирования схем, построенных по смешанной технологии (аналогово-цифровые схемы). Цель данной работы – построение моделей узлов системы цифровой обработки данных и их исследование. Поставленная цель реализуется средствами языка описания аппаратуры VHDL - AMS .

Результатом выполнения работы является исследование способов моделирования смешанных схем на примере реализации конкретных узлов радиоуправляемой аналогово-цифровой системы. Результаты данной работы в дальнейшем могут быть применены при моделировании и диагностике аналого-цифровых схем.

АНАЛОГОВО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, ШИРОТНО-ИМПУЛЬСНАЯ МОДУЛЯЦИЯ, РАЗРЕШАЮЩАЯ СПОСОБНОСТЬ, МУЛЬТИПЛЕКСНАЯ ПЕРЕДАЧА.

Содержание.

Введение.

Современный мир немыслим без цифровой техники. Она окружает на работе, в быту, в поездках, словом, повсюду. С её помощью мы решаем задачи хранения, обработки и передачи информации. Однако следует заметить, что существование цифровой техники невозможно без аналоговой части. Весь мир, окружающий нас имеет непрерывную аналоговую природу, непонятную машине. Следовательно, необходимостью является создание устройств смешанной технологии, служащих для преобразования различного вида данных. Как правило, это устройства, выполняющие оцифровку аналоговых данных, а также исполнительные механизмы.

С появлением новых систем проектирования и моделирования аналогово-цифровой техники мы получили возможность создавать принципиально новые устройства, отличающиеся своей надежностью, быстродействием, точностью работы. Одной из таких систем является САПР на основе языка описания аппаратуры аналоговых, аналогово-цифровых схем, а также устройств смешанной технологии (электронно-мехенические устройства) VHDL - AMS . В данной работе речь пойдет о концепции данной технологии на примере рассмотрения модели системы цифровой обработки сигналов.

2. Моделирование аналогово-цифровых схем.

Язык описания аппаратуры VHDL - AMS является языком высокого уровня, что позволяет ему абстрагироваться от конкретных параметров и физических законов разрабатываемых систем. Схему устройства (будь-то цифровое, аналоговое или даже механическое) можно представить в виде математической модели. При этом в саму модель необходимо заложить требуемые реальные параметры и законы их изменения.

В данной работе будут рассмотрены принципы моделирования смешанных аналогово-цифровых схем на примере радиоуправляемой системы самолета. Задача данной системы состоит в следующем:

– сбор данных от аналоговых органов управления;

– оцифровка полученных сигналов;

– передача сигналов на исполнительные механизмы;

– прием данных и их декодирование;

– преобразование сигналов в аналоговую форму и их выдача на исполнительные механизмы.

Общая схема движения сигналов в системе изображена на рис.1.

Рис. 1 – Схема движения сигналов в системе

Система управления состоит из 4-х секций: блок аналогового контроля (Control Stick); блок оцифровки и кодирования (digitize/encode block); блок декодирования и выработки широтно-импульсных сигналов (the decode/PW block); конвертер широтно-импульсных сигналов в аналоговые (the PW/analog blocks).

Скорость и направление полета самолета контролируются акселератором и штурвалом. На выходе этих устройств – непрерывные аналоговые сигналы в диапазоне от 0В до 4.8В. Аналоговые электрические сигналы поступают в блок кодера, где происходит их оцифровка. Рассмотрим принцип работы блока.

Основное назначение блока оцифровки/кодирования заключается в измерении аналоговых сигналов от обоих органов управления каждые 20 мс и их преобразовании в 10-битовые последовательные строки. В коммуникационных системах процесс оцифровки аналоговых сигналов и их форматирования для передачи осуществляется по принципу кодово-импульсной модуляции (PCM). Этот блок также выполняет мультиплексирование каждого потока данных по принципу мультиплексной передачи с временным разделением (TDM). Результатом этих операций является битовый поток, состоящий из данных, пересылаемых приемнику.

Данные в битовом потоке представляют собой совокупность пакетов, длительность каждого из них составляет 20 мс. Каждый пакет может содержать до 8 каналов, длительностью 2 мс каждый. Информация о синхронизации кадра и обнаружении ошибок также кодируется в битовый поток, более приоритетный для передачи. Аналогово-цифровое преобразование, сборка битового потока и общая синхронизация контролируются локально.

Выходной битовый поток кодера посылается на вход декодирующего устройства. В реальной системе этот сигнал передается посредством блоков RF-передатчика и RF-приемника. Частота передачи сигнала лежит в пределах 6000-7000 бит/с. Минимально допустимая частота для этой системы составляет:

(8 каналов) х (16 бит/канал) / (20 мс длительность пакета) = 6400 бит/с.

Полезная для системы информация заключена в первых 3-х каналах кадра (синхронизация, состояние органов управления); остальные каналы не используются. Каждый канал содержит 16 бит: 10 бит данных, 1 стартовый бит и 1 бит паритета. Дополнительные 4 бита добавлены к каждому каналу в качестве промежутка при рассмотрении временных диаграмм.

Пример битового потока с выхода кодера изображен на рис.2. Канал синхронизации состоит из 12 перемежающихся бит. Эта информация ипользуется декодером для оценки истинности принятых данных. Данные от акселератора и рулей направлений посылаются раздельно в каналах 1 и 2.

Рис. 2 – Последовательный битовый поток данных

Схема кодера, изображенная на рис.3, работает следующим образом: вначале 12-битовая синхро-последовательность генерируется в блоке TDM_кодера, состоящего из сдвигающего регистра-защелки. Дополнительные 4 нулевых бита также сдвигаются для заполнения 16-битного канала. Далее генерируются управляющие сигналы. Аналоговые сигналы от акселератора и рулей поступают на вход 2-х входового аналогового переключателя. Вначале переключатель пропускает сигнал от акселератора на вход аналогово-цифрового конвертера. Этот сигнал оцифровывается в 10-битную последовательность, которая поступает в TDM_кодер и кодируется в 16-битную последовательность данных канала. Далее аналоговый переключатель переводится в положение обработки сигнала рулей. Этот сигнал оцифровывается и кодируется таким же образом, как и предыдущий.

Рис. 3 – Схема кодера

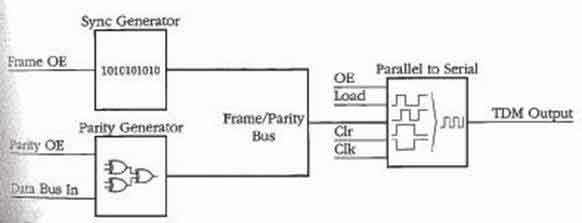

Схема TDM_кодера приведена на рис.4. Этот кодер к 10-битовому цифровому сигналу добавляет стартовый бит и бит паритета. Бит паритета позволяет обнаружить единичную ошибку между передатчиком и приемником в каждом канале. Если ошибка обнаружена в приемнике, канал не будет обновлен. Вместо этого приемник будет использовать данные предыдущего состояния органов управления. 12-битовая последовательность от генератора паритета защелкивается в параллельно-последовательном сдвиговом регистре, добавляющем еще 4 бита данных.

Рис. 4 – Схема TDM_кодера

2.2. Аналоговый переключатель

Модель 2-х входового аналогового переключателя приведена в приложении 1. Логический 0 на цифровом входе sw_state соответствует замкнутому состоянию контактов p_in1 и p_out (сопр. r_closed), и разомкнутому состоянию между контактами p_in2 и p_out (сопр. r_open). Сопротивление r_closed представлено очень маленьким значением, а r_open – очень большим. Это позволяет протекать току между контактами p_in1 и p_out и не протекать соответственно между контактами p_in2 и p_out. Противоположная ситуация возникает, когда на входе sw_state уровень логической единицы.

Процесс чувствителен к сигналу sw_state и присваивает значения r_open или r_closed сигналам r_sig1 и r_sig2, что представляет собой резистивный переключатель. Резисторы r1 и r2 в модели представлены с атрибутом ‘ramp. Это позволяет коммутировать ток и напряжение через переключатель согласно закону Ома.

2.3. Аналогово-цифровой конвертер.

Аналогово-цифровой конвертер (A/D) использует следующий алгоритм аппроксимации: конвертер выполняет операцию конвертирования за 2 шага:

– ввод (чтение аналоговых данных);

– конвертирование (измерение напряжения на входе и формирование цифрового эквивалента во временном битовом массиве и выдача результирующих данных на выход).

Работа конвертера начинается с первого шага – ввода данных по сигналу запуска start. Далее тестируется напряжение на входе конвертера Vin и инициализируются переменные, необходимые для выполнения операции конвертирования. Также сбрасывается флаг «конвертирование закончено», конвертер переводится в состояние готовности к конвертированию (шаг 2).

До начала 2-го шага конвертер ожидает фронт синхроимпульса, затем сравнивается измеренное значение входного напряжения с пороговой величиной для выделения старшего значащего бита. Если входное напряжение больше порогового значения, конвертер устанавливает старший бит логического вектора в 1 и уменьшает измеряемое напряжение на величину порогового напряжения. В противном случае конвертер заносит в старший бит вектора 0, не изменяя при этом входного напряжения. Эта операция повторяется для каждого из последующих бит. При выделении самого младшего бита вектора, конвертер устанавливает сигнал eoc в 1, что является признаком завершения операции конвертирования, после чего сформированный логический вектор выводится на выходную шину. После этого сбрасывается переменная состояния, что свидетельствует о готовности конвертера к выполнения нового цикла конвертирования.

2.4. Широтно-импульсный кодер/декодер.

Широтно-импульсный кодер (PW) декодирует входящий битовый поток данных и генерирует импульсные сигналы. Он принимает асинхронный TDM битовый поток от блока кодера через RF-блок приема-передачи. Данные из последовательного потока извлекаются и конвертируются в параллельный код, который представляет собой оцифрованные данные от органов управления. Слова параллельного кода наряду со значением цифрового счетчика используются для генерации аналогового сигнала пропорциональной длительности для каждого канала управления серво-приводами. Синхронизация, декодирование и генерирование широтно-импульсного сигнала контролируются управляющим автоматом.

С выхода кодера снимается аналоговые сигналы, управляющие определенными серво-приводами. Амплитуда сигналов равна 4.8 В. Импульсы сигнала обновляются каждые 20 мс (50 Гц), и занимают по длительности от 1 до 2 мс, в зависимости от воздействия на органы управления.

Сигнал ШИМ переменой длительности генерируется схемой, изображенной на рис.5. Эта схема принимает битовый поток, генерируемый в блоке кодера. Под управлением УА TDM-декодер делит битовый поток на каналы. Для каждого канала данные поступают на один из входов цифрового компаратора. На второй вход компаратора поступает значение счетчика. В момент, когда данные из битового потока защелкиваются в регистре компаратора, запускается счетчик, наращивающий свое значение. Выход компаратора находится в состоянии высокого уровня (ВУ). В момент, когда значение счетчика становится равным защелкнутому значению из канала, на выходе компаратора появляется низкий уровень (НУ). Ширина выходного сигнала компаратора пропорциональна времени счета счетчика.

Рис. 5 – Схема кодера сигналов ШИМ

Блок декодера сигналов ШИМ конвертирует широтно-импульсные сигналы, поступающие от блока ШИМ кодера в аналоговые сигналы, представленные уровнем напряжения для управления серво-приводами. Приходящие импульсы преобразуются в цифровой параллельный код (с использованием счетчиков), а затем трансформируются в эквивалентное ему напряжение с помощью ЦАП (D/A converter).

Это конвертирование осуществляется схемой, изображенной на рис.6. Сигнал ШИМ поступает на разрешающий вход счетчика, а также на вход его синхронизации. Выход счетчика поступает на цифро-аналоговый конвертер, с выхода которого снимается напряжение управления серво-приводами.

Рис. 6 – Схема декодера сигналов ШИМ

2.5. Цифро-аналоговый преобразователь

Почти все компоненты в блоке ШИМ являются цифровыми. Исключение составляет цифро-аналоговый преобразователь (ЦАП). VHDL-AMS модель данного блока приведена в приложении 3. Рассмотрим алгоритм его работы. Конвертер читает по одному биту последовательного кода, начиная с самого старшего разряда. Для каждого бита конвертер вычисляет соответствующее напряжение и добавляет его к значению v_sum; если бит=0 значение не добавляется. После прохода всех бит кода конвертер передает сигналу sum_out значение переменной v_sum. Далее происходит вычисление выходного напряжения vout с помощью атрибута ‘ramp сигнала sum_out. На этом шаге работа ЦАП завершена. Атрибут ‘ramp сигнализирует о завершении процесса преобразования.

В конечном итоге на выходе схемы мы получаем «оцифрованный» аналоговый сигнал управления серво-приводами, который обновляется каждые 20мс. Временная диаграмма этого сигнала приведена на рис. 7.

Рис. 7 – Аналоговый сигнал и его эквивалент после оцифровки

2.6. Анализ точности конвертирования

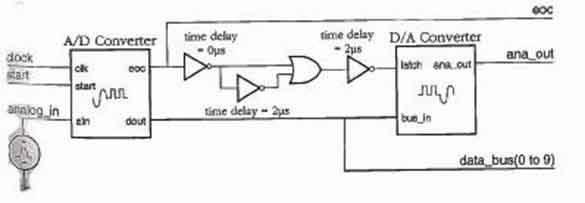

Прежде чем определить общую точность исследуемой системы, необходимо проанализировать тестовую схему, приведенную на рис.8, для ознакомления с принципами AD и DA конвертирования. В данной схеме источником пульсирующего аналогового сигнала является модель АЦП (приложение 2). По окончании конвертирования сигнал eoc устанавливается в верхний уровень. Этот сигнал трансформируется в короткий импульс, защелкивающий регистр схемы D/A. Как результат – аналоговый сигнал конвертируется в цифровой, а затем снова в аналоговый.

Рис. 8 – Тестовая схема для оценки точности AD и DA преобразований

Схема используется для исследования точности преобразования A/D и D/A компонентов. В качестве теста используется напряжение, изменяющееся от 0 В до 9.5 В течении 600 мс. Амплитуда 9.5В выбрана близкой к максимально возможной конвертируемой величине напряжения на конверторе (±4.8 В).

При первом проходе запускаем серию тестов для иллюстрации эффекта разрешающей способности (точность конвертирования). Рисунок 9 иллюстрирует квантованные выходные сигналы при разрешающей способности от 5 до 10 бит. Непрерывный сигнал – это аналоговый сигнал на входе, оцифрованный D/A сигнал состоит из 6 диаграмм для разных значений разрешающей способности. Эти сигналы налагаются друг на друга. Цифровой сигнал внизу отображает моменты начала A/D конвертирования.

Рис. 9 – Влияние разрешающей способности на точность конвертирования

Как видно из рисунка ошибка D/A преобразования возрастает при снижении разрешающей способности (квантованный сигнал не совпадает с исходным). Ошибку квантования легко увидеть на рис.10. Возьмем момент времени 285 мс. Он совпадает с восходящим фронтом сигнала запуска A/D конвертирования. Квантуемый аналоговый сигнал имеет амплитуду 4.49В. При этом D/A конвертер генерирует ошибку в 2.3мВ при 10-битном разрешении и 292мВ – при 5-битном. Максимальная ошибка при 10 битах составляет FSR/2 10, где FSR – максимально возможная амплитуда конвертируемого сигнала. Для нашего конвертера она составляет 9.6В, что дает ошибку квантования 9.6/1024=9.4мВ. Это приемлемый результат. Используя 5-битное квантование получим ошибку 9.6/32=300 мВ, что больше измеренного значения 292мВ.

Рис. 10 – Влияние разрешающей способности на точность конвертирования

Теперь мы знаем, чего можно ожидать от аналогово-цифровых и цифро-аналоговых конвертеров. Выберем 8-битное конвертирование. Из предыдущего анализа точности конвертирования можно подсчитать ошибку квантования: 9.6/256=37.5мВ. Будем использовать это значение для представления наибольшей разницы между входным аналоговым сигналом и его квантованным эквивалентом. Результат исследования для канала руля при 8 битах приведен на рис.11. На этом рисунке изображены 2 пары замеров. Левые вертикальные линии отображают моменты дискретизации входного сигнала, правые вертикальные линии показывают соответствующие им значения квантованного сигнала. Квантование выполнено с ошибкой 34.5мВ, что близко к максимальной ошибке. Это ожидаемая величина. Она указывает на предсказуемость системы в целом.

Рис. 11 – Сигнал канала руля и его 8-битный квантованный эквивалент

Предположим, что мы увеличили разрешающую способность до 10 бит для того, чтобы получить более «четкие» результаты преобразования. Результаты анализа приведены на рис.12. Из предыдущих расчетов мы ожидаем максимальной погрешности квантизации в 9.4мВ. Тем не менее, диаграмма выявляет ошибку. Входной сигнал квантуется при уровне 1.0095В, а результирующий квантованный сигнал составляет 0.9938В. Разница между ними – 15.7мВ, что больше подсчитанной величины. Необходимо выявить причину этой ошибки.

Рис. 12 – Сигнал канала руля и его 10-битный квантованный эквивалент

До сих пор мы ограничивались анализом точности конвертеров A/D и D/A. Тем не менее, еще одно преобразование данных мы проигнорировали: преобразование цифрового кода в сигнал широтно-импульсной модуляции. При этом использовались цифровой счетчик и компаратор. Ширина импульса измерялась в количестве циклов счетчика до равного результата. Зависимость между длинной импульса и тактовой частотой аналогична зависимости между напряжением и Разрешающей способностью: чем больше циклов синхроимпульса используется для получения сигнала ШИМ, тем больше точность. Так как мы используем длительности ШИМ в 1 мс и 8-битную систему, то должны ожидать цикл синхросигнала 1мс/256, что составляет 4мкс (частота 250 кГц). Для 10-битной системы период уменьшается соответственно до 1мс/1024, что примерно равно 1мкс (частота 1 МГц). Рассмотренная проблема возникла по причине применения 10-битного преобразования A/D и D/A и 8-битного широтно-импульсного преобразования.

Проведя исследования, получим диаграмму на рис.13. Полученная погрешность равна 6.4 мВ (входной сигнал = 1.0095 В, выходной = 1.0031 В). Это исследование указывает на взаимосвязанность интегрированных подсистем в единой системе.

Рис. 13 – Сигнал канала руля и его 10-битный квантованный эквивалент при 1мс широтно-импульсной модуляции

Рис. 14 – Аналоговый сигнал канала руля и его квантованный эквивалент

Заключение

Результатом выполнения данной работы является достижение её цели – изучение способов описания и моделирования схем, построенных по смешанной технологии. Как мы видим, новые и постоянно совершенствующиеся САПР дают разработчику всё больше и больше пространства для творчества. Эти современные средства позволяют описать целостную структуру схемы, построенной по смешанной технологии, т.е. содержащую аналоговые, цифровые и даже электромеханические части. Благодаря таким возможностям мы способны создавать новые устройства, сочетающие в себе быстроту и надежность цифровых узлов, и точность результатов аналоговой техники. Кроме того, в процессе разработки учитываются параметры реальных устройств, что делает систему незаменимой в работе с аналоговыми датчиками, исполнительными механизмами и другими устройствами ввода-вывода.

Список литературы.

Приложение 1.

Модель 2-х входового цифро-управляемого аналогового переключателя.

library ieee; use ieee.std_logic_l164.all;

library ieee_proposed; use ieee_proposed.electrical_systems.all;

entity switch_dig_2in is

port (sw_state : in std_ulogic; — цифровой управляющий вход

terminal p_in1, p_jn2, p_put: electrical); — аналоговый выход

end entity switch_dig_2in;

architecture ideal of switch_dig_2in is

constant r_open : resistance := 1.0e6; — сопротивление разрыва

constant r_c l osed : resistance := 0.001; — сопротивление замыкания

constant transjime : real := 0.00001; — время преобразования

signal r_sig1 : resistance := r_closed; — переменная сопротивления замыкания

signal r_sig2 : resistance := r__open; — переменная сопротивления разрыва

quantity v1 across 11 through p_in1 to p_out; — напряжение и ток от in1 к out

quantity v2 across i2 through p_in2 to p_out; — напряжение и ток от in2 к out

quantity r1 : resistance; — переменное сопротивление от in1 к out

quantity r2 : resistance; — переменное сопротивление от in 2 к out

begin

process (sw_state) is — процесс чувствителен к сигналу sw _ state

begin

if sw_state = '0' or sw_state = V then — sig1 разрыв , sig2 соединение

r_sig1 <= r_closed;

r_sig2 <= r_open;

elsif sw_state = '1' or sw_state = 'H' then — sig1 соед . , sig2 - разрыв

r_sig1 <= r_open;

r_sig2 <= r_closed;

end if;

end process;

r1 == r_sig1'ramp(trans_time, trans_time); — применить изменение сопротивления

r2 == r_sig2'ramp(trans_time, trans_time); — ...

v1 == r1 i1; — применить закон Ома ко входу in1

v2 == r2 i2; — применить закон Ома ко входу in 2

end architecture ideal;

Приложение 2.

Модель аналогово-цифрового конвертера.

library ieee; use ieee.std.logic_164.alll;

library ieee_proposed; use ieee_proposed.electrical_systems.all;

entity a2d_nbit is

port (signal start : in std_ulogic; — сигнал start

signal clk : in std_ulogic; — синхроимпульс

terminal ain : electrical; — входной аналоговый сигнал

signal eoc : out std_ulogic := '0'; — выход «конвертирование завершено»

signal dout: out std_ulogic_vector(9 downto 0));— выходной цифровой сигнал

end entity a2d_nbit;

architecture sar of a2d_nbit is

constant Vmax : real := 5.0; — максимальное напряжение на АЦП

constant delay : time := 10 us; — время конвертирования

type states is (input, convert); — 2 шага конвертирования

constant bit_range : integer := 9; — битовый массив для dtmp и dout

quantity Vin across lin through ain to electrical_ref; — вход АЦП

begin

sa_adc: process is

variable thresh : real := Vmax; — величина пороговое напряжение

variable Vtmp : real := Vin; — значение вх. сигнала при конвертировании

variable dtmp : std_ulogic_vector(bit_range downto 0); — временный данные

variable status : states := input; — состояние « ввод »

variable bit_cnt: integer := bit_range;

begin

case status is

when input => — считать напряжение на входе по сигналу start (шаг 1)

wait on start until start = '1' or start = 'H';

bit_cnt := biWange; — сброс счетчика bit_cnt

thresh := Vmax;

Vtmp := Vin; — переменная со значением вх. напряжения

eoc <= '0'; — сброс состояния АЦП

status := convert; — перейти в состояние конвертирования (шаг 2)

when convert => — начать аппроксимацию входных данных

wait on clk until clk = '1' or clk = 'H1;

thresh := thresh / 2.0; — величина порогового напряжения

if Vtmp > thresh then

dtmp(bit_cnt) := 'V; — записать 'V в dtmp

Vtmp := Vtmp - thresh; — подготовка к след. сравнению

else

dtmp(bit_cnt) := '0'; — записать 'V в dtmp

end if;

if bit_cnt > 0 then

bit_cnt := bit_cnt - 1; — уменьшить счетчик бит

else

dout <= dtmp; — вывод dtmp на выход

eoc <= '1' after delay; — сигнал конца конвертирования

status := input; — перейти к состоянию ввода данных

end if;

end case;

end process sa_adc;

lin == 0.0; — идеальный вход (ток не течет)

end architecture sar;

Приложение 3. Модель цифро-аналогового преобразователя.

library ieee; use ieee.stdjogic_1164.all;

library ieee_proposed; use ieee_proposed.electrical_systems.all;

entity dac_10_bit is

port (signal bus_in : in std_ulogic_vector(9 downto 0); - входные данные

signal clk : in std_ulogic; - синхроимпульс

terminal analog_out: electrical); - аналоговый выход

end entity dac_10_bit;

architecture behavioral of dac_10_bit is

constant v_max : real := 5.0; - максимальное значение напряжения

signal s_out: real := 0.0; - переменная выходного сигнала

quantity v_out across i_out through analog_out to electrical_ref; - аналоговый выход

begin

convert: process is

variable v_sum : real; - суммируемое значение напряжения

variable delta_v: real; - временное значение напряжения

begin

wait until clk'event and (elk = '1' or clk = 'H');

v_sum := 0.0; - обнулить сумму

delta_v := v_max;

for i in bus_in'range loop

delta_v := delta_v / 2.0; - вес разряда

if bus_in(i) = '1' or bus_in(i) = 'H' then

v_sum := v_sum + delta_v; - бит =1 прибавляем вес разряда

end if;

end loop;

s_out <= v_sum; - записать преобразованное знеачение

end process convert;

v_out == s_out'ramp(100.0E-9); - выдать напряжение на выход ЦАП

end architecture behavioral;