Тезисы доклада на конференции "Компьютерный мониторинг и информационные технологии”, ДонНТУ, 2007

СИСТЕМА АВТОМАТИЗИРОВАННОГО СИНТЕЗА УПРАВЛЯЮЩИХ АВТОМАТОВ С ЖЕСТКОЙ ЛОГИКОЙ

Якубовский А.В., Красичков А.А.

Донецкий национальный технический университет

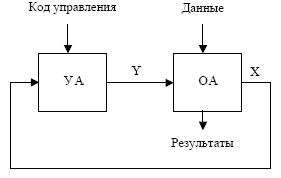

Современные цифровые устройства состоит из операционного автомата (ОА) и управляющего автомата (УА). Операционный автомат служит для выполнения заданных операций, а управляющий автомат требуется для стыковки, взаимодействия всех составных блоков устройства [1], изображение типового цифрового устройства на рисунок 1.

Рисунок 1 – Структурная схема цифрового устройства.

В настоящее время для реализации схем управляющих автоматов используются различные программируемые логические устройства. В связи с высокой сложностью современных цифровых устройств, увеличение аппаратных затрат на реализацию функциональности автомата становятся все большей проблемой, для реализации требуются программируемые логические устройства большой сложности и стоимости. В связи с этим, задача проектирования управляющего (конечного) автомата, сводится к оптимизации его структуры по таким параметрам как: скорость реакции на входной сигнал, аппаратные затраты. Методы реализации управляющих автоматов на цифровых устройствах, в научном мира, уделяется большое внимание, разрабатываются множество методов реализации управляющих автоматов с учетом требований оптимизации по аппаратным затратам и/или быстродействию [1].

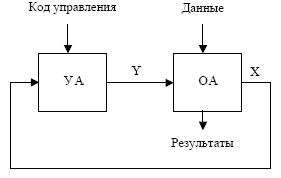

Рисунок 2 – Общая структура программы.

Принцип работа системы: проектировщик (User), формирует текстовый файл (File.gsa) который содержит в себе таблицу переходов (ГСА), данные из этого файла используются программой (САПР) для преобразования и минимизации. Проанализировав и преобразовав полученную информацию, программа на выходе формирует файл (File.vhdl) формата HDL содержащий уже готовый синтезированный управляющий автомат, который можно в дальнейшем использовать в других средах.| ЛИТЕРАТУРА |