# ОПТИМИЗАЦИЯ СХЕМЫ КОМПОЗИЦИОННОГО МИКРОПРОГРАММНОГО УСТРОЙСТВА УПРАВЛЕНИЯ С РАЗДЕЛЕНИЕМ КОДОВ

## А.А. Баркалов, Р.В.Мальчева, А.А.Красичков, Халед Баракат

Зеленогурский университет (Польша),

Донецкий национальный технический университет

A.Barkalov@iie.uz.zgora.pl

#### Аннотация

Предлагается метод синтеза КМУУ с разделением кодов, позволяющий сохранить минимальную емкость управляющей памяти при произвольных характеристиках реализуемого алгоритма управления. Также приведен пример применения предлагаемого метода.

#### 1. Постановка задачи и цели исследования

Устройство управления (УУ) любой цифровой системы может быть реализовано в виде композиционного микропрограммного устройства управления (КМУУ) [1,2]. В настоящее время для реализации схем устройств управления широко используются программируемые логические устройства типа CPLD и FPGA [3,4]. При этом традиционно актуальной является задача оптимизации аппаратных затрат в схеме устройства управления [4,5]. В случае применения CPLD или FPGA эта задача может решаться путем уменьшения числа термов в системе функций, реализуемых УУ [6]. Одним из методов решения этой задачи в случае КМУУ является метод разделения кодов [2]. Однако этот метод применим только при выполнении определенных условий, нарушении которых ведет к резкому увеличению емкости управляющей памяти КМУУ [2]. В настоящей работе предлагается метод синтеза КМУУ с разделением кодов, позволяющий сохранить минимальную емкость управляющей памяти при произвольных характеристиках реализуемого алгоритма управления.

#### 2. Основные определения и общая постановка задачи

Пусть алгоритм управления цифровой системы представлен в виде граф-схемы алгоритма ( $\Gamma$ CA)  $\Gamma$  [2] с начальной вершиной  $b_0$ , конечной вершиной  $b_E$ , операционными вершинами из множества  $B_1$  и условными вершинами из множества  $B_2$ . Вершины  $\Gamma$ CA  $\Gamma$  образуют множество  $B = B_1 \cup B_2 \cup \{b_0, b_E\}$ , связанных дугами  $\langle b_1, b_2 \rangle$ , образующими множество дуг E. Введем ряд определений, используя результаты работы [1].

Определение 1. Операторной линейной цепью (ОЛЦ) ГСА  $\Gamma$  называется конечная последовательность операторных вершин  $\alpha_g = \langle b_{g1}, ..., b_{gF_g} \rangle$ , такая, что существует дуга  $\langle b_{gi}, b_{gi+1} \rangle \in E$  для каждой пары соседних компонент вектора  $\alpha$  (i=1, ...,  $F_{g}$ -1).

Определение 2. Операторная вершина  $b_q \in D^g$ , где  $D^g$  – множество вершин, входящих в ОЛЦ  $\alpha_g$ , называется входом ОЛЦ  $\alpha_g$ , если существует дуга  $< b_t, b_q > \in E$ , такая, что  $b_t = b_0$  или  $b_t \in B_2$  или  $b_t \notin D^g$ .

Определение 3. Операторная вершина  $b_q \in D^g$  называется выходом ОЛЦ  $\alpha_g$ , если существует дуга  $\langle b_t, b_q \rangle \in E$ , такая, что  $b_t = b_E$  или  $b_t \in B_2$  или  $b_t \notin D^g$ .

Пусть для ГСА  $\Gamma$  сформировано множество ОЛЦ  $C = \{\alpha_1, ..., \alpha_G\}$ , удовлетворяющее условию

$$D^{i} \cap D^{j} = 0 \ (i \neq j; i, j \in \{1, ..., G\});$$

$$D^{1} \cup D^{2} \cup ... \cup D^{G} = B_{1};$$

$$G \Rightarrow \min.$$

$$(1)$$

При выполнении условия (1) каждая операторная вершина исходной ГСА входит ровно в одну ОЛЦ  $\alpha_g$   $\in$  С. Пусть каждой вершине  $b_q$   $\in$   $B_1$  соответствует двоичный код  $A(b_q)$  и для компонент любой ОЛЦ  $\alpha_g$   $\in$  С выполняется условие

$$A(b_{g_{i+1}}) = A(b_{g_i}) + 1$$

$$(i = \overline{1, F_g - 1}; g = \overline{1, G}).$$

(2)

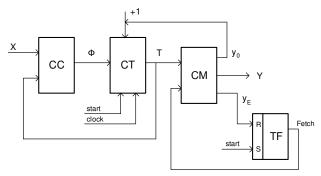

В этом случае для интерпретации ГСА  $\Gamma$  может быть использовано КМУУ  $U_1$  (рис.1), называемое КМУУ с общей памятью [2].

Рис. 1. Структурная схема КМУУ с общей памятью

Здесь комбинационная схема СС формирует систему функций возбуждения счетчика СТ

$$\Phi = \Phi(X, T), \tag{3}$$

где  $X = \{x_1, ..., x_L\}$  – множество логических условий, записанных в условных вершинах  $\Gamma$ CA  $\Gamma$ ,  $T = \{T_1, ..., T_R\}$  – множество внутренних переменных, используемых для адресации микрокоманд, хранящихся в управляющей памяти CM,

$$R = \log_2 M \left[, \tag{4}\right]$$

где  $M = |B_1|$ . Система (3) формирует адрес  $A(I_g^j)$  ј-го входа ОЛЦ  $\alpha_g \in C$ . Управляющая память CM содержит микрооперации  $y_n \in Y$ , где  $Y = \{y_1, ..., y_N\}$  — множество микроопераций, записанных в операторных вершинах ГСА  $\Gamma$ . Сигнал  $y_0$  используется для управления счетчиком CT: если  $y_0 = 1$ , то выполняется операция CT:=CT+1; если  $y_0 = 0$ , то содержимое CT определяется функциями (3). Сигнал  $y_E$  используется для организации режима останова  $U_1$ .

Устройство управления  $U_1$  функционирует следующим образом. По сигналу start=1 в CT записывается адрес первой микрокоманды интерпретируемой микропрограммы. Одновременно триггер выборки TF устанавливается в единицу и сигнал Fetch=1 разрешает выборку микрокоманды из CM. Если в CT находится адрес  $A(b_q)$  микрокоманды  $Y(b_q)$  и  $b_q \neq O_g$ , где  $O_g -$  выход ОЛЦ  $\alpha_g \in C$ , то CM формирует соответствующие микрооперации и сигнал  $y_0$ . Таким образом происходят переходы между микрокомандами, соответствующими компонентам одной ОЛЦ. Если  $b_q = O_g$ , то  $y_0 = 0$  и адрес перехода формируется системой (3). При достижении микрокоманды  $Y(b_t)$ , такой, что существует дуга  $\langle b_t, b_E \rangle \in E$ , формируется сигнал  $y_E$ , тригтер TF обнуляется и выборка микрокоманд прекращается.

Устройство управления  $U_1$  является автоматом Мура, память которого реализована на счетчике. При этом содержимое СТ интерпретируется как код состояния, совпадающий с адресом выхода ОЛЦ. Если число  $R_1$  переменных, требуемых для кодирования ОЛЦ  $\alpha_g \in C$

$$R_1 = \lceil \log_2 G \rceil, \tag{5}$$

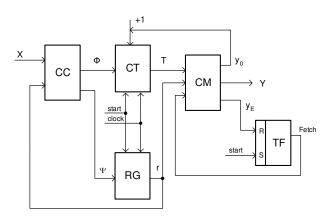

меньше R, то аппаратурные затраты в схеме CC можно уменьшить, применив метод разделения кодов [2], приводящий к  $KMYY\ U_2$  (puc.2).

Рис. 2. Структурная схема КМУУ с разделением кодов

Здесь адрес  $A(b_q)$  микрокоманды  $Y(b_q)$  определяется как конкатенация

$$A(b_a) = K(\alpha_g) * K(b_a), \tag{6}$$

где  $K(\alpha_g)$  – код ОЛЦ  $\alpha_g \in C$  разрядности  $R_1$ ,  $K(b_g)$  – код вершины  $b_g \in D^g$  (g=1,...,G) разрядности

$$R_2 = \left[\log_2 F_{\text{max}}\right],\tag{7}$$

где  $F_{max}$  — максимальная длина ОЛЦ  $F_{max}$  =  $max(F_1,...,F_G)$ , \* — знак конкатенации. Принципы функционирования КМУУ  $U_1$  и  $U_2$  идентичны, но комбинационная схема КМУУ  $U_2$  формирует системы функций

$$\Phi = \Phi(\tau, X), \tag{8}$$

$$\Psi = \Psi(\tau, X), \tag{9}$$

где  $\psi$  – множество функций возбуждения регистра RG, хранящего код  $K(\alpha_g)$ , представленный переменными  $\tau$ , где  $|\tau| = R_1$ . Кроме того, условие (2) превращается в условие

$$K(b_{g_{i+1}}) = K(b_{g_i}) + 1$$

$$(i = \overline{1, F_g - 1}; g = \overline{1, G}).$$

(10)

Такой подход позволяет использовать известные методы оптимизации автомата Мура [7] для уменьшения аппаратурных затрат в схеме СС. Но при нарушении условия

$$R_1 + R_2 = R \tag{11}$$

емкость управляющей памяти КМУУ  $U_2$  резко увеличивается по сравнению с соответствующим параметром КМУУ  $U_1$ . В настоящей работе предлагается метод, позволяющий использовать метод разделения кодов при нарушении условия (11).

## 3. Метод решения задачи

Пусть для ГСА Г условие (11) нарушается, то есть

$$R_1 + R_2 > R.$$

(12)

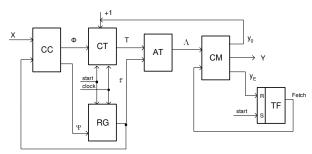

Введем в схему КМУУ U<sub>2</sub> преобразователь адреса АТ и получим КМУУ U<sub>3</sub> (рис.3).

Рис. 3. Структурная схема КМУУ с разделением кодов и преобразователем адреса

Здесь преобразователь АТ реализует систему функций

$$\Lambda = \Lambda(T, \tau),\tag{13}$$

где  $\Lambda = \{\lambda_1, \dots, \lambda_R\}$  — множество переменных, кодирующих адреса микрокоманд в управляющей памяти. Функции остальных структурных элементов схемы КМУУ  $U_3$  и  $U_2$  совпадают.

В настоящей работе предлагается метод синтеза КМУУ U<sub>3</sub>, включающий следующие этапы:

- 1. Преобразование исходной ГСА.

- 2. Формирование удовлетворяющего (1) множества ОЛЦ С.

- 3. Кодирование операторных линейных цепей α<sub>σ</sub>∈ С

- 4. Кодирование операторных вершин преобразованной ГСА.

- 5. Адресация микрокоманд.

- 6. Формирование содержимого управляющей памяти.

- 7. Формирование таблицы переходов КМУУ.

- 8. Формирование таблицы преобразователя адресов.

- 9. Формирование систем функций Ф, Ч, Л.

- 10. Реализация схем КМУУ в заданном элементом базисе.

#### 4. Пример применения предложенного метода

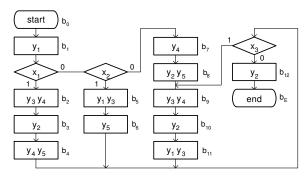

Рассмотрим применение предложенного метода на примере ГСА  $\Gamma_1$  (рис.4).

Рис. 4. Исходная граф-схема алгоритма  $\Gamma_1$

<u>Преобразование исходной ГСА</u>. Преобразование сводится к введению сигнала  $y_E$  в операторные вершины  $b_q$ , такие, что  $\langle b_q, b_E \rangle \in E$ . Если существует дуга  $\langle b_t, b_E \rangle \in E$ , такая, что  $b_t \in B_2$ , то вводится дополнительная вершина  $b_q$ , содержащая  $y_E$ , и дуги  $\langle b_t, b_q \rangle$ ,  $\langle b_q, b_E \rangle$  заменяют исходную дугу  $\langle b_q, b_E \rangle$ . Если существует дуга  $\langle b_0, b_q \rangle \in E$ , такая, что  $b_q \in B_2$ , то вводится дополнительная пустая вершина  $b_t$ , содержащая  $y_E$ , и дуги  $\langle b_0, b_t \rangle$  и  $\langle b_t, b_q \rangle$  заменяют исходную дугу  $\langle b_0, b_q \rangle$ .

В случае ГСА  $\Gamma_1$  преобразование сводится к введению сигнала  $y_E$  в вершину  $b_{12}$ .

Формирование множества ОЛЦ. Для этого используется стандартная процедура из [1]. В нашем случае  $C = \{\alpha_1, \dots, \alpha_5\}$ , где  $\alpha_1 = <b_1>$ ,  $\alpha_2 = <b_2$ ,  $b_3$ ,  $b_4>$ ,  $\alpha_3 = <b_5$ ,  $b_6>$ ,  $\alpha_4 = <b_7$ , ...,  $b_{11}>$ ,  $\alpha_5 = <b_{12}>$ .  $I_1^1 = O_1 = b_1$ ,  $I_2^1 = b_2$ ,  $O_2 = b_4$ ,  $I_3^1 = b_5$ ,  $O_3 = b_6$ ,  $I_4^1 = b_7$ ,  $I_4^2 = b_9$ ,  $O_4 = b_{11}$ ,  $I_5^2 = O_5 = b_{12}$ .

Анализ множества С показывает, что G=5,  $F_1$ = $F_5$ =1,  $F_2$ =3,  $F_3$ =2,  $F_4$ =5,  $F_{max}$ =5. Следовательно, для кодирования ОЛЦ  $\alpha_g \in C$  достаточно  $R_1$ =3 разряда, для кодирования компонент ОЛЦ достаточно  $R_2$ =3. Для адресации микрокоманд достаточно R=4 адресных разряда. Следовательно, условие (11) нарушается и применение модели КМУУ  $U_3$  целесообразно.

Кодирование операторных линейных цепей. Этот этап выполняется аналогично оптимальному кодированию псевдоэквивалентных состояний автомата Мура [7]. Напомним, что ОЛЦ являются эквивалентными, если их выходы связаны с входом одной и той же вершины  $\Gamma$ CA. Для оптимизации аппаратурных затрат коды псевдоэквивалентных ОЛЦ должны входить в один обобщенный интервал  $R_1$  – мерного булева пространства [2].

В нашем случае разбиение  $\Pi_{C}$  множества ОЛЦ С на классы псевдоэквивалентных ОЛЦ включает блоки  $B_1 = \{\alpha_1\}, B_2 = \{\alpha_2, \alpha_3, \alpha_4\}, B_3 = \{\alpha_5\}$ . Закодируем ОЛЦ  $\alpha_g \in C$  следующим образом:  $K(\alpha_1) = 000, K(\alpha_2) = 001, K(\alpha_3) = 011, K(\alpha_4) = 101, K(\alpha_5) = 010$ . Теперь с учетом неопределенностей классу  $B_1$  соответствует код  $K(B_1) = *00,$  классу  $-K(B_2) = **1,$  классу  $B_3 - K(B_3) = *10.$

Кодирование операторных вершин  $\Gamma$ CA. Кодирование выполняется так, чтобы выполнялось условие (10). Используя метод [2], получим  $K(b_1) = K(b_2) = K(b_3) = K(b_3) = K(b_1) = K(b_2) = K(b_3) = K(b_4) = K(b_4) = K(b_5) = K(b_5)$

<u>Адресация микрокоманд</u>. Адреса микрокоманд могут быть присвоены в произвольном порядке, так как они формируются преобразователем AT. При этом микрокомандам  $Y(b_q)$  и  $Y(b_t)$  могут быть присвоены одинаковые адреса, если содержимое вершин  $b_q$  и  $b_t$  совпадает. Это может привести к оптимизации емкости управляющей памяти при ее реализации на FPGA.

Пусть в нашем случае  $A(b_1) = 0000$ ,  $A(b_2) = 0001$ , ...,  $A(b_{12}) = 1011$

Формирование содержимого управляющей памяти. Содержимое СМ представляется таблицей, каждая строка которой содержит адрес микрокоманды и входящие в нее микрооперации. В микрокоманду  $Y(b_q)$ , где  $b_q \neq O(\Gamma)$ , вводится сигнал  $y_0$ , здесь  $O(\Gamma)$  – множество выходов ОЛЦ  $\alpha_g$ ∈С. Например, микрокоманде  $Y(b_1)$  соответствует строка с адресом 0000 и содержимым  $y_1$ , микрокоманде  $Y(b_2)$  – с адресом 0001 и содержимым  $y_0$ ,  $y_3$ ,  $y_4$  и т.д.

Формирование таблицы переходов КМУУ. Для формирования этой таблицы необходимо построить систему формул перехода вида

$$B_i \to \bigvee X_i(I_g^j)I_g^j \qquad (B_i \in \Pi_C),$$

(14)

где  $X_i$  ( $I_g^j$ ) — конъюнкция логических условий, определяющая переход из выхода любой ОЛЦ  $\alpha_q \in B_i$  в операторную вершину, соответствующую входу  $I_g^j$ ,  $\Pi_C^i \in \Pi_C$  — множество классов ОЛЦ, выходы которых не связаны с конечной вершиной ГСА.

В случае ГСА Г  $\Pi_C$  ={B<sub>1</sub>, B<sub>2</sub>} и формулы (14) имеют следующий вид:

$$B_{1} \to x_{1}I_{2}^{1} \vee x_{1}x_{2}I_{3}^{1} \vee x_{1}^{-} x_{2}I_{4}^{1},$$

$$B_{2} \to x_{3}I_{4}^{2} \vee x_{3}I_{5}^{1}.$$

Таблица переходов КМУУ  $U_3$  включает столбцы:  $B_i$ ,  $K(B_i)$ ,  $I_g^j$ ,  $A(I_g^j)$ ,  $X_h$ ,  $\Phi_h$ ,  $\Psi_h$ , h, где  $A(I_g^j)$  – адрес входа  $I_g^j$ ;  $X_h \equiv X_i(I_g^j)$ ;  $\Phi_h$  – набор функций возбуждения СТ, принимающих единичное значение для формирования в СТ кода компоненты ОЛЦ  $\alpha_g$ , соответствующей входу  $I_g^j$ ;  $\Psi_h$  – набор функций возбуждения RG кода ОЛЦ  $\alpha_g \in C$ ;  $h = \overline{1, H}$  – номер перехода. В случае ГСА  $\Gamma_1$  таблица переходов КМУУ  $U_3$  имеет H=5 строк (табл.1)

Таблица парахолор КМУУ II

| гаолица переходов КМУУ Оз |                    |         |            |                                                    |                |                                        |   |  |  |

|---------------------------|--------------------|---------|------------|----------------------------------------------------|----------------|----------------------------------------|---|--|--|

| $\mathbf{B}_{\mathrm{i}}$ | K(B <sub>i</sub> ) | $I_g^j$ | $A(I_g^j)$ | $X_h$                                              | $\Phi_{\rm h}$ | $\Psi_{h}$                             | h |  |  |

| $\mathbf{B}_1$            | *00                | $I_2^1$ | 001000     | $\mathbf{x}_1$                                     | ı              | $D_3$                                  | 1 |  |  |

|                           |                    | $I_3^1$ | 011000     | $\overline{\mathbf{x}_1} \ \mathbf{x}_2$           | 1              | $egin{array}{c} D_2 \ D_3 \end{array}$ | 2 |  |  |

|                           |                    | $I_4^1$ | 101000     | $\overline{\mathbf{x}_1}  \overline{\mathbf{x}_2}$ | -              | D <sub>1</sub><br>D <sub>3</sub>       | 3 |  |  |

| $B_2$                     | **1                | $I_4^2$ | 101010     | X <sub>3</sub>                                     | D <sub>5</sub> | D <sub>1</sub><br>D <sub>3</sub>       | 4 |  |  |

|                           |                    | $I_5^2$ | 010000     | $\overline{x_3}$                                   | 1              | $D_2$                                  | 5 |  |  |

Как видно из таблицы 1, регистр RG и счетчик CT имеют информационные входы D-типа:  $\Psi$ ={D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub>},  $\Phi$  = {D<sub>4</sub>, D<sub>5</sub>, D<sub>6</sub>}.

Формирование таблицы преобразователя адреса. Эта таблица отображает систему функций (13) и имеет столбцы:  $b_q$ ,  $K(\alpha_g)$ ,  $K(b_q)$ ,  $A(b_q)$ ,  $\lambda_h$ , h. Здесь  $\lambda_h$  – набор адресных разрядов, равных единице для h-й строки таблицы (h =  $\overline{1,H_1}$ ). Для ГСА  $\Gamma_1$  таблица АТ имеет  $H_1$ =12 строк и  $H_1$  =  $|B_1|$ . Фрагмент таблицы АТ приведен в таблице 2.

Таблица 2 – Фрагмент таблицы преобразователя адреса

| $b_q$ | $K(\alpha_g)$ | $K(b_q)$ | $A(b_q)$ | $\lambda_{\rm h}$     | h |

|-------|---------------|----------|----------|-----------------------|---|

| $b_1$ | 000           | 000      | 0000     | _                     | 1 |

| $b_2$ | 001           | 000      | 0001     | $\lambda_4$           | 2 |

| $b_3$ | 001           | 001      | 0010     | $\lambda_3$           | 3 |

| $b_4$ | 001           | 010      | 0011     | $\lambda_3 \lambda_4$ | 4 |

Формирование систем функций  $\Phi,\Psi,\lambda$ . Функции  $\Phi$  и  $\Psi$  формируются по таблице переходов КМУУ. Например,  $D_1 = \overline{\tau_2} \, \overline{\tau_3} \, \overline{x_1} \, \overline{x_2} \vee \tau_3 \, x_3$ , что соответствует третьей и четвертой строкам табл.1. Функции  $\lambda_{\rm r} \in \lambda$  формируются по таблице AT. Например, из табл.2 имеем  $\lambda_3 = \overline{\tau_1} \, \overline{\tau_2} \, \tau_3 \, \overline{T_1} \, \overline{T_2} \, T_3 \vee \overline{\tau_1} \, \overline{\tau_2} \, \tau_3 \, \overline{T_1} \, T_2 \, T_3 = \overline{\tau_1} \, \overline{\tau_2} \, \tau_3 \, \overline{T_1} \, T_2$ , что соответствует третьей и четвертой строкам табл.2.

<u>Реализация схемы КМУУ в заданном элементном базисе</u>. Схема СС реализуется на FPGA или CPLD по системам (8) – (9), схема преобразователя адресов АТ реализуется на FPGA или CPLD по системе (13), управляющая память СМ, как правило, реализуется с использованием памяти, входящей в состав кристаллов с FPGA и CPLD [4,5]. Вопросы реализации подобных схем достаточно полно рассмотрены в литературе [4,8] и выходят за рамки данной статьи.

#### 5. Заключение и результаты исследований

Применение метода преобразования адресов позволяет использовать метод разделения кодов при синтезе композиционных микропрограммных устройств управления при любом сочетании разрядности кодов операторных линейных цепей, их компонент и минимальной разрядности адреса микрокоманды. Научная новизна предлагаемого метода заключается в том, что сохраняется возможность оптимального кодирования псевдоэквивалентных ОЛЦ, что позволяет уменьшать аппаратурные затраты в схеме, формирующей коды ОЛЦ и их компонент. Практическое значение метода заключается в том, что применение преобразователя адресов

позволяет уменьшить емкость управляющей памяти за счет произвольной адресации по сравнению с известными методами реализации устройств-аналогов. К недостаткам предложенного метода относится увеличение времени цикла КМУУ за счет введения схемы АТ. Исследования авторов показали, что при выполнении условия (12), оптимальном кодировании операторных линейных цепей и уменьшении емкости управляющей памяти предлагаемый метод позволяет на 12-16% уменьшить аппаратурные затраты по сравнению с КМУУ с общей памятью. Применение метода является перспективным и для КМУУ с элементарными ОЛЦ.

## Литература:

- 1. Баркалов А.А., Палагин А.В. Синтез микропрограммных устройств управления. Киев: ИК НАН Украины, 1997. 135 с.

- 2. Баркалов А.А. Синтез устройств управления на программируемых логических устройствах. Донецк: ДонНТУ, 2002. 262 с.

- 3. Грушвицкий Р.И., Мурсаев А.Х., Угрюмов Е.П. Проектирование систем с использованием микросхем программируемой логики. Петербург: БХВ, 2002.

- 4. T.Luba. Synteza ukladow logicznych. Warszawa: WSIZ, 2001. 238 s.

- 5. Z.Salcic. VHDL and FPLDs in Digital systems Design, prototyping and Customization. Kluwer Academic Publishers, 1998. 412 pp.

- 6. T. Sasao. Switching Theory for Logic Synthesis. Kluwer Academic Publishers, 1999. 316 pp.

- 7. Баркалов А.А. Принципы оптимизации логической схемы микропрограммного автомата Мура. / Кибернетика и системный анализ. 1998, №1. с. 65 72.

- 8. Соловьев В.В. Проектирование цифровых схем на основе программируемых логических интегральных схем. М.: Горячая линия-ТЕЛЕКОМ, 2001. 636 с.

Поступила в редколлегию 06.12.05

#### Рецензент:

Баркалов Александр Александрович, д.т.н., профессор, профессор кафедры ЭВМ ДонНТУ, профессор Университета Зеленогурского (Польша). Цифровые устройства управления. Научная работа, спорт. 83122, г.Донецк, ул. Артема, д.204А, кв.105. (+38062)301-07-35

Мальчева Раиса Викторовна, к.т.н., доцент, доцент кафедры ЭВМ ДонНТУ. Компьютерная графика. Научная работа, туризм. 83000, г.Донецк, ул. Артема, 58, каф. ЭВМ, к.36. (+38062)301-07-35.

Красичков Алексей Александрович, к.т.н, доцент каф ЭВМ ДонНТУ. Цифровые устройства управления на ПЛУ. Научная работа, спорт, музыка. 83005, г.Донецк, ул. Куприна, д.62, кв.33. (+38062)301-07-23.

Халед Баракат, аспирант каф ЭВМ ДонНТУ. Цифровые устройства управления на ПЛУ. Научная работа. 83000, г.Донецк, ул. Артема, 58, каф. ЭВМ, к.36.

### УДК 681.324

Оптимізація схеми композиційного мікропрограмного пристрою керування з розділенням кодів / О.О. Баркалов, Р.В.Мальчева, О.О.Красічков, Халед Баракат // Радіоелектроніка та інформатика. 2006. № 00. С.00-00.

В роботі запропоновано використовувати розділення кодів станів АЖЛ в схемі КМПК. Розглядаються умови використання перетворювача адрес мікрокоманд. Приведено приклад синтезу схеми КМПК з перетворювачем адреси. Проведені дослідження показали, що метод зменшує апаратурні витрати на 12-16%.

Табл. 02. Іл. 04. Бібліогр.: 08 назв.

#### UDC 681.324

**Optimization of the compositional microprogram control unit's circuit with codes sharing** / A.A. Barkalov, R.V.Malcheva, A.A.Krasichkov, Khaled Barakat // Radioelektronica i informatika. 2006. N 00. P.000-000.

The sharing of the FSM state's codes in the CMCU circuit is offered in the article. The conditions of address transformer usage for addressing of microinstructions are considered. The example of the CMCU circuit synthesis with address transformer is given. The carried out researches have shown that the method reduces hardware expenses on 12-16%.

Tab. 02. Fig. 04. Ref.: 08 items.