Арифметические операторы в программировании на HDL

Xilinx®

XST User Guide (10.1), 2008

Об арифметических операторах

XST поддерживает следующие арифметические операторы:

-

Сумматоры:

- С переносом в

- С переносом из

- С переносом в/из

-

Вычитатели:

- Сумматоры/вычитатели

- Схемы сравнения (=, /=, <, <=, >, >=)

- Умножители

- Делители

Сумматоры, вычитатели, схемы сравнения и умножители поддерживаются для знаковых и беззнаковых операторов.

Для более подробной информации по знаковым и беззнаковым операторам поддерживаемым в VHDL, смотрите "Регистры в программировании на HDL".

Кроме того, XST исполняет разделение ресурса для сумматоров, вычитателей, сумматоров/вычитателей и умножителей.

Log-файл арифметических операторов

Log – файл XST сообщает о типе и размере распознанных сумматоров,вычитателей, сумматоров/вычитателей в течение шага Macro Recognition.

Related source file is arithmetic_operations_1.vhd.

Found 8-bit adder for signal .

Summary:

inferred 1 Adder/Subtracter(s).

=============================

HDL Synthesis Report

Macro Statistics

# Adders/Subtractors : 1

8-bit adder : 1

Ограничения, касающиеся арифметических операторов

- "Использование DSP48 (USE_DSP48)"

- "Коэффициент утилизации DSP (DSP_UTILIZATION_RATIO)"

- "Хранение (KEEP)"

Примеры программирования арифметических операторов

Скачать обновления можно с ftp://ftp.xilinx.com/pub/documentation/misc/examples_v9.zip.

Для примера арифметических операторов смотрите пример содержащийся в следующих секциях:

- "Сумматоры, вычитатели, сумматоры/вычитатели в программировании на HDL"

- "Схемы сравнения в программировании на HDL"

- "Умножители в программировании на HDL"

- "Последовательные комплексные умножители в программировании на HDL"

- "Конвейерные умножители в программировании на HDL"

- "Умножающий сумматор/вычитатель в программировании на HDL"

- "Умножающий аккумулятор в программировании на HDL"

- "Делитель в программировании на HDL"

- "Разделение ресурсов в программировании на HDL"

Сумматоры, вычитатели, сумматоры/вычитатели в программировании на HDL

Эта секция рассматривает cумматоры, вычитатели, сумматоры/вычитатели в программировании на HDL, и включает в себя следующие пункты:

- "О cумматорах, вычитателях, сумматорах/вычитателях"

- "Операторы Case cумматоров, вычитателей, сумматоров/вычитателей"

- "Log-файл cумматоров, вычитателей, сумматоров/вычитателей"

- "Ограничения, касающиеся cумматоров, вычитателей, сумматоров/вычитателей"

- "Примеры программирования cумматоров, вычитателей, сумматоров/вычитателей"

О cумматорах, вычитателях, сумматорах/вычитателях

Virtex-4, Virtex-5, и семейство Spartan-3A D позволяют сумматорам /вычитателям быть исполненными на ресурсах DSP48. XST поддерживает один уровень выводов регистров в DSP48 блоках. Если Перенос в или выбор операции сложения/вычитания зарегистрированы, XST погружает эти регистры также в блоки DSP48.

XST может исполнить сумматор/вычитатель в блоке DSP48, если его выполнение требует только единственный ресурс DSP48. Если макрокоманда суммирования/вычитания не соответствует в единственном DSP48, XST осуществляет полный макрос, используя логику сектора.

Выполнение макрокоманды на блоках DSP48 управляется "Коэффициентом утилизации DSP (DSP_UTILIZATION_RATIO)" с заданным по умолчанию значением auto. В режиме auto, если сумматор/вычитатель - часть более сложной макрокоманды такой как фильтра, XST автоматически располагается на блоке DSP. Иначе, XST осуществляет сумматоры/вычитатели, использующий LUTs. Установите значение "Использования DSP48 (USE_DSP48)" в yes вынуждает XST выдвигать эти макрокоманды в DSP48. При размещении сумматора/вычитателя на блоке DSP, XST проверяет, чтобы видеть, является ли это связанным с другими цепями DSP. Если так, XST пробует использовать в своих интересах быстрые связи DSP, и соединяет этот сумматор/вычитатель с цепью DSP, используя эти быстрые связи.

При осуществлении сумматоров/вычитателей на блоках DSP48, XST исполняет автоматическое управление ресурса DSP48.

Для обеспечения лучшего исполнения, XST по умолчанию пробует выводить и осуществлять максимум макро-конфигурации, включая так много регистров в DSP48 насколько возможно. Используйте, "Хранение (KEEP)" ограничение, чтобы формировать макрокоманду определенным способом. Например, чтобы исключить первое состояние регистра из DSP48, место "Хранение (KEEP)" ограничения на выводы этих регистров.

Log-файл cумматоров, вычитателей, сумматоров/вычитателей

Synthesizing Unit .

Related source file is "v_adders_4.v".

Found 8-bit adder carry in/out for signal <$addsub0000>.

Summary:

inferred 1 Adder/Subtractor(s).

Unit synthesized.

======================================================================

HDL Synthesis Report

Macro Statistics

# Adders/Subtractors : 1

8-bit adder carry in/out : 1

======================================================================

Ограничения, касающиеся cумматоров, вычитателей, сумматоров/вычитателей

- "Использованиеe DSP48 (USE_DSP48)"

- "Коэффициент утилизации DSP (DSP_UTILIZATION_RATIO)"

- "Хранение (KEEP)"

Примеры программирования cумматоров, вычитателей, сумматоров/вычитателей

Скачать обновления можно с ftp://ftp.xilinx.com/pub/documentation/misc/examples_v9.zip.

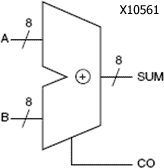

- "Беззнаковый 8-битный сумматор"

- "Беззнаковый 8-битный сумматор с входным переносом"

- "Беззнаковый 8-битный сумматор с выходным переносом"

- "Беззнаковый 8-битный сумматор с входным и выходным переносом"

- "Знаковый 8-битный сумматор"

- "Беззнаковый 8-битный вычитатель"

- "Беззнаковый 8-битный вычитатель с заемом"

- "Беззнаковый 8-битный сумматор/вычитатель"

Беззнаковый 8-битный сумматор

Эта секция рассматривает беззнаковый 8-битный сумматор, и включает в себя следующие пункты:

- "Схема беззнакового 8-битного сумматора"

- "Описание выводов беззнакового 8-битного сумматора"

- "Пример программирования на VHDL беззнакового 8-битного сумматора"

- "Пример программирования на Verilog беззнакового 8-битного сумматора"

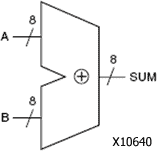

Рисунок 2-37: Схема беззнакового 8-битного сумматора

Таблица 2-44: Описание выводов логического сдвигателя на 3

| Выводы |

Описание |

| A, B |

Операнды суммирования |

| SUM |

Результат суммирования |

Пример программирования на VHDL беззнакового 8-битного сумматора

--

-- Unsigned 8-bit Adder

--

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adders_1 is

port(A,B : in std_logic_vector(7 downto 0);

SUM : out std_logic_vector(7 downto 0));

end adders_1;

architecture archi of adders_1 is

begin

SUM <= A + B;

end archi;

Беззнаковый 8-битный сумматор с входным переносом

Эта секция рассматривает Беззнаковый 8-битный сумматор с входным переносом, и включает в себя следующие пункты:

- "Схема беззнакового 8-битного сумматора с входным переносом"

- "Описание выводов беззнакового 8-битного сумматора с входным переносом"

- "Пример программирования на VHDL беззнакового 8-битного сумматора с входным переносом"

- "Пример программирования на Verilog беззнакового 8-битного сумматора с входным переносом"

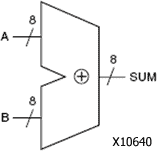

Рисунок 2-38: Схема беззнакового 8-битного сумматора с входным переносом

Таблица 2-46: Описание выводов беззнакового 8-битного сумматора с входным переносом

| Выводы |

Описание |

| A, B |

Операнды суммирования |

| CI |

Вход переноса |

| SUM |

Результат суммирования |

Пример программирования на VHDL беззнакового 8-битного сумматора с входным переносом

--

-- Unsigned 8-bit Adder with Carry In

--

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adders_2 is

port(A,B : in std_logic_vector(7 downto 0);

CI : in std_logic;

SUM : out std_logic_vector(7 downto 0));

end adders_2;

architecture archi of adders_2 is

begin

SUM <= A + B + CI;

end archi;

Пример программирования на Verilog беззнакового 8-битного сумматора с входным переносом

//

// Unsigned 8-bit Adder with Carry In

//

module v_adders_2(A, B, CI, SUM);

input [7:0] A;

input [7:0] B;

input CI;

output [7:0] SUM;

assign SUM = A + B + CI;

endmodule

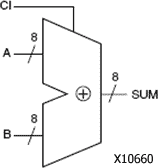

Беззнаковый 8-битный сумматор с выходным переносом

Эта секция рассматривает Беззнаковый 8-битный сумматор с выходным переносом, и включает в себя следующие пункты:

- "Схема беззнакового 8-битного сумматора с выходным переносом"

- "Описание выводов беззнакового 8-битного сумматора с выходным переносом"

- "Пример программирования на VHDL беззнакового 8-битного сумматора с выходным переносом"

- "Пример программирования на Verilog беззнакового 8-битного сумматора с выходным переносом"

Перед тем, как написать а + (плюс) операция с выходным переносом на VHDL, считывается арифметический пакет, который вы планируете использовать. Например, std_logic_unsigned не позволяет писать + (плюс) при следующей форме использования выходного переноса:

Res(9-bit) = A(8-bit) + B(8-bit)

Причина размера результата операции плюс в этом пакете равно размеру длиннейшего аргумента (8 бит).

Одно решение к примеру состоит в том, чтобы регулировать размер операндов А и В к использованию на 9 битов связь.

Res <= ("0" & A) + ("0" & B);

В этом случае, XST признает, что этот сумматор на 9 бит может быть осуществлен как сумматор на 8 бит свыходным переносом.

Другое решение:

- Конвертирование А и В в целые числа

- Конвертирование результата обратно в std_logic вектор

- Определяют, что размер вектора равняется 9

Рисунок 2-39: Схема беззнакового 8-битного сумматора с выходным переносом

Таблица 2-47: Описание выводов беззнакового 8-битного сумматора с выходным переносом

| Выводы |

Описание |

| A, B |

Операнды суммирования |

| SUM |

Результат суммирования |

| CО |

Выходной перенос |

Пример программирования на VHDL беззнакового 8-битного сумматора с выходным переносом

--

-- Unsigned 8-bit Adder with Carry Out

--

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity adders_3 is

port(A,B : in std_logic_vector(7 downto 0);

SUM : out std_logic_vector(7 downto 0);

CO : out std_logic);

end adders_3;

architecture archi of adders_3 is

signal tmp: std_logic_vector(8 downto 0);

begin

tmp <= conv_std_logic_vector((conv_integer(A) + conv_integer(B)),9);

SUM <= tmp(7 downto 0);

CO <= tmp(8);

end archi;

Предыдущий пример использует два арифметических пакета: std_logic_arith

Содержит целое число к std_logic конверсионной функции (conv_std_logic_vector) std_logic_unsigned

Содержит беззнаковую операцию + (плюс)

Пример программирования на Verilog беззнакового 8-битного сумматора с выходным переносом

//

// Unsigned 8-bit Adder with Carry Out

//

module v_adders_3(A, B, SUM, CO);

input [7:0] A;

input [7:0] B;

output [7:0] SUM;

output CO;

wire [8:0] tmp;

assign tmp = A + B;

assign SUM = tmp [7:0];

assign CO = tmp [8];

endmodule