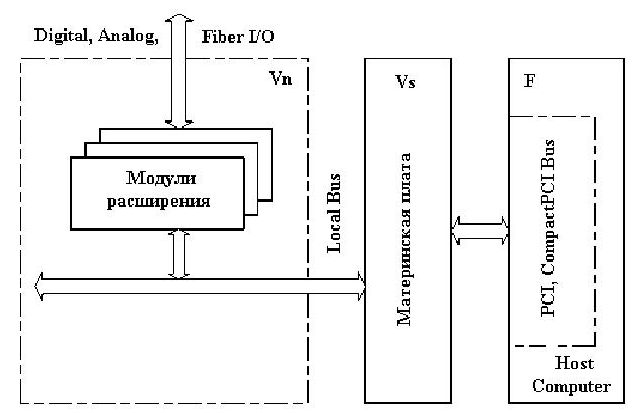

Fig. 1. Generalized structure DCFA (gif-animation, 689 x 324 , 5 slides, 5 cycles, size 141 kb)

Relevance: Currently, modern element base are microprocessors in conjunction with LSI memory and programmable logic integrated circuits (FPGAs).They should not only meet the requirements of a wide range of1 users, but also consider prospect of the future development of computer technology. FPGA technology allows to implement on the chip almost any project digital device for a short period of time without the using of finishing technologies. Reconfigurable FPGA-based systems are widely used in many areas: reconfigurable data processing, digital signal processing, image processing, communications, computing devices of common purpose; verification, also the possibility of processing and sorting data.

The aim of this work is to develop reconfigurable computing system for increasing the speed data sorting.

The main objectives of development and research. To achieve these goals it is necessary:

The object of research: reconfigurable system FPGA.

The subject of development and research: implementation of sorter based on reconfigurable system.

The practical significance of the results contained in the development of reconfigurable systems, which will be used to sort the data.

The main difference of reconfigurable computing system from the existing computing platforms is a dynamic reconfiguration of the equipment in this work platform and implementation of complex dynamic algorithm. At the moment the main method of implementing complex dynamic algorithms is the development of combined hardware-software systems. Reconfigurable computing system has several advantages over the combined computing system. The basic logic element of the reconfigurable computing platform is a hardware computing process, which is the analogue of the software process. Reconfigurable FPGA-based systems are widely used in many areas:

Reconfigurable Computing is a new style of computer architecture enabled by the availability of high density programmable logic chips, or FPGAs (Field Programmable Gate Arrays). FPGAs are integrated circuits consisting of large arrays of uncommitted logic gates and interconnection wires.

The chips are programmed for a specific function by downloading a stream of programming bits to select gate functions and wire connections. A new hardware program can be downloaded to these chips in a few milliseconds. When these chips are added to a conventional computer, we have a machine where we can not only program the software for the computer, but where we can also change the hardware that executes the software.

Reconfigurable computing is a new research area which has developed worldwide over the last decade. In this time around 100 different experimental reconfigurable computers have been designed worldwide, and approximately half have actually been built. The area has its own yearly cycles of specialist conferences, and there are several hundred researchers working in this area worldwide. Many of the experimental machines have shown execution time speedups of hundreds or thousands of times compared to conventional workstations, or even supercomputers. The significance of reconfigurable computing lies in its ability to deliver computing structures with the speed of dedicated hardware circuits, but with the programmability of software.

Reconfigurable processor (RP) is a minimal configuration of the circuit board placed on it by one or more chips of custom FPGA (PPLIS), non-volatile memory for storage of configuration files, elements of the boot configuration file (files) and one or more connectors for connecting external devices (expansion modules).

Sorting - is the process by rearrangement of a given set of data in a certain order. As a measure of the effectiveness of the implementation of sorting algorithms usually take the number of necessary comparisons and the number of hops (permutations) of elements. In general, these values determine the function of N - the number of sorted elements, the depth of the array. Direct methods require some sort x'2 comparisons of elements. In hardware implementation of algorithms sort through the FPGA must take into account the restrictions on the logical resources of chips for the given parameters of sorting process. There are two versions of the FPGA - the implementation of sorting - the linear sorter and sorter on the basis of memory.

Creating of reconfigurable devices based on chips of modern FPGA for computer systems with the possibility of reconfigurable in the presence of an open library of configuration files. It'll allow to implement latest developments in the chips for a short period of time. Implementing of sorters with reconfigurable systems is the most promising idea that will allow increase processing speed.