Источник: http://www.radioradar.net/articles/scientific_technical/analiz_plis.html

В современных ПЛИС - тысячи логических элементов, многие килобайты памяти ОЗУ, сотни внешних сигнальных выводов - возможно использование нескольких несинхронных тактовых сигналов. На ПЛИС нередко создаются устройства с весьма сложной логической структурой. Отладка и поиск ошибок в таких устройствах - задача далеко не простая, и существующий инструментарий нередко оказывается недостаточным. Имеющиеся в распоряжении разработчика средства отладки не лишены недостатков, препятствующих всесторонней отладке, локализации и исправлению ошибок. И здесь на помощь может прийти логический анализатор, сформированный в самой ПЛИС.

Моделирование с помощью САПР ПЛИС - мощное средство отладки. Однако для воспроизведения всех возможных ситуаций объем его оказывается столь велик, что моделирование даже малой части этого объема физически неосуществимо. К тому же, нередко ошибка связана с такой комбинацией или временной последовательностью сигналов на входах ПЛИС, которая, по мысли разработчика, не возникает при работе и поэтому не проверяется и при моделировании. Использование осциллографа практически не помогает обнаружить ошибки, проявляющиеся как неправильная комбинация нескольких сигналов. Мощное средство - логический анализатор, однако он не позволяет подключиться к внутренним сигналам ПЛИС, не поступающим на ее выводы. А нередко (например, при использовании корпусов BGA) нельзя подключиться и к выводам ПЛИС. Кроме того, высокочастотный логический анализатор - дорогой и малораспространенный прибор, не у каждого разработчика есть возможность его использовать.

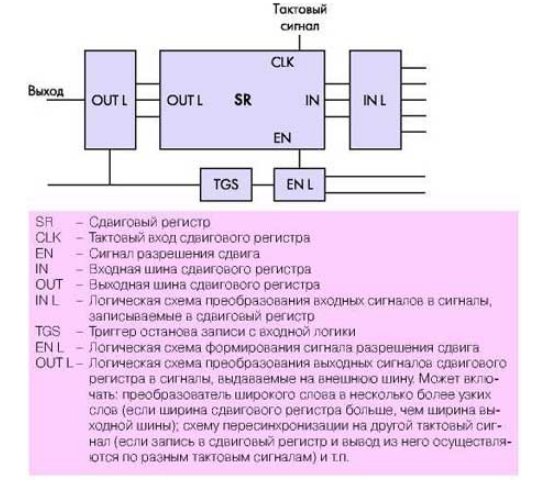

Весьма полезным средством отладки устройства, реализованного на ПЛИС, может оказаться логический анализатор, размещенный внутри этой ПЛИС. Возможность такого размещения, как правило, имеется, поскольку логические ресурсы ПЛИС очень редко задействованы полностью. Обычно часть их остается свободной, и этой части достаточно для реализации логического анализатора. Такой анализатор имеет доступ ко всем логическим сигналам - как к внешним, поступающим на выводы ПЛИС, так и к внутренним, не поступающим на ее внешние выводы. Анализатор позволяет запоминать последовательность сигналов или их комбинаций в сдвиговом регистре, организованном в ПЛИС на одном или нескольких блоках памяти (см. рисунок). Причем запись может вестись как в каждом такте, так и по условию, выработанному на основе логических сигналов ПЛИС. Запись останавливается (по достижении ошибки) либо по условию, выработанному внутри ПЛИС, либо по внешнему сигналу, поступающему, например, от тестового оборудования. После этого сдвиговый регистр хранит информацию и о сигналах на момент проявления ошибки, и о сигналах за предыдущее время (предистория). Считав эти данные, можно получить информацию о непосредственном проявлении ошибки и о том, что ей предшествовало. Анализ этой информации, как правило, позволяет выявить характер ошибки и определить пути ее исправления. Важное достоинство такого логического анализатора - большая гибкость. Можно выбирать как ширину записываемой информации (число записываемых в одном такте бит), так и ее глубину (глубину сдвигового регистра). Разработчик свободен в выборе того, какие биты или их логические комбинации записывать, каковы условия записи и ее останова.

Работает логический анализатор следующим образом. В начальный момент значение триггера TGS равно логическому "0". При этом допускается формирование сигнала разрешения сдвига от комбинации входных сигналов. В ходе работы ПЛИС информация записывается в сдвиговый регистр. При обнаружении ошибки триггер TGS переводится в состояние логической "1". При этом сдвиг от комбинации входных сигналов запрещается, а по мере поступления сигналов чтения производится сдвиг содержимого сдвигового регистра, так что на выходную шину каждый раз подается очередное сохраненное в регистре значение, т.е. сигнал сдвига формируется от сигнала чтения. Запрет сдвига от комбинации входных сигналов на этапе чтения гарантирует отсутствие лишних, не связанных с чтением содержимого сдвигового регистра, сдвигов, которые привели бы к пропаданию части сохраненной информации.

Блок-схема логического анализатора

По данной блок-схеме реализован логический анализатор в ПЛИС типа EP1C6 (семейство Cyclone) фирмы Altera. На этой ПЛИС был выполнен контроллер шины PCI, интерфейс синхронной динамической памяти, интерфейс специализированного микропроцессора и буфера типа FIFO, а также ряд вспомогательных функций. Для реализации сдвигового регистра в составе логического анализатора использовалась стандартная функция Shift Register (RAM Based), доступная через MegaWizard Plugin Manager, входящую в САПР ПЛИС Quartus-ll. Применение стандартной функции позволило создать логический анализатор с минимальными затратами труда и времени разработчика. Выход логического анализатора реализован как 32-бит регистр, доступный по чтению по определенному адресу шины PCI. Установка триггера TGS в состояние логической "1" осуществлялась по чтению из этого регистра. При поиске нескольких различных ошибок менялись ширина и глубина сдвигового регистра, совокупность входных сигналов, логика формирования сигнала разрешения сдвига. Применение логического анализатора позволило значительно ускорить процесс отладки.