Назад в библиотеку

Проблемы верификации систем-на-кристалле на базе FPGA на различных этапах проектирования

Авторы: Горохов И.В., Зинченко Ю.Е.

Источник: Інформаційні управляючі системи та комп’ютерний моніторинг (ІУС та КМ - 2012) - 2012 / Матерiали III мiжнародної науково-технiчної конференцiї студентiв, аспiрантiв та молодих вчених. — Донецьк, ДонНТУ — 2012. — с. 591-594.

Содержание

Аннотация

Горохов И.В., Зинченко Ю.Е. Проблемы верификации систем-на-кристалле на базе FPGA на различных этапах проектирования. В данной статье рассматриваются вопросы верификации встраиваемых систем-на-кристалле (СнК) на базе FPGA на маршруте их проектирования. Проводится обзорный анализ существующих методов верификации систем-на-кристалле и цифровых устройств в целом. На основании обзора формируется перечень актуальных проблем при верификации СнК и возможных путей их преодоления с целью создания качественно нового подхода к верификации FPGA-проектов. В последнее время этому направлению уделяется все больше и больше внимания, как в зарубежных, так и в отечественных изданиях, чему свидетельствует последняя обзорная публикация, датированная февралем 2012 года [1].

Общая постановка проблемы

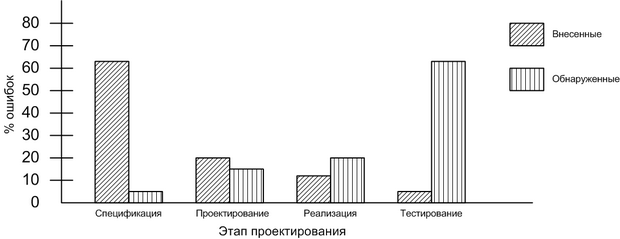

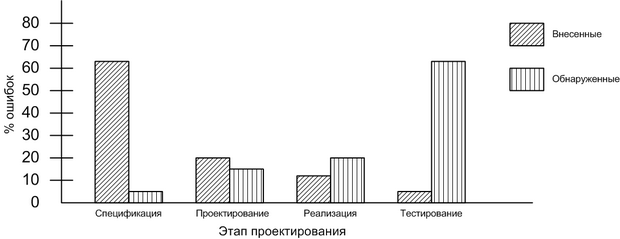

Процесс проектирования цифровых устройств неразрывно связан с понятием верификации. Понятие верификации в общем случае подразумевает под собой проверку совпадения результатов работы разрабатываемого устройства и требований, которые к ним предъявляются. Чтобы представить всю важность верификации достаточно сказать, что она занимает более 60% от общего времени проектирования [2] и привлекает большую часть персонала, работающего над проектом. Большинство существующих методик проектирования цифровых устройств подразумевают верификацию лишь на этапе отладки готового изделия. При таком подходе даже небольшая ошибка, занесенная на ранней стадии, в дальнейшем может привести к более серьезным последствиям, что обычно выражается в дополнительных материальных и временных затратах. При сохранении существующих методик проектирования до 70% ошибок возникает на начальных этапах проектирования и только на этапе отладки готового прибора удается устранить порядка 70% ранее внесенных ошибок [3]. Данная ситуация изображена на рис. 1.

Рисунок 1 — Распределение ошибок при текущей методике проектирования

Становится ясным, что при разработке сложных систем-на-кристалле такой подход к верификации недопустим. Необходимо применение процедур верификации на всем маршруте проектирования с учетом особенностей проектирования СнК на базе FPGA.

Целью написания данной работы является проведение обзорного анализа существующих методик верификации при проектировании цифровых устройств. На основе анализа необходимо сделать вывод о целесообразности применения данных методик для верификации СнК на базе FPGA, выявить особенности верификации проектов этой категории.

Актуальность поставленных задач подтверждается как растущим количеством различных встраиваемых FPGA-систем, так и периодичностью выхода публикаций в зарубежных и отечественных изданиях, посвященных проблемам верификации цифровых устройств.

Существующие подходы к верификации проектов

Все множество методов организации верификации можно разделить на две большие категории — динамические методы и формальные (статические). При рассмотрении методов важнейшими критериями успешности верификации являются полнота покрытия проекта тестами и затраченное на верификацию время.

К динамическим методам относятся симуляционные эксперименты над разрабатываемым проектом на различных этапах проектирования — системный уровень, уровень RTL, топологический уровень. В каждом из случаев на вход системы подается набор тестовых стимулов в виде testbench либо waveform, и сверяются полученные результаты с ожидаемыми. При этом тестируемый объект может быть как физическим образцом (прототипом), так и моделью. При таком подходе к верификации может контролироваться отдельно как функциональность модели (при этом временные показатели опускаются или принимаются равными нулю), так и ее соответствие временным характеристикам (упор на удовлетворение временным показателям), а также эти факторы в совокупности. Достоинством данного метода является теоретическая возможность полного покрытия верификации. На практике же часто случается так, что тестируемое устройство представлено в виде черного ящика

и невозможно сгенерировать стимулы так, чтобы полностью проверить функциональность, либо количество тестовых векторов для полного покрытия может оказаться слишком большим и привести к большим временным затратам. Еще одним недостатком данного подхода является возможность ситуации, когда невозможно наблюдать источник возникновения ошибки во внутренних цепях. Такие ошибки, как правило, проявляют себя на более поздних этапах проектирования, что приводит к дополнительным временным и материальным затратам.

К формальным методам верификации можно отнести внедрение спецификаций проекта в его модель, а также доказательства эквивалентности различных моделей.

Методы внедрения спецификаций проекта в его модель основаны на различных свойствах проекта, которые контролируются путем утверждений внутри самого проекта. Таким образом, модель проекта будет содержать как описание работы, так и описание контроля своих свойств. При создании модели применяются методы строгого математического доказательства соответствия обладания моделью запланированных свойств будущей системы [3]. Данные методы получили название методов ассертирования (утверждений). Простейшей реализацией такого метода является включение в код ассертов, контролирующих определенные свойства проекта. Это достигается путем применения как простейших HDL операторов типа assert, так и использованием специальных языков описания утверждений — PSL (Property Specification Language), OVA (OpenVera Assertions) для описания сложных поведенческих алгоритмов. Развитие данной методики привело к появлению целой методологии, основанной на применении ассертирования — ABD (Assertion-Based Design), в основе которой лежит идея применения целых модулей ассертирования, например, из библиотеки OVL (Open Verification Library) фирмы Accellera. Самым важным моментом в использовании ассертов является правильный выбор контролируемых свойств объекта, от которого зависит полнота покрытия верификации. При правильном выборе свойств полнота покрытия может достигать максимума.

Метод доказательства эквивалентности моделей основан на сравнении работы проектируемой модели с другой моделью. При этом возникает проблема определения правильности работы другой модели, которая берется в качестве эталонной. Примером использования данного метода является сравнение на эквивалентность RTL- и gate- представлений.

Достоинством применения формальных методов является достаточно большая полнота покрытия при более низких по сравнению с динамическими методами временных затратах при условии правильного и полного выбора контролируемых свойств. Недостатком данных методов является невозможность их применения на стадии аппаратной реализации, в отличие от динамических, которые предполагают работу с опытным образцом проекта; также недостатком является сложность САПР, реализующих методы формальной верификации.

Разработка методологии верификации систем-на-кристалле на базе FPGA

Особенности проектирования цифровых устройств на базе FPGA, ввиду автоматизации этапов проектирования в САПР, существенно снижают цену ошибки проектирования. Однако немаловажным все еще остается временной фактор. Поэтому при проектировании сложных устройств, какими являются СнК, необходимо учитывать важность более полного покрытия верификации на всех этапах проектирования с применением существующих методик и их комбинаций. Это влечет за собой необходимость создания качественно новой методологии верификации СнК на базе FPGA, с учетом особенностей целевой платформы.

Разработка новой методологии должна решать следующие проблемы:

- уменьшение времени от начала проектирования до выхода готового изделия на рынок;

- максимизация покрытия верификации проекта;

- исключение верификационной избыточности.

Средства, за счет которых планируется решение перечисленных проблем:

- декомпозиция СнК на составляющие IP-ядра, с применением индивидуальных методик верификации;

- правильный выбор методик верификации и их использование на всех этапах проектирования, в отличие от стандартного маршрута проектирования FPGA-проектов на основе ПЛИС фирмы Xilinx [4], где процедура верификации имеет место лишь после этапа синтеза в виде функционального моделирования устройства без учета верификации исходного описания;

- совмещение по возможности методик нисходящей и сквозной верификации для обеспечения максимального покрытия проекта;

- применение технологии граничного сканирования для верификации достоверности прошивки кристалла, путем обратного чтения конфигурационных данных из запрограммированной ПЛИС и сравнения с содержимым соответствующего файла программирования, который указан для выбранного элемента цепочки периферийного сканирования [5];

- применение технологии граничного сканирования для динамической верификации проекта на аппаратном уровне путем подключения соответствующих ядер, например, с помощью утилиты ChipScope Pro.

Выводы

В ходе обзора существующих методик проектирования цифровых устройств было выявлено, что недостаточность использования процедур верификации на различных этапах проектирования и использование верификации лишь на конечной стадии часто приводит к дополнительным материальным и временным затратам, связанным с откатом на ранние стадии разработки для устранения обнаруженных ошибок. При этом даже небольшая необнаруженная логическая ошибка на ранней стадии проектирования может привести к неработоспособности всего изделия после изготовления опытного образца.

Для изучения существующих решений по применению методов верификации на различных этапах проектирования для сокращения общего времени проектирования и обнаружения ошибок на ранних стадиях разработки был проведен обзорный анализ наиболее типичных методов верификации, используемых в настоящее время. Были выявлены достоинства и недостатки каждого из методов, а также области их возможного применения.

С учетом выполненного анализа было принято решение о создании качественно новой методологии верификации систем-на-кристалле на базе FPGA, с учетом особенностей целевой платформы, которая должна решать ряд поставленных проблем. Особенности целевой платформы хоть и минимизируют стоимость ошибки проектирования, минимизация сроков разработки все еще остается актуальной проблемой. Новая методология верификации должна основываться на правильном выборе и использовании существующих методов на каждой из стадий проектирования индивидуально и обеспечивать должное верификационное покрытие проекта при исключении верификационной избыточности. Ключевым моментом здесь должно стать использование механизма граничного сканирования, который бы обеспечил доступ ко внутренним сигналам проекта для их контроля, что существенно расширит возможности динамической верификации и сведет на нет некоторые из ее недостатков, ограничивающих ее применение.

Литература

- Verification Horizons. A publication of Mentor Graphics – volume 8, issue 1 [Электронный ресурс]. — Режим доступа: http://www.mentor.com/products/fv/verificationhorizons/.

- Немудров В., Мартин Г. Системы-на-кристалле. Проектирование и развитие [текст] / В. Немудров, Г. Мартин — М.: Техносфера. — 2004. — 216 с.

- Грушвицкий Р., Михайлов М. Проектирование в условиях временных ограничений: верификация проектов (1 часть) [Электронный ресурс]. — Режим доступа: http://www.kit−e.ru/assets/files/pdf/2008_3_96.pdf.

- Зотов В. Практический курс сквозного проектирования цифровых устройств на основе ПЛИС фирмы Xilinx (часть 2) [Электронный ресурс]. — Режим доступа: http://www.soel.ru/cms/f/?/347292.pdf.

- Зотов В. Практический курс сквозного проектирования цифровых устройств на основе ПЛИС фирмы Xilinx (часть 20) [Электронный ресурс]. — Режим доступа: http://www.soel.ru/cms/f/?/382795.pdf.