Назад в библиотеку

Особливості верифікації систем-на-кристалі на базі FPGA

Автори: Горохов І.В., Шерекін О.О., Корченко О.О., Зінченко Ю.Є.

Джерело: Сучасні комп’ютерні інформаційні технології (ACIT-2012) / Матеріали школи-семінару молодих вчених і студентів. — Тернопіль, ТНЕУ — 2012.

Зміст

1 Постановка проблеми

Процес проектування цифрових пристроїв тісно пов'язаний з поняттям верифікації. Щоб уявити всю важливість верифікації досить сказати, що вона займає більше 60% від загального часу проектування [1]. Більшість існуючих методик проектування цифрових пристроїв передбачають верифікацію лише на етапі відлагодження готового виробу. При такій методиці до 70% помилок виникають на початкових етапах проектування і лише на етапі відлагодження вдається усунути приблизно 70% помилок [2]. Стає зрозумілим, що при проектуванні складних FPGA проектів, якими є системи-на-кристалі (СнК), існуючий підхід до верифікації є неприпустимим.

Мета роботи

Метою дослідження є аналіз сучасних методів верифікації цифрових пристроїв і СнК зокрема та розробка нової методології верифікації СнК, яка би враховувала особливості їх проектування та використовувала накопичений досвід з питань верифікації цифрових пристроїв.

3 Розробка методології верифікації СнК на базі FPGA

Особливості проектування цифрових пристроїв на базі FPGA, зважаючи на автоматизацію етапів проектування в САПР, істотно знижують ціну помилки проектування. Проте важливим все ще залишається часовий фактор. Тому при проектуванні складних пристроїв, якими є СнК, необхідно враховувати важливість більш повного покриття верифікації на всіх етапах проектування із застосуванням існуючих методик та їх комбінацій. Це тягне за собою необхідність створення якісно нової методології верифікації СнК на базі FPGA, з урахуванням особливостей цільової платформи.

Розробка нової методології повинна вирішувати наступні проблеми:

- зменшення часу від початку проектування до виходу готового виробу на ринок;

- максимізація покриття верифікації проекту;

- виключення надмірності верифікації.

Засоби, за рахунок яких планується вирішення перерахованих проблем:

- правильний вибір методик верифікації і їх використання на всіх етапах проектування, на відміну від стандартного маршруту проектування FPGA-проектів на основі ПЛІС фірми Xilinx [3], де процедура верифікації має місце лише після етапу синтезу у вигляді функціонального моделювання пристрою без урахування верифікації вихідного опису;

- поєднання по можливості методик низхідної і крізної верифікації для забезпечення максимального покриття проекту;

- вживання технології граничного сканування для динамічної верифікації проекту на апаратному рівні шляхом підключення відповідних ядер;

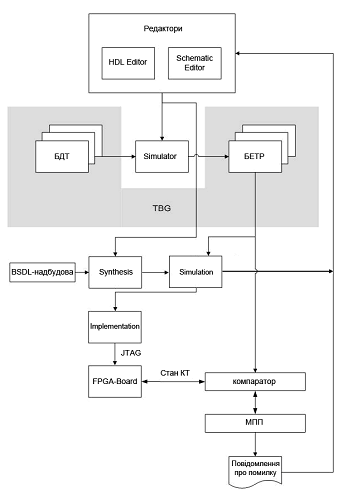

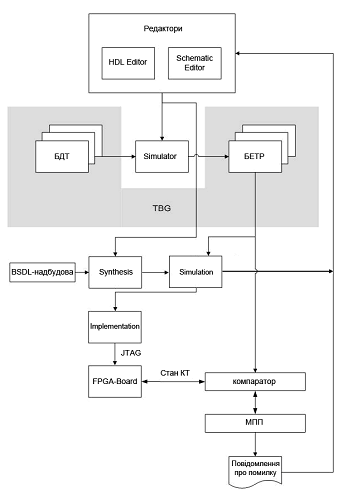

В зв’язку з усіма переліченими вимогами пропонується для розгляду структура системи верифікації СнК на базі FPGA, яка наведена на рис.1.

Рисунок 1 — Схема верифікації СнК на базі FPGA

Цю структуру можна розділити на декілька основних частин/етапів виконання верифікації.

- Вибір HDL-редактора. Перш за все треба визначитися з редактором, в якому буде створена еталонна модель.

- Формування бази даних тестів (БДТ). Тести, що будуть подаватися на еталонний пристрій та на пристрій, що розробляється, для того, щоб впевнитися в їх ідентичності.

- Симуляція еталонного об’єкта. Подача розроблених тестів на відлагоджену модель. Результатом цього процесу є база еталонних тестових реакцій.

- База еталонних тестових реакцій (БЕТР). З нею буде виконуватись порівняння результатів роботи об’єкта, що верифікується. Симулятор, база даних тестів та база еталонних тестових реакцій об’єднуються в один блок TBG — Test Bench Generator.

- BSDL-надбудова. IP-ядра, що надаються розробниками FPGA, задля вбудови в СнК потребують спеціальний апаратний додаток для отримання можливості доступу до внутрішніх сигналів проекту через порт JTAG. Ця технологія має назву периферійне сканування, або Boundary Scan.

- Синтез та відлагодження отриманої моделі. Після виконання процесу синтезу САПР перетворює вихідну модель для подальшої прошивки в FPGA. Після такого перетворення завжди треба виконувати симуляцію та порівняння результатів з БЕТР. У випадку присутності помилок корегується вихідна HDL-модель.

- Прошивка FPGA.

- Подача тестів з БДТ та перевірка їх відповідності БЕТР. У якості пристрою для аналізу використовується компаратор, що розташований на комп’ютері проектувальника. При виявленні помилки робиться висновок, в якому саме елементі вперше з’явилася помилка або яку частину схеми треба перевірити додатково, щоб зробити такий висновок. Цим питанням займається модуль пошуку помилок, в яком реалізований той чи інший алгоритм верифікації.

Висновок

Для вивчення існуючих рішень по вживанню методів верифікації на різних етапах проектування був проведений аналіз сучасних методів верифікації. Були виявлені переваги та недоліки кожного з методів, а також сфери їх можливого застосування.

З урахуванням виконаного аналізу була запропонована структура верифікації FPGA-проектів.

Список використаних джерел

- Немудров В., Мартин Г. Системы-на-кристалле. Проектирование и развитие / В. Немудров, Г. Мартин — М.: Техносфера. — 2004. — 216 с.

- Грушвицкий Р., Михайлов М. Проектирование в условиях временных ограничений: верификация проектов (1 часть) [Электронный ресурс]. — Режим доступу: http://www.kit−e.ru/assets/files/pdf/2008_3_96.pdf.

- Зотов В. Практический курс сквозного проектирования цифровых устройств на основе ПЛИС фирмы Xilinx (часть 2) [Электронный ресурс]. — Режим доступу: http://www.soel.ru/cms/f/?/347292.pdf.