Назад в библиотеку

Построение системы реального времени на базе платформы FPGA фирмы ALTERA

Авторы: Сероштан С.Ю., Горохов И.В., Деменко А.Г., Лобанов Е.В.

Источник: Інформатика та комп’ютерні технології (ІКТ-2011) / Збірка праць VII міжнародної науково-технічної конференції студентів, аспірантів та молодих науковців — 22-23 листопада 2011 р., Донецьк, ДонНТУ . — 2011. У 2-х томах, Т. 1, с. 61-63.

Содержание

Аннотация

Сероштан С.Ю., Горохов И.В., Деменко А.Г., Лобанов Е.В. Построение системы реального времени на базе платформы FPGA фирмы ALTERA. В статье рассматривается разработка системы управления управляющими механизмами, работающей под управлением операционной системы реального времени MicroC/OS-II, с использованием в качестве целевой платформы ПЛИС FPGA фирмы Altera Cyclone II и Cyclone III.

Введение

Рост емкости и производительности ПЛИС FPGA ведущих мировых производителей, таких как Xilinx [1] и Altera [2], приводит к большему использованию данных платформ для решения задач, требующих оперативной обработки данных. То есть появилась возможность использовать FPGA кристаллы для построения сложных систем управления процессами, которые работают в реальном режиме. Поэтому на данный момент актуальным вопросом является рассмотрение процесса разработки подобной системы и ее развертывание на целевой платформе.

Постановка задачи

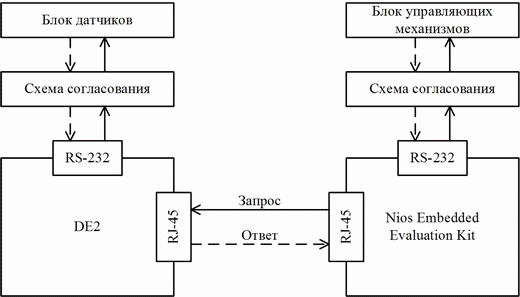

Необходимо построить систему реального времени, задачей которой является управление блоком управляющих механизмов. Управление осуществляется на основе данных полученных от блока датчиков. Важным требованием является возможность устанавливать блок датчиков на неограниченном расстоянии от блока управляющих механизмов (рис. 1).

Рисунок 1 — Размещение блока датчиков и блока управляющих механизмов

Построение системы на кристалле

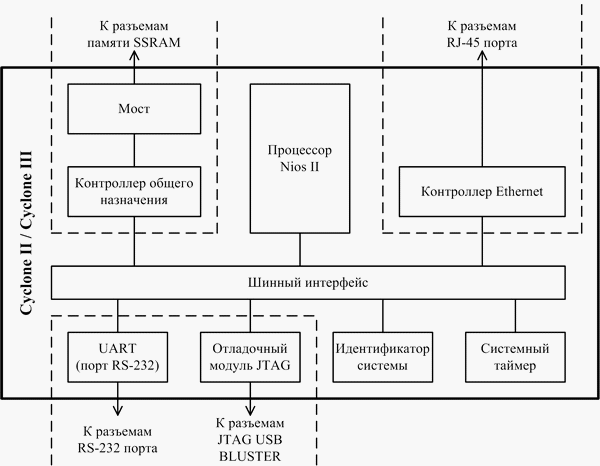

Целевыми платформами разрабатываемой системы на кристалле [3] являются ПЛИС FPGA фирмы Altera Cyclone II [4] и Cyclone III [5].

Для определения компонентов, которые войдут в состав системы на кристалле, необходимо рассмотреть набор требований к проектируемой системе:

- Система должна работать в реальном режиме.

- Система должна иметь интерфейс доступа по сети.

- Система должна иметь интерфейс подключения периферийных модулей.

Для обеспечения первого требования необходимо развернуть в системе на кристалле операционную систему реального времени — MicroC/OS-II, что в свою очередь предусматривает наличие в системе процессора и памяти. Фирма Altera предоставляет ядро программного процессора — Nios II [6]. Интерфейсы доступа по сети и подключения периферийных модулей содержатся в соответствующих контролерах.

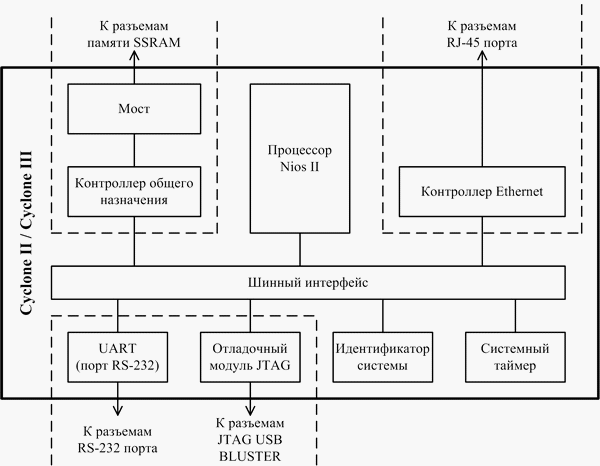

Также в систему (рис. 2) необходимо включить три дополнительных компонента:

- Отладочный модуль JTAG необходим для конфигурирования кристалла, и для последовательной потоковой передачи символов между главным компьютером и системой на кристалле.

- Идентификатор системы предоставляет простое устройство доступное только для чтения, предоставляющее системе на кристалле уникальный идентификатор. Процессорная система Nios II использует идентификатор системы для определения того, что исполняемая программа была собрана для соответствующей аппаратной конфигурации.

- Системный таймер — устройство, предоставляющее такие возможности как: 32-х и 64-х битные счетчики; управляющие сигналы запуска, останова и сброса; два режима счета (нисходящий / восходящий).

Рисунок 2 — Система на кристалле

Развертывание системы на целевой платформе

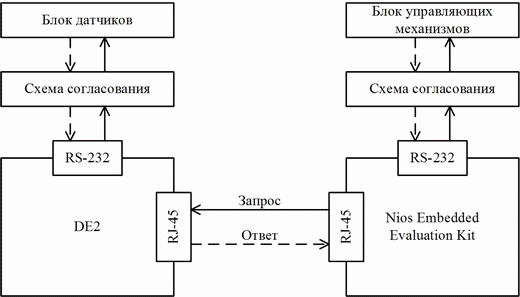

Ранее было отмечено использование в качестве целевых платформ ПЛИС FPGA фирмы Altera Cyclone II и Cyclone III, которые входят в состав отладочных плат DE2 и Nios Embedded Evaluation Kit соответственно. Ниже приведена структурная схема развертывания разработанной системы реального времени (рис. 3).

Рисунок 3 — Структурная схема развертывания разработанной системы реального времени

В состав блока датчиков входят температурные датчики, которые подключены через схему согласования к разъему последовательного RS-232 порта, находящегося на отладочной плате DE2 фирмы Altera. В состав блока управляющих механизмов входят реле, которые подключены к обогревающим механизмам. Для управления реле используется отладочная плата Nios Embedded Evaluation Kit фирмы Altera, которое осуществляется через последовательный порт RS-232 и схему согласования.

Общее взаимодействие выполняется посредством удаленного взаимодействия двух отладочных плат, которые соединены между собой сетевым интерфейсом, что в свою очередь предоставляет возможность удаленного расположения плат, путем их подключения к локальной сети либо сети интернет.

Программное обеспечение, расположенное на отладочной плате DE2 является серверным компонентом, который предоставляет сервис, позволяющий посредством запроса получить значения от любого датчика температуры. Центральное управление всей системой осуществляется алгоритмами, функционирующими в операционной системе реального времени MicroC/OS-II, которая развернута на отладочной плате Nios Embedded Evaluation Kit. Основная задача управляющего алгоритма заключается в периодическом считывании значений датчиков посредством контроллера Ethernet, дальнейшем анализе полученных данных, на основе которого выполняется управление блоком управляющих механизмов. Следует также отметить, в сервисе мониторинга температуры может использоваться один из алгоритмов сглаживания полученных значений. Это связанно с тем, что некоторые из полученных значений датчика могут сильно отличаться от предыдущих значений, что является аномальным явлением и не должно сказываться на работе всей системы.

Выводы

В данной работе был рассмотрен пример построения системы управления, работающей в реальном режиме. В качестве платформы были использованы ПЛИС FPGA фирмы Altera. Важным аспектом использования указанных платформ является возможность быстрой разработки и развертывания подобных систем. Это связанно с наличием большого количества готовых аппаратных и программных компонентов, что в свою очередь позволит разработчикам полностью сосредоточиться на построении общей функциональности системы и не тратить временной ресурс на построение составляющих ее компонентов.

Литература

- FPGA, CPLD, and EPP Solutions from Xilinx, Inc. [Электронный ресурс]. — Режим доступа: http://www.xilinx.com/.

- FPGA CPLD and ASIC from Altera [Электронный ресурс]. — Режим доступа: http://www.altera.com/.

- Rajsuman Rochit. System-on-a-Chip: Design and Test / Rochit Rajsuman. — Boston: Artech House., 2000. — 277 pp.

- Cyclone II Device Handbook, Volume 1. [Электронный ресурс]. — Режим доступа: http://www.altera.com/literature/hb/cyc2/cyc2_cii5v1.pdf.

- Cyclone III Device Handbook, Volume 1. [Электронный ресурс]. — Режим доступа: http://www.altera.com/literature/hb/cyc3/cyc3_ciii5v1.pdf.

- Nios II Processor Reference Handbook. [Электронный ресурс]. — Режим доступа: http://www.altera.com/literature/hb/nios2/n2cpu_nii5v1.pdf.