| Введение в UVM Connect | ||||||||

|

||||||||

| Включение IP и повторное использование VIP | ||||||||

|

Итак, какие новые возможности появляются при использовании данной библиотеки? UVM Connect включает следующие полезные модели, разработанные для обеспечения максимальной степени повторного использования IP:

|

||||||||

| Ключевые особенности | ||||||||

|

Библиотека UVM Connect соединяет TLM-модели на SystemC и UVM на SystemVerilog, что является относительно простым процессом. В этом разделе описываются некоторые ключевые особенности библиотеки UVM Connect.

|

||||||||

| Создание UVMC соединений | ||||||||

|

Для реализации соединения верифицируемые компоненты должны быть синхронизированы по данным, которыми они обмениваются, и должны использовать одинаковые интерфейсы для обмена. TLM соединения, параметризованные по типу объекта (транзакции), помогают компонентам соответствовать данным требованиям и таким образом преодолевать проблему интеграции и увеличить гибкость. Для реализации таких соединений между языками SystemC и SystemVerilog, UVMC предоставляет функции connect и connect_hier.

SystemVerilog TLM2:

uvmc_tlm #(trans)::connect(port_handle, “lookup”);

uvmc_tlm #(trans)::connect_hier(port_handle, “lookup”);

SystemC TLM2

uvmc_connect(port_ref, “lookup”);

uvmc_connect_hier(port_ref, “lookup”);

trans — определяет тип транзакции для однонаправленных TLM1 портов, экспорта и импорта. Необходим только при использовании SystemVerilog.

port_handle или ref — указатель или ссылка на порт, экспорт, импорт, интерфейс или экземпляр сокета, с которым выполняется соединение.

lookup — необязательная строка-идентификатор для регистрации порта.

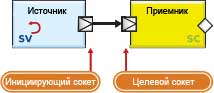

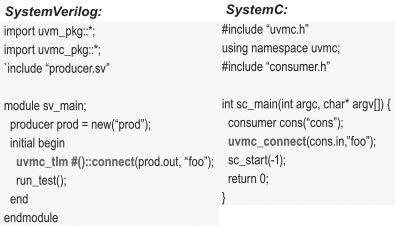

UVMC регистрирует иерархическое имя порта и строковый идентификатор (если таковой имеется) для дальнейшего сравнения с другими регистрируемыми портами как на SystemVerilog, так и на SystemC. Если строки каких-либо двух зарегистрированных портов совпадают, эти порты считаются соединенными независимо от того, написаны ли они на одном языке, либо на разных. Рассмотрим использование функции соединения на примере. Диаграмма ниже показывает как компонент-источник на SystemVerilog и компонент-приемник на SystemC соединяются с помощью TLM сокета.  Следующий код создает тест и UVMC соединение на обоих языках. Приведенный код является полным и пригодным к использованию. Это все, что необходимо выполнить для передачи операции tlm_generic_payload между компонентами на SystemC и SystemVerilog.  В главном модуле sv_main реализован пример на SystemVerilog. Здесь создается экземпляр компонента-источника, после чего регистрируется его выходной сокет в UVMC, используя строковый идентификатор «foo». Далее начинается UVM тестирование посредством вызова run_test(). Функция sc_main реализует пример на SystemC. В ней создается экземпляр приемника sc_module, далее регистрируется его входной сокет в UVMC, используя строковый идентификатор «foo». После этого начинается симуляция посредством вызова sc_start. В процессе работы UVMC соединит сокеты источника и приемника, так как они зарегистрированы с одинаковым строковым идентификатором. (Примечание: Порт в SystemVerilog в действительности будет создан в connect_phase UVM. Этот факт опущен для упрощения примера.) |

||||||||

| Операция преобразования | ||||||||

|

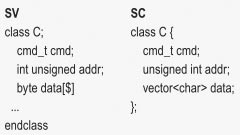

Передача объектов требует наличия преобразователей для перевода между двумя типами, когда используются два языка SystemC и SystemVerilog. UVMC обеспечивает встроенную поддержку средства TLM Generic Payload (TLM GP). При использовании TLM GP нет необходимости делать какие-либо манипуляции, связанные с операциями преобразования. Использование TLM GP также предоставляет наилучшие условия для взаимодействия независимо разработанных компонентов от различных поставщиков IP. Таким образом, имеется огромный стимул к использованию Generic Payload, если это возможно. Однако, если вы не используете TLM GP, задача создания преобразователя в SystemC и SystemVerilog достаточно проста. Допустим, имеется операция с командой, адресом и данными переменной длины. Базовые определения в SystemC и SystemVerilog могут выглядеть следующим образом:  UVMC использует отдельные классы преобразователей для выполнения операций упаковки и распаковки. Это позволяет определить преобразователи независимо от операций, с которыми они имеют дело. По умолчанию UVMC определяет реализацию преобразователя, которая соответствует преобладающей методологии в каждом из языков. UVMC также может размещать практически любое приложение, как например, использование объекта SystemVerilog, который не расширяет uvm_object. |

||||||||

| Преобразование на SystemVerilog | ||||||||

|

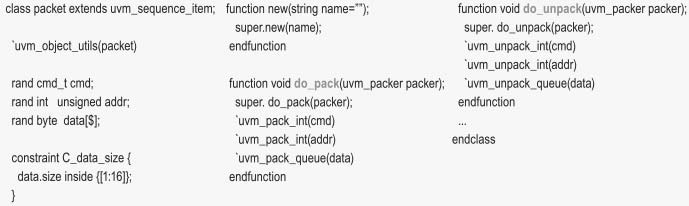

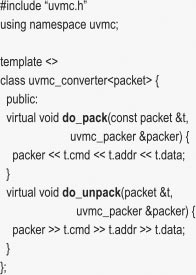

По умолчанию стандартный преобразователь UVMC в SystemVerilog поручает преобразование методам pack и unpack. Если присутствует класса операции, то реализуется собственное преобразование с помощью UVMC.  Операции преобразования UVM обычно реализуются в методах do_pack и do_unpack, либо с помощью макроса `uvm_field. Способ с использованием методов do_pack и do_unpack лучше с точки зрения производительности и обеспечивает большую гибкость, удобство отладки и поддержку типов, чем способ с макросом `uvm_field. Он требует больше времени для реализации этих методов, но это компенсируется высокой производительностью и преимуществами при отладке. Рекомендуемый способ для реализации методов do_pack/unpack включает использование макросов `uvm_pack и `uvm_unpack, которые являются частью UVM стандарта. Эти макросы находятся среди рекомендуемых к использованию. Они меньше и более эффективны, чем макрос uvm_field и API uvm_packer. Следующее определение транзакции показывает рекомендуемый способ описания методов do_pack/unpack:  |

||||||||

| Преобразование на SystemC | ||||||||

|

Классы преобразований в SystemC обычно не расширяют базовый класс, поэтому преобразование выполняется в отдельном классе конвертера.

Конвертер в SystemC является шаблоном конвертера по умолчанию, umvc_converter<T>. Шаблонная специализация позволяет перегружать стандартную реализацию параметризированного класса классом, исключительным для определенного ряда значений параметров, например, uvmc_converter<packet>. Это операция уровня компилятора, поэтому любой код, использующий uvmc_converter Следующий код создает класс преобразователя для класса пакетных операций:  Переменная упаковщика — это экземпляр uvmc_packer, аналог uvm_packer на SystemVerilog. Для передачи транзакций можно использовать потоковые операции встроенного упаковщика. Для упаковки используется оператор <<, для распаковки >>.

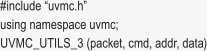

Многие классы преобразователей соответствуют структуре указанного шаблона, за исключением актуальных имен полей, переданных в поток. Поэтому для удобства UVMC обеспечивает макрос, который может генерировать полный класс uvmc_converter Используя опцию макроса, определение специализированного класса преобразователя пакета уменьшается до одной строки:  Числовой суффикс в имени макроса определяет число полей транзакции, которые преобразуются. Далее просто перечисляются поля в порядке, в котором их необходимо поместить в поток. Следует обратить внимание на то, чтобы порядок был одинаков при упаковке и распаковке на стороне SystemVerilog. Данный макрос UVMC поддерживает до 20 полей. |