| Функциональная модель синхронной статической памяти с нулевым временем смены режима (zbt ssram) | ||||||

|

||||||

| Введение | ||||||

|

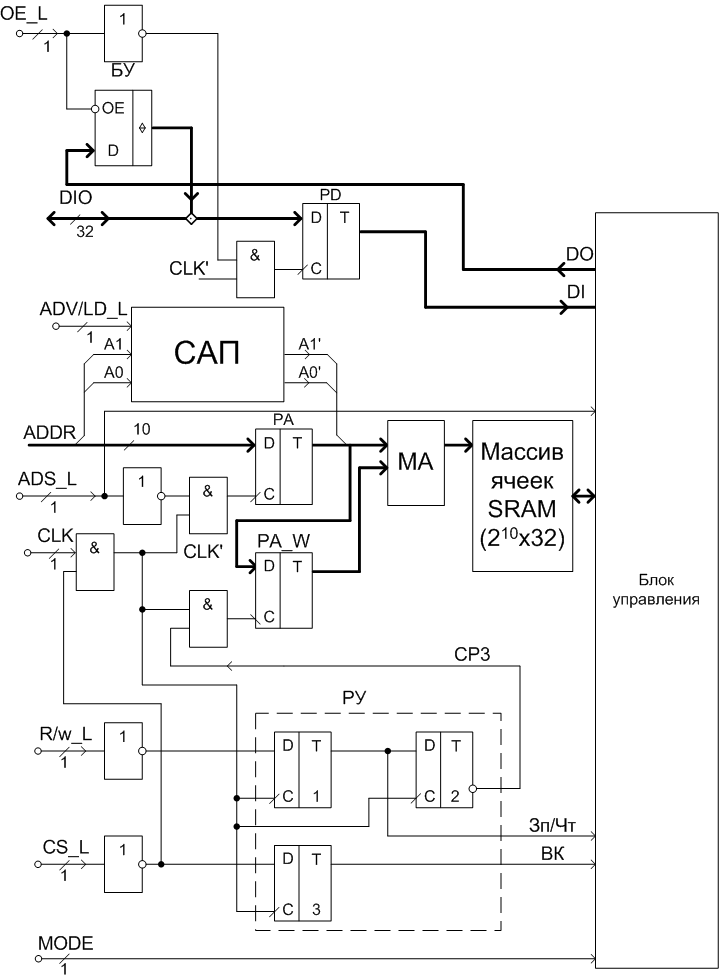

В синхронном статическом ОЗУ (SSRAM, synchronous static RAM) имеется тактируемый интерфейс для сигналов адреса, данных и управления. Микросхемы памяти содержат также внутренние регистры адреса, данных и управления, которые переключаются по фронту тактового сигнала (ТС) синхронизации. Операция, задаваемая передним нарастающим фронтом ТС, выполняется внутри микросхемы на следующем такте. При выполнении операции записи во внутреннем регистре данных фиксируются выходные данные. В памяти типа SSRAM используется протокол с задержанной записью, при котором невозможно организовать запись в соседних тактах по двум различным адресам в ячейки, не следующие одна за другой. Структура памяти SSRAM с задержанной записью не позволяет выполнить цикл чтения на следующем такте после цикла записи и наоборот. При смене режима работы внутренняя матрица памяти должна простаивать не менее одного периода ТС.  Рисунок 1 — Функциональная схема памяти ZBT SSRAM Этот недостаток отсутствует в памяти SSRAM с нулевым временем смены режима — ZBT SSRAM (zero bus turn around). Это обеспечивается за счет усложнения функциональной организации микросхем памяти. Разработчики микросхем, боясь утечки “секретов”, не дают потребителям свои синтезируемые модели и разрабатывают функциональные модели отдельно, часто независимо от синтезируемых, и соответственно не всегда полностью функционально совместимые с реальными схемами. Многие другие компании предоставляют подобные модели лишь платно. Поэтому целью данной работы является разработка и исследование функциональной модели памяти типа ZBT SSRAM в различных режимах работы, а также выявление особенностей и характеристик при построении модулей памяти. |

||||||

| Функциональная модель памяти ZBT SSRAM | ||||||

|

Функциональная схема памяти типа ZBT SSRAM представлена на рис. 1. В ее состав входят следующие основные блоки: массив ячеек статической памяти (SRAM) организацией 1024 ячеек по 32 разряда каждая, блок управления (БУ), регистры адреса (РА), адреса-записи (РА_W), данных (РD), управления (РУ), счетчик адреса пакета (САП), буферные усилители (БУ) с тремя состояниями и логические схемы обрамления. Рассмотрим назначение сигналов интерфейса памяти. CS_L — сигнал выборки устройства памяти (уровень активности низкий). CLK — тактовый сигнал синхронизации блоков памяти. Используется вместе с сигналом CS_L и распознается только при низком уровне этого сигнала. ADS_L — сигнал адресного строба (уровень активности низкий). Сопровождает подачу адресных сигналов. ADDR — адресные входы для выбора ячейки памяти. Младшие адресные линии А1 и А0 поданы для записи в счетчик адреса пакета (САП). ADV / LD_L — сигнал управления САП. При высоком уровне сигнала используется внутренний САП, при низком уровне сигнала в САП загружается новый адрес пакета по линиям А1 и А0. OE_L — сигнал управления БУ и записью данных в регистр PD. При низком уровне сигнала БУ открыты. Этим обеспечивается передача данных с внутренней шины DO на выходную шину DIO. При высоком уровне сигнала OE_L выходы БУ находятся в третьем состоянии, поэтому данные с шины DIO по нарастающему фронту ТС записываются в регистр данных PD и выдаются на внутреннюю шину DI. R / W_L — сигнал задания режима работы памяти. Высокий уровень задает операцию считывания данных из матрицы SRAM, низкий уровень - записи данных в матрицу SRAM. MODE — сигнал выбора пакетного режима работы. При высоком уровне сигнала задается одиночный режим работы, при низком — пакетный режим. Сигналы R / W_L и CS_L записываются по нарастающему фронту ТС в триггера Т1 и Т2 регистра управления (РУ) и выдаются в качестве сигналов записи-чтения (Зп / Чт) и выбора кристалла (ВК) в блок управления. Триггер Т2 РУ фиксирует тип выполняемой операции, заданной на предыдущем такте работы памяти. Инверсный выход этого триггера является сигналом разрешения записи (СРЗ) в регистр адреса-записи РА_W. Мультиплексором адреса (МА) выбирается адрес ячейки памяти из регистров РА или РА_W. Управление МА осуществляет блок управления. При выполнении операции считывания данных из SRAM выставляется адрес считываемой ячейки ADDR, сопровождаемый сигналом адресного строба ADS_L = 0, а также сигналы чтения R / W_L = 1, выбора устройства CS_L = 0 и управления БУ OE_L = 0. С приходом нарастающего фронта ТС адрес и управляющие сигналы записываются во внутренние регистры адреса РА и управления РУ микросхемы памяти. Начинается цикл считывания данных из массива ячеек SRAM по адресу из РА. С задержкой срабатывания SRAM данные появляются на выходной шине памяти DO и удерживаются на ней в течение всего тактового периода. Поскольку сигнал OE_L низкого уровня, буферные усилители БУ с тремя выходными состояниями открыты и данные появляются на выходной шине микросхемы памяти. Считывание этих данных в процессор происходит с поступлением очередного фронта ТС (то есть на следующем такте). При выполнении операции записи данных в SRAM выставляется адрес ячейки записи ADDR, сопровождаемый стробом ADS_L = 0, а также сигналы записи R / W_L = 0, CS_L = 0 и OE_L = 0. С поступлением ТС адрес и управляющие сигналы записываются во внутренние регистры РА и РУ. Поскольку внешняя шина DIO может быть занята достоверными данными от предыдущей операции, операция записи откладывается. На время ожидания записи адрес и связанная с ним информация должны быть сохранены в другом регистре адреса PA_W, поскольку регистр РА вновь используется другими операциями. Операция записи в SRAM становится возможной в том случае, когда на линиях адреса и управления инициируется еще одна операция записи или не выполняется никакой операции (NOP > ADS_L = 1). Для выполнения отложенной операции записи в следующем текущем такте на шину DIO выставляются записываемые данные и выдается сигнал OE_L высокого уровня, по которому выходы БУ переводядся в третье состояние. Данные записываются в регистр данных PD по фронту тактового сигнала. Как только появляется возможность (определяется блоком управления), данные из регистра PD записываются в ячейку SRAM по адресу, выбираемому из адресного регистра РА_ W. |

||||||

| Экспериментальные исследования | ||||||

|

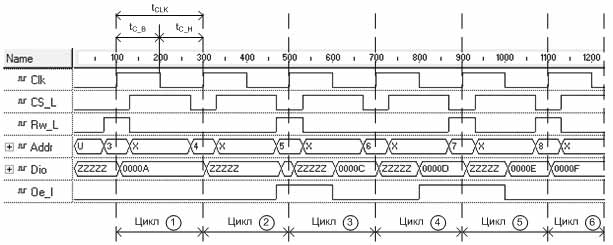

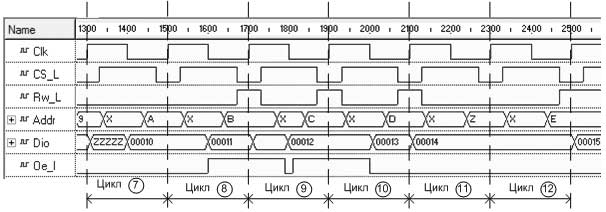

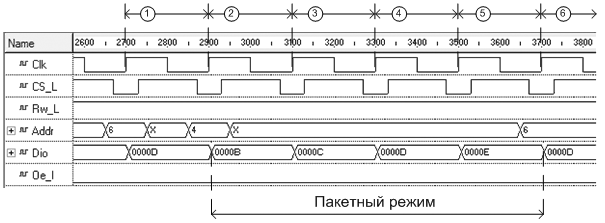

Экспериментальные исследования проводились методом математического моделирования модуля памяти ZBT SSRAM на языке VHDL с использованием инструментальной среды Active — HDL. Результаты модельных экспериментов представлены на рис.2 — рис.4. На рис. 2 представлены первые шесть циклов работы памяти в последовательности выполняемых операций: R1 (3, A) > W1 (4, B) > R2 (5, C) > W2 (6, D) > R3 (7, E) > R4 (8, F), где R1 — первая операция чтения, W1 — первая операция записи. В скобках в 16-й системе счисления обозначены соответственно адрес и данные. На рис.3 представлены следующие шесть циклов работы памяти с 7 по 12: W3 (9, 10) > W4 (10, 11) > R5 (11, 12) > R6 (12, 13) > R7 (13, 14) > NOP.  Рисунок 2 — Временная диаграмма первых шести циклов памяти  Рисунок 3 — Временная диаграмма 7-12 циклов работы памяти  Рисунок 4 — Временная диаграмма пакетного цикла памяти На рис.4 показан пакетный цикл считывания данных. Данные считываются из следующих одна за другой ячеек. В этом режиме используется САП, поэтому нет необходимости в каждом такте выдавать новый адрес. Времена предустановки и удержания сигналов адреса (tSA, tHA), данных (tSH, tHD), выборки кристалла (tSC, tHC) и чтения-записи (tSW, tHW) приняты при выполнении экспериментов равными 2,5 и 0,5 нс соответственно. Из анализа модельных экспериментов следует, что в памяти ZBT SSRAM с целью исключения конфликта ресурсов на двунаправленной шине данных DIO операции считывания данных предоставлен приоритет. Операция записи откладывается на один или более тактов териода CLK. На время ожидания записи адрес и связанная с ним информация должны быть сохранены в специально отведенных для них дополнительных регистрах. Отложенная операция записи данных выполняется в том случае, если на линиях интерфейса памяти инициируется еще одна операция записи или не выполняется никакой операции. |

||||||

| Выводы | ||||||

|

||||||

| Литература | ||||||

|