УДК 004.31

КОНВЕЕРНАЯ РЕАЛИЗАЦИЯ НА FPGA СУММАТОРОВ И УМНОЖИТЕЛЕЙ

Автор Волошин Д.Н.1), Зинченко Ю.Е.2), Войтов Г.В.3)

1. Донецкий национальный технический университет, магистр

2. Донецкий национальный технический университет, к.т.н., доцент кафедры компьютерная инженерия

3. Донецкий национальный технический университет, аспирант кафедры компьютерная инженерия

Источник: Інформатика і комп’ютерні технології (ІКТ-2011) / Матерiали VII мiжнародної науково-технiчної конференцiї студентiв, аспiрантiв та молодих вчених – Донецьк, ДонНТУ – 2011, с. 44-47.

I. Постановка проблемы

Одним из перспективных направлений исследований является конвейеризация FPGA-проектов, что позволяет существенно повышать быстродействие по сравнению с традиционным проектированием [1]. Так как арифметические схемы занимают значительную часть среднестатистического вычислительного устройства, то построение быстродействующих структур таких схем играет ключевую роль [2-3].

II. Цель работы

Целью работы является разработка и исследование конвейерных схем и методики проектирования сумматоров и умножителей, ориентированных на реализацию на FPGA.

III. Реализация конвейерного сумматора и умножителя

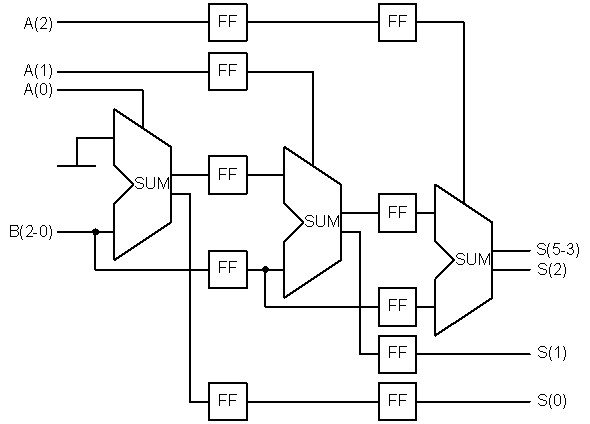

Конвейерный сумматор строится путем добавления в классическую схему сумматора ступеней (уровней) синхронных триггерных элементов (FF) так, как показано на рис.1 (синхросигналы не показаны, но подразумеваются [4]).

Рисунок 1 – Схема конвейерного сумматора

Так как матричный умножитель также строится на основе сумматоров [2], то его конвейерная модификация может быть построена по аналогичной схеме (см. рис. 2).

Рисунок 2 – Схема конвейерного умножителя

В таблицах 1 и 2 приведены сравнительные результаты реализации предложенных структур на FPGA семейства Virtex6 в среде Xilinx ISE 12.4 (www.xilinx.com ) в зависимост от их разрядности и числа ступеней.

Таблица 1 - Результаты синтеза сумматоров

|

Разрядность, n |

Число ступеней, m |

Комбинационный |

Конвейерный |

||

|

Затраты, LUTs |

Задержка, ps |

Затраты, LUTs |

Задержка, ps |

||

|

512 |

2 |

512 |

9189 |

513 |

5151 |

|

4 |

1539 |

2975 |

|||

|

8 |

1799 |

1887 |

|||

|

256 |

2 |

256 |

4837 |

257 |

2975 |

|

4 |

771 |

1887 |

|||

|

8 |

903 |

1343 |

|||

|

16 |

975 |

1071 |

|||

|

32 |

1023 |

935 |

|||

Таблица 2 - Результаты синтеза умножителей

|

Разрядность, n |

Комбинационный |

Конвейерный |

Прирост аппаратных затрат |

||

|

|

Задержка, ps |

Затраты, LUTs |

Задержка, ps |

Затраты, LUTs |

|

|

8 |

7755 |

64 |

935 |

90 |

41% |

|

16 |

16144 |

256 |

1071 |

314 |

23% |

|

32 |

32824 |

1024 |

1343 |

1146 |

12% |

На основе анализа результатов синтеза можно сделать следующие выводы:

Выводы

В данной работе были предложены структуры конвейерных схем сумматоров и матричных умножителей. Проведенные исследования показали, что за счет использования дополнительных ресурсов FPGA может быть существенно повышено быстродействие арифметических устройств.

Предложенные в работе структур могут быть использованы при построении более сложных устройств кодирования, шифрования, аппаратной сортировки и архивации, цифровой обработки сигналов.

Список использованных источников