Реализация булевого выражения на Xilinx Spartan 3E Starter board с помощью LabVIEW FPGA

Автор: Vincent Claes

Автор перевода: Кревега В.

Источник: FPGA PLATFORM WITH DATA-I/O CAPABILITIES FOR INDUSTRIAL AND EDUCATIONAL APPLICATIONS - 2. [Электронный ресурс]. – Режим доступа: http://pwo.fpga.be

Перед началом работы

Прежде, чем начать выполнение данной работы, необходимо выполнить все необходимые настройки целевой платы - Xilinx Spartan-3E Starter Kit. По причине это рекомендуется прочесть руководство пользователя платы. Необходимо удостовериться в качестве подключения USB-кабеля и кабеля питания. Перед началом работы плата должна быть включена.

Создание проекта и ВП для исполнения на FPGA-плате

Сперва необходимо запустить среду LabVIEW 8.5. И создать пустой проект (Empty Project). В окне управления созданного пустого проекта необходимо добавить в рабочую среду плату Spartan3E как целевое устройство (Hardware target). Для этого после щелчка правой кнопкой на позиции «My Computer» в окне проекта. Во всплывшем меню необходимо выбрать пункт «New», а затем «Targets and Devices», как показано на рис.1.

В открывшемся окне необходимо выбрать XUP платы, для чего нужно отметить позицию «New target or device» (рис.2). После этих действий откроется список «Targets and Devices». Необходимо прокрутить список до конца вниз и выбрать «Spartan-3E Starter board» из папки «Xilinx university Program». Эти действия добавят FPGA-плату в список доступных устройств, что будет отображено соответсвующей иконкой под пунктом «My Computer» окна управления проектом.

Добавление средств ввода/вывод FPGA-платы

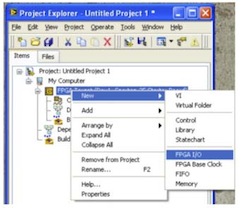

Следующим шагом необходимо добавит средства ввода/вывода платы («FPGA I/O»), которые можно будет использовать в дальнейшем в проекте, в окно упраления проектом. Для этого необходимо, кликнув правой кнопкой мыши, по добавленному ранее FPGA-устройству, выбрать пункт всплывшего меню «New», а затем «FPGA I/O» (рис. 3), в следствие чего появится окно, изображенное на рис. 4.

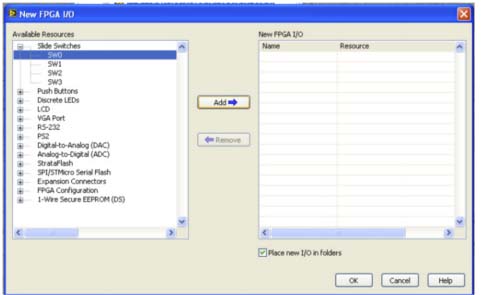

В левой области окна можно увидеть все ресурсы, которые доступны к использованию на плате Spartan-3E. Для того, чтобы добавить нужные средства ввода/вывода к проекту, необходимо выбрать их в левой области окна и нажать кнопку «Add». Теперь нужное средство ввода/вывода информации добавлено в список в левой области окна . В данном проекте нужны SW0, SW1 и LED0. Теперь добавленные средства ввода/вывода отображены также в окне управления проектом. С помощью них будет реализована тестовая булевская функция.

Создание виртуального прибора FPGA

Следующий шаг – создание программы для устройства, которая будет выполняться на целевой плате Xilinx Spartan-3E.

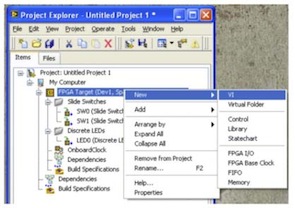

Для этого необходимо снова кликнуть правой кнопкой мыши на целевом устройстве FPGA в окне управления проектом и выбрать во сплывшем меню пункт «New», «VI» (рис.5). Если же щелчок выполнен на позиции « My Computer», будет создана программа, выполнение которой будет происходить непосредственно на перональном компьютере.

Этот шаг откроет лицевую панель и блок-диаграмму виртуального прибора FPGA, в заголовках окон которых будет указано имя ВП с подписью «/FPGA Target», свидетельствующей о том, что создаваемый ВП предназначен для выполнения на плате FPGA. Код будет реализовывать функцию «Исключающего ИЛИ» .

В окне блок-диаграммы при нажатии правой кнопки мыши можно наблюдать палитру множества доступных функций, распределенных по группам, среди которых в том числе и e «FPGA I/O», «Memory & Fifo» и «FPGA Math& Analysis», которые предназначены специально для использования в FPGA-платах. В группе палитры функций следует выбрать раздел «FPGA I/O», из которго необходимо добавить в блок-диаграмму 2 узла ввода/вывода (рис.6).

Однако добавленные узлы не определены. Один из узлов следует расширить еще одним элементом, что можно сделать с помощью пунктов всплывающего меню «Add Element». Для инициализации элементов узла необходимо щелкнуть на нем правой кнопкой мыши и во всплывшем меню выбрать «Select FPGA I/O», «Slide Switches», «SW0» для одного элемента и «SW1» для другого. Теперь внутри узлов появились зеленые надписи «SW0» и «SW1» соответственно. Надписи на узлах указывают на тип средства ввода – «Slide Switch», а цвет надписей указывает на boolean-тип данных узлов, что соответствует принципу работы двухпозиционного переключателя.

Оставшийся узел ввода/вывода следует инициализировать значением «LED0» аналогично вышеописанным действиям.

Таким образом на блок-диаграмме ВП расположены 2 узла ввода/вывода, один из которых состоит из двух элементов «Slide Switch», а другой представляет собой отображение светодиода платы.

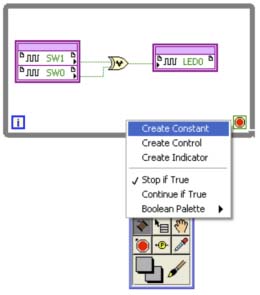

Для реализации тестовой функции из палитры функций из группы «Programming», «Boolean» выбирается функция «Exclusive Or» и помещается на блок-диаграмму.

Два входа функции необходимо соединить с элементами «SW0» и «SW1», а выход – с элементом «LED0». Однако такого вида код выполнит операцию лишь единожды. Для многократного последовательного вычисления на блок-диаграмму из палитры функций помещается «While Loop», который охватывает ранее созданный код. На условие остановки цикла подается boolean-переменная «False». Таким образом, результат тестовой функции будет вычисляться непрерывно.

В результате вышеописанных действий получен код вид которого представлен на рис.7.

Разработанный ВП необходимо сохранить. Для этого в окне лицевой панели или блок-диаграммы в пункте меню «File», «Save As» указывается имя и путь сохраняемого ВП. Аналогичным образом следует сохранить и файл проекта.

Запуск виртуального прибора FPGA на исполнение

Теперь, когда ВП для FPGA разработан, можно запустить его исполнение на целевой плате. Для этого в окне лицевой панели или блок-диаграммы необходимо нажать стилизованную под стрелку кнопку «Run».

После этого LabVIEW запустит процесс генерации промежуточных файлов «Generating Intermediate Files». Эти файлы будут отправлены в модуль «Xilinx Synthesis Tools» для генерации битстрима. На этом шаге LabVIEW открывает меню «Compile Server» - сервис, который позволяет выполнить ресурсоемкую компиляцию кода на другом, более мощном компьютере, чем имеющийся в распоряжении.

Когда появляется сообщение о завершении генерации битстрима для платы «Bitstream generation is complete» и статус сервера уставлен в «Idle…», модуль Xilinx Synthesis Tools выполнил свою работу. Пользователю выводиться отчет о компиляции, где можно увидеть детали реализации скомпилированного кода.

После закрытия отчета о компиляции по нажатию клавиши «ОК», ВП начинает свою работу на целевой FPGA плате, что отображается на экране черной закраской клавиши «Run».

Теперь, изменяя положение клавиш SW0 и SW1 на плате, можно наблюдать изменение состояния светодиода LED0 в соответсвии с логикой функции «Исключающее ИЛИ». Однако, если выполнение ВП будет остановлено с рабочего компьютера, функция будет стерта с платы. Для предотвращения этого эффекта данный ВП можно загрузить на флеш-память платы.

Запись ВП LabVIEW во флэш-память платы

Для записи разработанного ВП во флэш-память платы Spartan-3E Starter board, необходимо выполнить ряд действий. Сперва нужно включить опцию «Run when loaded to FPGA». Для этого нужно кликнуть правой кнопкой мыши по позиции «FPGA Target» в окне управления проектом. Во всплывшем меню нужно выбрать пункт «Properties», в окне которого и находится искомая опция.

После включения данной опции нужно перекомпилировать ВП, поскольку в него было внесено изменение. Для этого в окне управления проектом нужно кликнуть правой кнопкой мыши по пункту с иконкой разработанного ВП и во всплывшем меню выбрать пункт « Compile». После выполнения компиляции и выдачи отчета об успешной компиляции можно приступить непосредственно к загрузке ВП во флэш-память платы.

Для этого в окне управления проектом нужно кликнуть правой кнопкой мыши по пункту с иконкой разработанного ВП и во всплывшем меню выбрать пункт «Download VI to Flash Memory», после чего будет начата загрузка ВП в память платы. Когда появится сообщение, представленное на рис.8, загрузка ВП во флеш-память платы завершена.

Теперь USB-кабель можно извлечь из платы. После нажатия клавиши PROG на плате начнется работа загруженного ВП.

Автор: Vincent Claes

Автор перевода: Кревега В.

Источник: FPGA PLATFORM WITH DATA-I/O CAPABILITIES FOR INDUSTRIAL AND EDUCATIONAL APPLICATIONS - 2. [Электронный ресурс]. – Режим доступа: http://pwo.fpga.be