ПЕРСПЕКТИВНЫЕ АРХИТЕКТУРЫ И ТЕНДЕНЦИИ РАЗВИТИЯ СОВРЕМЕННЫХ СЕТЕВЫХ ПРОЦЕССОРОВ

Авторы: В.И. Грищенко, Ю.В. Ладыженский, Моатаз Юнис

Источник:#

Авторы: В.И. Грищенко, Ю.В. Ладыженский, Моатаз Юнис

Источник:#

В.И. Грищенко, Ю.В. Ладыженский, Моатаз Юнис. Перспективные архитектуры и тенденции развития современных сетевых процессоров. Описаны особенности и функции сетевых процессоров. Проведен анализ современных СП, их технических характеристик и функциональных возможностей. Предложена обобщенная структура, отражающая перспективные тенденции в разработке сетевых процессоров.

Сетевые процессоры (СП), как самостоятельный класс устройств, появились в конце 1990-х годов. Их создание было обусловлено увеличением объемов потоков данных в компьютерных сетях и, связанного с этим, повышения требований к пропускной способности сетевого оборудования. За прошедшее десятилетие СП развивались, в основном, в направлении увеличения производитель- ности и расширения функциональности.

Основным требованием к сетевым процессорам является способность обрабатывать поток пакетов со скоростью канала, к которому подключен маршрутизатор. Следует отметить, что маршрутизаторы могут использоваться как в магистральных сетях, где скорость передачи данных может превышать сотни гигабит в секунду, так и на маршрутизаторах обычных пользователей, работающими со скоростями от десятков Мб/с до нескольких Гб/с. При этом в разных типах сетей используются различные реализации СП.

В качестве основных отличий сетевых процессоров от процессоров общего назначения следует отметить [1]:

В настоящее время большую часть сетевых процессоров для высоконагруженных систем разрабатывает компания EZchip [2]. Основным продуктом этой компании в настоящее время являются сетевые процессоры NP-3 [3], обеспечивающие пропускную способ- ность, равную 30 Гб/с (см. табл. 1).

Сетевые процессоры NP-3 включают в себя менеджеры трафика для входящих и исходящих пакетов с 4-х уровневой иерархической классификацией пакетов; блоки поиска, которые могут использоваться для маршрутизации, коммутации и обеспечения политик безопасности; а также аппаратную реализацию протокола OAM (Operation, Administration, and Maintenance), упрощающую администрирование и поддержку маршрутизаторов. Маршрутные таблицы для этого процессора хранятся во внешней DRAM?памяти и могут достигать 1.5 Гбайт.

Для покрытия возрастающих требований современных компью- терных сетей компания EZchip выпустила сетевой процессор следующего поколения NP-4 [3], который обеспечивает пропускную способность маршрутизатора на уровне 100 Гб/с (50 Гб/с в дуплексном режиме). Этот СП основан на архитектуре NP-3, но имеет большую пропускную способность и более широкий набор функций (см. табл. 1).

Помимо функций, реализованных в NP-3, NP-4 предоставляет поддержку потокового видео и IPTV, встроенный блок взаимодействия с внешними матрицами коммутации, функции формирова- ния трафика, большее число алгоритмов планирования очередей.

Сетевой процессор следующего поколения NP-5 [5] будет обеспечивать работоспособность 200 Гб/с сетей. При этом обеспечивается полная обратная программная совместимость с процессорами NP-4.

Среди производителей процессоров для устройств доступа наиболее крупным является компания PMC-Sierra, которая предлагает сетевые процессоры семейства WinPath3 [6], обеспечивающие пропускную способность до 10Гб/с. Благодаря гибкой архитектуре, эти устройства могут использоваться как в проводных, так и беспроводных сетях (см. табл. 1).

Процессоры WinPath3 содержат два отключаемых вычислительных ядра общего назначения и до 12 специализированных вычислительных ядер для обработки пакетов, которые в сумме реализуют до 64 аппаратных потоков обработки команд. Аппаратно реализованный классификатор пакетов может содержать до 32 тысяч правил, 16 тысяч из которых могут отвечать за переадресацию (forwarding). Классификатор обеспечивает обработку до 450 млн. поисковых запросов в секунду. Микропроцессор имеет 2,5 МБ внутренней памяти и три шины для работы с внешним ОЗУ.

Таблица 1 - Сравнение характеристик сетевых процессоров

Характеристика |

EZchip NP-3 |

EZchip NP-4 |

PMC-Sierra Winpath3 |

LSI APP 3110 |

|

Пропускная способность |

30 Гб/с |

100 Гб/с (50 Гб/с в дуплексном режиме) |

10 Гб/с или до 15 млн. пакетов/с |

до 2 Гб/с |

|

Вычислительные ядра |

Ядро общего назначения, специализированные ядра для обработки пакетов |

Ядро общего назначения, специализированные ядра для обработки пакетов |

2 x MIPS @ 650 MHz, 64K icache / 32 K dcache, 512 MB L2 cache (на первом ядре); 12 x RISC WinGines @ 450 MHz |

ARM 11 MP Core, 32 K icache / 64 K dcache |

|

Функциональные блоки |

Менеджеры трафика (QoS), блоки поиска в маршрутных таблицах, аппаратная реализация обработки протокола OAM |

Менеджеры трафика (QoS), блоки поиска в маршрутных таблицах, аппаратная реализация обработки протокола OAM, блок взаимодействия с внешними матрицами коммутации |

Классификатор пакетов, блок политик, блок формирования трафика, два блока для поддержки криптографии |

Классификатор пакетов, управление трафиком, акселератор обработки IPsec трафика

|

|

Интерфейсы |

10 x 1Гб/с Ethernet, 1 x 10Гб/с Ethernet, 2 x SPI 4.2 |

1 x 40 Гб/с Ethernet, совместимый с 802.3ba или 10 x XAUI (10 Гб/с); 24 ? quad-speed SGMII/1000Base-X Ethernet или 48 x tri-speed QSGMII Ethernet;

|

до 12 x Gigabit Ethernet, до 72 x Fast Ethernet, до 16 x TDM |

GMII (до 1000 Мб/с), SGMII (до 1000 Мб/с) GPIO, I?C, UART, MDIO, JTAG |

|

Размеры |

40x40 мм |

45x45 мм |

31x31 мм |

23x23 мм |

|

Техпроцесс |

90 нм |

55 нм |

— |

— |

|

Энергопотребление |

— |

35 Вт |

20 Вт |

3 Вт |

Еще одним крупным производителем сетевых процессоров для устройств доступа является компания LSI, выпускающая новое семейство коммуникационных процессоров Axxia (Axxia communication processors, ACP). Процессоры этого производителя объединяют в себе использование вычислительных ядер общего назначения с архитектурой Power, и нескольких специализированных ядер для выполнения различных задач обработки пакетов: сравнение с шаблоном, классификация, управление трафиком и др. В настоящее время LSI поставляет четыре модели сетевых процессоров: APP3100, APP3300, APP650 и APP300, которые отличаются структурой и производительностью. Технические характеристики наиболее производительного из них (APP3100) приведены в таблице 1.

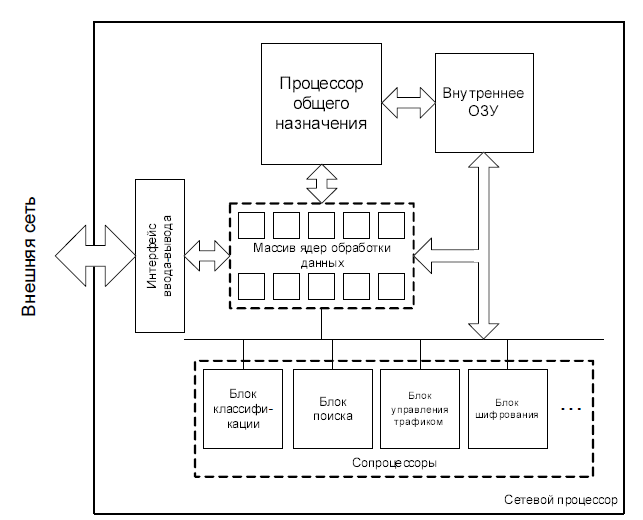

Проанализировав существующие структуры сетевых процессоров, можно представить обобщенную структуру современного сетевого процессора (см. рис. 1).

Рисунок 1 — Обобщенная структура сетевого процессора

Все представленные процессоры используют многоядерные структуры для повышения скорости обработки пакетов. Широко используются специализированные сопроцессоры и функциональные блоки для ускорения отдельных операций обработки пакетов. В общем случае сетевой процессор содержит несколько специализированных вычислительных ядер для обработки данных и ядро общего назначения для выполнения инструкций управления: обработка ошибок, сбор статистики, обновление маршрутных таблиц.

В целях увеличения скорости обработки пакетов могут использоваться специализированные сопроцессоры. Количество и функциональные возможности сопроцессоров зависят от области исполь- зования конкретной модели СП, но, в большинстве моделей присутствуют блоки управления трафиком, поиска в маршрутной таблице и блоки классификации пакетов.

Еще одним способом повышения производительности обработки пакетов является размещение на кристалле блока оперативной памяти ограниченного объема. Это ОЗУ имеет меньшее время доступа по сравнению с внешней памятью и используется для хранения временных данных, используемых в процессе обработки пакетов.

В статье проведены анализ и сравнение актуальных моделей сетевых процессоров, рассмотрены их структуры и функциональные возможности. Предложена обобщенная структура, отражающая основные направления и тенденции в разработке сетевых процессоров.