Оценка эффективности архитектур сетевых процессоров

Автор: Д.Д. Моргайлов, Ю.В. Ладыженский, М. Юнис

Источник: Информационные управляющие системы и компьютерный мониторинг – 2013 (ИУС и КМ – 2013) / Материалы IV международной научно-техническая конференция студентов, аспирантов и молодых ученых – 23-25 апреля 2013 – Донецк, ДонНТУ – 2013, С. 219-224, http://iuskm.donntu.ru/pdf/vol1/Секция%204.pdf

Аннотация

Д.Д. Моргайлов, Ю.В. Ладыженский, М. Юнис. Оценка эффективности архитектур сетевых процессоров. Описано назначение и приведена обобщенная структура сетевых процессоров. Рассмотрена и программно реализована марковская модель для оценки эффективности гетерогенных архитектур многоядерных сетевых процессоров. Исследованы зависимости показателей эффективности архитектуры от интенсивности входного потока пакетов и других параметров.

Ключевые слова: сетевой процессор, эффективность, производительность, цепи Маркова

Постановка проблемы

Сетевые процессоры (СП) в настоящее время активно используются на различных уровнях стека протоколов. Однако их главным назначением является маршрутизация высокоскоростных потоков пакетов в ядре Интернет. В условиях повышения требований к пропускной способности компьютерных сетей необходимо, чтобы обработка потоков осуществлялась со скоростью канала, к которому подключен маршрутизатор.

Кроме того, сетевые процессоры, как и процессоры общего назначения, предоставляют широкие возможности по программированию. Программируемость архитектуры, возможности параллельной и конвейерной обработки позволяют расширить области применения многоядерных СП.

Производительность сетевых процессоров полностью зависит от эффективного выбора параметров архитектуры, разработки быстрых адаптируемых алгоритмов анализа пакетов, оптимального использования аппаратных ресурсов системы. Это делает актуальной задачу разработки комплекса аналитических и имитационных моделей для исследования характеристик архитектур сетевых процессоров, а также обработки и анализа полученных оценок.

Анализ литературы

Использование моделирования позволяет изучить свойства предполагаемой архитектуры, получить оценки производительности сетевого процессора и на основании анализа экспериментальных данных выбрать оптимальные архитектурные и программные решения. В работе [1] описываются тенденции развития и функциональные возможности сетевых процессоров, приведена их обобщенная архитектура.

Задачи, критерии и проблемы проектирования СП рассмотрены в [2-4]. Выделяется несколько направлений в моделировании СП. Методики и подходы к моделированию многоядерных сетевых процессоров, а также модели архитектур предложены в [5-8]. К настоящему времени не существует единой методологии проектирования СП.

Цель статьи – оценка эффективности гетерогенной архитектуры сетевых процессоров с использованием аналитической модели.

Структура сетевых процессоров

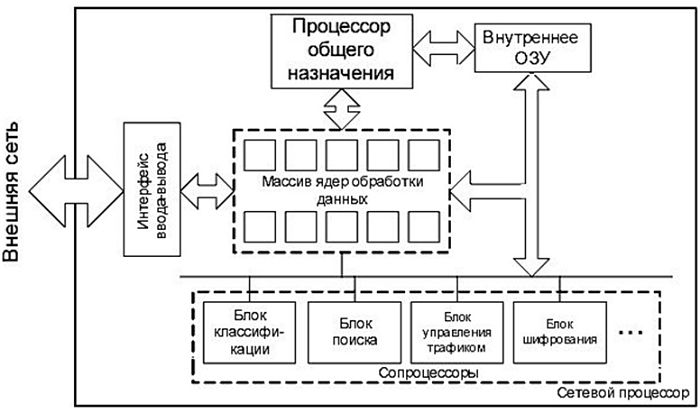

Типичный сетевой процессор состоит из множества программируемых пакетных процессоров (ядер обработки данных) с высоко параллельной архитектурой, программируемого процессора общего назначения (центрального процессора), аппаратных сопроцессоров (ускорителей) для обычных сетевых операций, высокоскоростных интерфейсов памяти и высокоскоростных сетевых интерфейсов [1] (рисунок 1).

Рисунок 1 – Обобщенная архитектура сетевого процессора

Центральный процессор предназначен для выполнения инструкций управления: обработка ошибок, сбор статистики, обновление маршрутных таблиц. Пакетные процессоры имеют ограниченный набор команд и используются для быстрой параллельной и конвейерной реализации алгоритмов пересылки, фильтрации, работы с заголовками, преобразования протоколов и контроля безопасности. Сопроцессоры предоставляют специфические функции для выполнения общих задач, поэтому их аппаратная реализация ускоряет обработку данных. Количество и функциональные возможности сопроцессоров зависят от области использования конкретной модели сетевого процессора.

Существует несколько возможных схем распределения потоков по процессорным элементам. Однако наиболее эффективным является гетерогенное распределение, при котором трафик поступает на процессоры равномерно. Потоки процессора при этом принадлежат к разным типам и, предположительно, принимают равную нагрузку при обработке пакетов.

Преимуществами традиционных многопоточных-многопроцессорных архитектур сетевых процессоров являются значительное увеличение вычислительной мощности путем соединения нескольких процессорных элементов, разделение ограниченного ресурса памяти с другими элементами и формирование распределенной общей памяти, снижение накладных расходов на доступ к памяти за счет многопоточности [8].

Подсистема памяти, как правило, является узким местом системы ввиду длительных задержек доступа к ней. Однако современный уровень информационных технологий делает возможным расположить несколько процессоров и блоков памяти на одном чипе, что значительно снижает эту задержку.

Реализация марковской модели мультипроцессорного СП

Модель системы СП состоит из I процессоров, каждый из которых имеет J потоков [8]. Когда пакет поступает в свободный поток, данный поток помещается в очередь готовых к выполнению потоков процессора или переходит в активное состояние, если в текущий момент на процессоре нет активного потока. Поток может запрашивать доступ к памяти, например, для работы с дескриптором пакета или маршрутной таблицей. После обслуживания в памяти поток помещается в очередь готовых к выполнению либо вновь поступает на процессор, если данная очередь пуста. Обычно поток снова становится свободным после того, как пакет будет обслужен и передан следующему потоку. Однако если следующий поток занят обслуживанием пакета, текущий поток переходит в состояние «завершен».

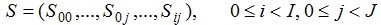

Пространство состояний модели есть:

где  представляет собой состояние

представляет собой состояние  j-го потока i-го процессора.

j-го потока i-го процессора.

Строится непрерывная марковская модель для расчета вероятностей состояний и характеристик производительности СП. Моделирование выполняется только для множества достижимых состояний, что существенно сокращает затраты памяти и время моделирования.

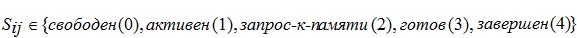

Пример системы на двух процессорах показан на рисунке 2.

Рисунок 2 – Схема моделируемой системы на двух процессорах

Здесь  – интенсивность поступления пакетов на процессор,

– интенсивность поступления пакетов на процессор,  –

интенсивность обслуживания j-го потока,

–

интенсивность обслуживания j-го потока,  – интенсивность обращения к

памяти для j-го потока, m – интенсивность обслуживания запросов подсистемой памяти, h – длина очереди запросов к памяти; R, S, T – выполняемые над пакетом операции.

– интенсивность обращения к

памяти для j-го потока, m – интенсивность обслуживания запросов подсистемой памяти, h – длина очереди запросов к памяти; R, S, T – выполняемые над пакетом операции.

Интенсивности с одинаковым индексом потока на всех процессорах характеризуется равными значениями в связи с гомогенным характером данных потоков.

В качестве механизма обслуживания очередей запросов к памяти и готовых к выполнению потоков была выбрана дисциплина RSS (Random Selection for Service). Это позволило значительно сузить пространство состояний, не снижая при этом корректность аналитических результатов.

Изменение состояния системы происходит, когда свое состояние изменяют один или более потоков. Такой переход осуществляется при возникновении активизирующего события на одном из потоков каждого процессора. Остальные потоки под действием активизирующего события выполняют подчиненный переход.

Переход считается действительным, если на

процессоре возникает только одно активизирующее событие, которое включает в

себя активизирующий переход и возможно несколько связанных с ним подчиненных

переходов. Например, активизирующими являются переходы, связанные с

поступлением на обслуживание нового пакета:  и

и  .

.

После расчета вероятностей состояний вычисляются показатели эффективности: среднее число работающих процессоров, коэффициенты использования процессора и памяти, среднее число обращений к памяти, среднее число готовых к выполнению потоков на процессоре.

Анализ эффективности гетерогенной архитектуры сетевых процессоров.

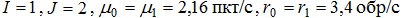

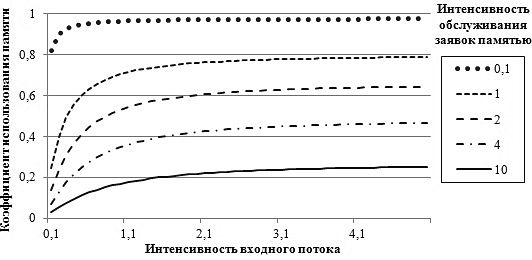

Пусть моделируемая архитектура задается следующими параметрами:

. На

рисунках 3 и 4 приведены зависимости

характеристик загрузки памяти и процессоров от интенсивности потока пакетов и

производительности памяти СП для указанных значений исходных данных.

. На

рисунках 3 и 4 приведены зависимости

характеристик загрузки памяти и процессоров от интенсивности потока пакетов и

производительности памяти СП для указанных значений исходных данных.

Качество роста исследуемых оценок определяется величиной интенсивности обслуживания заявок подсистемой памяти. При малых ее значениях показатели эффективности быстрее достигают устойчивости, которая на практике выражается в наличии существенной доли отказов в обслуживании. В то же время увеличение производительности памяти приводит к снижению коэффициента ее использования и возрастанию загрузки процессора. Как следствие, пропускная способность системы увеличивается.

Рисунок 3 – Изменение коэффициента использования памяти

Рисунок 4 – Изменение среднего числа работающих процессоров

Таким образом, полученные графики подтверждают тезис о том, что подсистема памяти является «узким местом» рассматриваемой архитектуры.

Выводы

Описано назначение и приведена обобщенная структура сетевых процессоров. Рассмотрена и программно реализована марковская модель для оценки эффективности гетерогенных архитектур многоядерных сетевых процессоров. Исследованы зависимости показателей эффективности архитектуры от интенсивности входного потока пакетов и других параметров.

Результаты проведенных экспериментов показывают, что эффективность сетевого процессора в значительной мере зависит от производительности подсистемы памяти. Ограничение ресурсов памяти может привести к снижению коэффициента загрузки процессоров и проявляться в появлении отказов системы при сравнительно небольших интенсивностях входного потока.

Список литературы

- Грищенко В.И., Ладыженский Ю.В., Юнис М. Основные направления развития современных сетевых процессоров / Д.Д. Моргайлов, Ю.В. Ладыженский, М. Юнис // Наукові праці ДонНТУ. – Донецк, 2011. – (Серия «Інформатика, кібернетика та обчислювальна техніка»). – № 14 (188). – С. 123-127.

- Кучерявый Е.А. Управление трафиком и качество обслуживания в сети Интернет. – СПб.: Наука и Техника, 2004. – 336 с.

- Юнис М., Ладыженский Ю.В. Архитектуры и тенденции развития сетевых процессоров / М. Юнис, Ю.В. Ладыженский // Материалы II всеукраинской научно-технической конференции «Информационные управляющие системы и технологии и компьютерный мониторинг – 2011». – Донецк, 2011. – С. 259-262.

- Орлов С.А., Цилькер Б.Я. Организация ЭВМ и систем. 2-е изд. – СПб.: Питер, 2011. – 688 с.

- Грищенко В.И., Ладыженский Ю.В., Юнис М. Влияние выделенного кэша команд на производительность сетевого процессора / В.И. Грищенко, Ю.В. Ладыженский, М. Юнис // Наукові праці ДонНТУ. – Донецк, 2011. – (Серия «Інформатика, кібернетика та обчислювальна техніка»). – № 13 (185). – С. 85-91.

- Грищенко В.И., Ладыженский Ю.В.. Моделирование маршрутизаторов на многоядерных сетевых процесорах / В.И. Грищенко, Ю.В. Ладыженский // Наукові праці ДонНТУ. – Донецк, 2010. – (Серия «Інформатика, кібернетика та обчислювальна техніка»). – № 12 (165). – С. 169-176.

- Ali F.H., Ahmed O.F. Modeling and Analysis of IXP425 Network Processor / F.H. Ali, O.F. Ahmed // Al-Rafadain Engineering Journal. – 2012. – vol. 20 (2). – pp. 116-130.

- Lin Y.-N., Lin Y.-D., Lai Y.-C. Thread Allocation in CMP-based Multithreaded Network Processors / Y.-N. Lin, Y.-D. Lin, Y.-C. Lai // Parallel Computing. – 2010. – vol. 36 (2-3). – pp. 104-116.