Программный комплекс для исследования производительности сетевых процессоров

Автор: Ю.В. Ладыженский, Д.Д. Моргайлов, М. Юнис

Источник: Статья принята к печати в научном журнале «Известия ЮФУ. Технические науки». – 2013. – № 5.

Аннотация

Ю.В. Ладыженский, Д.Д. Моргайлов, М. Юнис. Программный комплекс для исследования производительности сетевых процессоров. Рассматривается проблема создания высокопроизводительных специализированных сетевых процессоров и их программного обеспечения для обработки потоков данных на разных уровнях стека протоколов и для маршрутизации потоков пакетов в ядре Интернета. Описана обобщенная схема, проанализированы требования, основные задачи проектирования и перспективные пути повышения эффективности сетевых процессоров. Разработана архитектура программного комплекса для исследования производительности сетевых процессоров. Комплекс предназначен для расчета показателей эффективности многопоточных-многопроцессорных сетевых процессоров. В состав программного комплекса входит набор аналитических и имитационных моделей, обеспечивающих построение зависимостей показателей эффективности архитектуры от интенсивности входного потока процессора и других параметров. Приведены примеры результатов расчетов.

Ключевые слова: сетевой процессор, программный комплекс, эффективность, производительность, модели.

Y.V. Ladyzhensky, D.D. Morgajlov, M. Younis. Software solution for performance analysis of network processors. A problem of high performance ad-hoc network processors hardware and software development is considered. Network processors are used for processing data flows on different levels of a protocol stack and for routing of packet flows in Internet core. A generalized structure of network processor is described, requirements, main tasks of development and prospective ways for network processor efficiency increasing are analyzed. Software system architecture to research network processor productivity is developed. The system is intended for calculating efficiency indexes of multithread and multicore network processors. Software system consists of analytical and simulating models for obtaining architecture efficiency indexes depending of processor input packet flow rates and other parameters. Examples of calculation results are given.

Keywords: network processor, software system, efficiency, productivity, simulations.

Введение

Требования к пропускной способности компьютерных сетей неуклонно повышаются. Рост интенсивности обмена данными, необходимость обеспечения высокого качества обслуживания сетевых приложений, учет периодически возникающих задержек в передаче данных и потери пакетов при недостаточной производительности и ограниченных ресурсах памяти делают процессоры общего назначения неэффективными для маршрутизации и управления сетью. Это увеличивает актуальность проблемы создания высокопроизводительных специализированных сетевых процессоров и их программного обеспечения для обработки потоков данных на разных уровнях стека протоколов и для маршрутизации огромных высокоскоростных потоков пакетов в ядре Интернета.

Особенности сетевых процессоров

Сетевые процессоры представляют собой устройства, архитектура которых оптимизирована для использования в сетевых системах, обеспечения устойчивого режима обработки пакетов и ориентирована на выполнение узкого круга задач. Основным требованием к СП является способность обрабатывать поток пакетов со скоростью канала, к которому подключен маршрутизатор [1, 2].

Ключевые операции сетевой обработки (управление очередями, вычисление контрольных сумм, поиск в маршрутной таблице, анализ заголовков пакетов) реализуются в сетевых процессорах аппаратно. Кроме того, СП предоставляют широкие возможности для программирования сложных сетевых приложений на языке высокого уровня и ассемблера [3]. Большинство процессоров использует многоядерные структуры для повышения скорости обработки.

В качестве основных отличий сетевых процессоров от процессоров общего назначения важно отметить следующие: набор инструкций большинства СП основан на RISC-архитектуре, архитектуры сетевых процессоров содержат дополнительные инструкции для битовых операций, расчета контрольных сумм и операций поиска, СП могут содержать дополнительные функциональные блоки, реализующие задачи обработки пакетов.

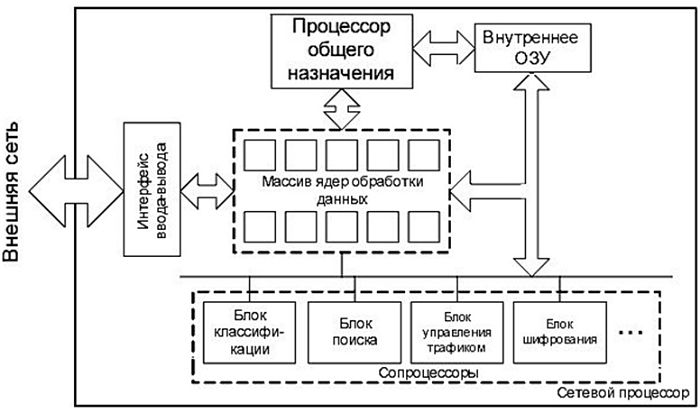

Типичный сетевой процессор состоит из множества программируемых пакетных процессоров (ядер обработки данных) с высоко параллельной архитектурой, программируемого процессора общего назначения, аппаратных сопроцессоров (ускорителей) для обычных сетевых операций, высокоскоростных интерфейсов памяти и высокоскоростных сетевых интерфейсов [4] (рисунок 1).

Рисунок 1 – Обобщенная архитектура сетевого процессора

Пакетные процессоры имеют ограниченный набор команд и используются для быстрой параллельной и конвейерной реализации алгоритмов пересылки, фильтрации, работы с заголовками, преобразования протоколов и контроля безопасности. Сопроцессоры предоставляют специфические функции для выполнения общих задач, поэтому их аппаратная реализация ускоряет обработку данных. Количество и функциональные возможности сопроцессоров зависят от области использования конкретной модели сетевого процессора [4].

Преимуществами традиционных многопоточных-многопроцессорных архитектур сетевых процессоров являются значительное увеличение вычислительной мощности путем соединения нескольких процессорных элементов, разделение ограниченного ресурса памяти с другими элементами и формирование распределенной общей памяти, снижение накладных расходов на доступ к памяти за счет многопоточности [5].

Подсистема памяти, как правило, является узким местом системы ввиду длительных задержек доступа к ней. Однако современный уровень информационных технологий делает возможным расположить несколько процессоров и блоков памяти на одном чипе, что значительно снижает эту задержку.

Проблемы проектирования сетевых процессоров

Сетевые компьютерные системы проектируются по критериям производительности и функциональных возможностей в условиях ограничений на стоимость, размеры и время изготовления для выхода на рынок [6, 7, 8].

Разрабатываемые системы должны быть масштабируемыми, универсальными и гибкими. В ходе проектирования необходимо учитывать быстрые изменения в рыночных тенденциях, применяемых технологиях и технических требованиях к выпускаемой системе.

Чтобы СП обладали необходимой производительностью, задачи обработки пакетов должны быть детально проанализированы, выполнена их функциональная декомпозиция, сделаны оценки их временной и емкостной сложности. Для наиболее затратных по времени задач в архитектуру сетевых процессоров следует включать проблемно ориентированные блоки. Использование сетевых процессоров оказывается экономически выгодным в системах, содержащих много сетевых интерфейсов, потоки пакетов через которые обрабатываются мультипроцессорными устройствами.

Основными проблемами проектирования СП являются определение наиболее важных задач обработки пакетов для сетевых протоколов, определение критериев оптимизации архитектур процессоров, определение состава, структуры и способов взаимодействия функциональных блоков для повышения быстродействия, выбор эффективных интерфейсов ввода-вывода, определение оптимальных технологий и объемов памяти программ и памяти данных, выбор способов реализации функций сетевых протоколов (аппаратная и/или, программная реализация, применение проблемно ориентированных интерфейсных СБИС или сопроцессоров), разработка средств автоматизации программирования (языки, компиляторы, компоновщики, загрузчики, библиотеки).

Архитектура программного комплекса для исследования СП

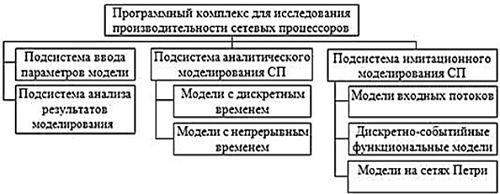

Архитектура разработанного программного комплекса для исследования производительности сетевых процессоров приведена на рисунке 2.

Рисунок 2 – Архитектура программного комплекса

Комплекс предназначен для расчета показателей эффективности многопоточных-многопроцессорных сетевых процессоров с заданным числом процессорных элементов и потоков. В состав программного комплекса входит набор аналитических и имитационных моделей СП, обеспечивающих построение зависимостей показателей эффективности архитектуры от интенсивности входного потока процессора и других параметров.

Реализация марковской модели мультипроцессорной системы СП

Модель системы состоит из I процессоров, каждый из которых имеет J потоков [5]. Когда пакет поступает в свободный поток, данный поток помещается в очередь готовых к выполнению потоков процессора или переходит в активное состояние, если в текущий момент на процессоре нет активного потока. Поток может запрашивать доступ к памяти, например, для работы с дескриптором пакета или маршрутной таблицей. После обслуживания в памяти поток помещается в очередь готовых к выполнению либо вновь поступает на процессор, если данная очередь пуста. Обычно поток снова становится свободным после того, как пакет будет обслужен и передан следующему потоку. Однако если следующий поток занят обслуживанием пакета, текущий поток переходит в состояние «завершен».

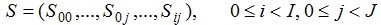

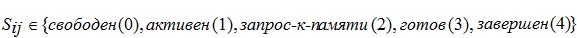

Пространство состояний модели есть:

где  представляет собой состояние

представляет собой состояние  j-го потока i-го процессора.

j-го потока i-го процессора.

Строится непрерывная марковская модель для расчета вероятностей состояний и характеристик производительности СП. Моделирование выполняется только для множества достижимых состояний, что существенно сокращает затраты памяти и время моделирования.

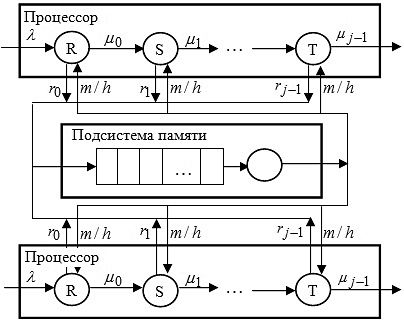

Пример моделируемой системы на двух процессорах показан на рисунке 3.

Рисунок 3 – Схема моделируемой системы на двух процессорах

Здесь  – интенсивность поступления пакетов на процессор,

– интенсивность поступления пакетов на процессор,  –

интенсивность обслуживания j-го потока,

–

интенсивность обслуживания j-го потока,  – интенсивность обращения к

памяти для j-го потока, m – интенсивность обслуживания запросов подсистемой памяти, h – длина очереди запросов к памяти; R, S, T – выполняемые над пакетом операции.

– интенсивность обращения к

памяти для j-го потока, m – интенсивность обслуживания запросов подсистемой памяти, h – длина очереди запросов к памяти; R, S, T – выполняемые над пакетом операции.

После расчета вероятностей состояний вычисляются показатели эффективности: среднее число работающих процессоров, коэффициенты использования процессора и памяти, среднее число обращений к памяти, среднее число готовых к выполнению потоков на процессоре.

Анализ эффективности гетерогенной архитектуры сетевых процессоров

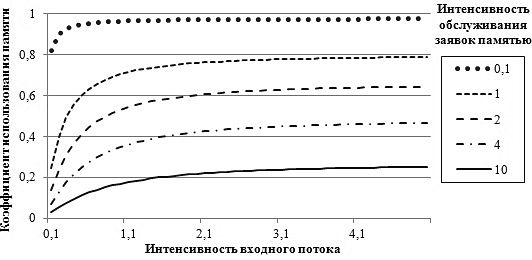

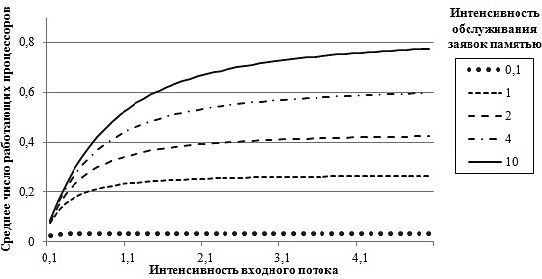

На рисунках 4 и 5 приведены примеры зависимостей характеристик загрузки памяти и процессоров от интенсивности потока пакетов и производительности памяти СП.

Рисунок 4 – Изменение коэффициента использования памяти

Рисунок 5 – Изменение среднего числа работающих процессоров

Выводы

Рассмотрена проблема создания высокопроизводительных специализированных сетевых процессоров и их программного обеспечения. Описана обобщенная схема, проанализированы требования, основные задачи проектирования и перспективные пути повышения эффективности сетевых процессоров. Разработан программный комплекс для исследования производительности сетевых процессоров. Комплекс предназначен для расчета показателей эффективности многопоточных многопроцессорных сетевых процессоров, включает набор аналитических и имитационных моделей. Приведены примеры моделей и результатов расчетов.

Библиографический список

- Сетевые процессоры [Электронный ресурс]. Режим доступа: http://chernykh.net/content/view/432/639/ Thursday, 27 December 2012 19:11:47

- Грищенко В.И., Ладыженский Ю.В., Юнис М. Основные направления развития современных сетевых процессоров / Д.Д. Моргайлов, Ю.В. Ладыженский, М. Юнис // Наукові праці ДонНТУ. – Донецк, 2011. – (Серия «Інформатика, кібернетика та обчислювальна техніка»). – № 14 (188). – С. 123-127.

- Gries M., Kulkarni C., Sauer C., Keutzer K. Exploring Trade-offs in Performance and Programmability of Processing Element Topologies for Network Processors / M. Gries, C. Kulkarni, C. Sauer, K. Keutzer // Network Processor Design: Issues and Practices. – 2003. – vol. 2. – pp. 133-158.

- Грищенко В.И., Ладыженский Ю.В, Юнис М. Перспективные архитектуры и тенденции развития современных сетевых процессоров / В.И. Грищенко, Ю.В. Ладыженский, М. Юнис // Материалы IV международной научно-технической конференции «Моделирование и компьютерная графика – 2011». – Донецк, 2011. – С. 259-262.

- Lin Y.-N., Lin Y.-D., Lai Y.-C. Thread Allocation in CMP-based Multithreaded Network Processors / Y.-N. Lin, Y.-D. Lin, Y.-C. Lai // Parallel Computing. – 2010. – vol. 36 (2-3). – pp. 104-116.

- Кучерявый Е.А. Управление трафиком и качество обслуживания в сети Интернет. – СПб.: Наука и Техника, 2004. – 336 с.

- Юнис М., Ладыженский Ю.В. Архитектуры и тенденции развития сетевых процессоров / М. Юнис, Ю.В. Ладыженский // Материалы II всеукраинской научно-технической конференции «Информационные управляющие системы и технологии и компьютерный мониторинг – 2011». – Донецк, 2011. – С. 259-262.

- Орлов С.А., Цилькер Б.Я. Организация ЭВМ и систем. 2-е изд. – СПб.: Питер, 2011. – 688 с.