Аннотация

Святный В. А., Иванов Ю. А. Управление циклом реального времени встроенных систем при моделировании Исследованы вопросы реализации алгоритмов планирования и управления систем моделирования на базе микроконтроллерных систем. Получены задержки при переключении и запуске процессов для NEEK. Проведено сравнение характера реактивности данной системы со стандартным цифровым процессором.

Введение

Средства модельной поддержки и сопровождения разработок систем управления критичных по безопасности функционирования сложных динамических объектов во всех сферах человеческой деятельности становятся решающим фактором качества и конкурентоспособности проектов в аэрокосмическом комплексе, химических технологиях, спутниковой, инерционной, радионавигации и др.

Одним из перспективных направлений создания систем моделирования реального времени, в том числе и полунатурных, является разработка их на основе современных микроконтроллерных систем, поскольку их архитектура имеет ряд достоинств: высокая производительность, высокий уровень надежности, портативность, относительная дешевизна.

Организация цикла реального времени в системе моделирования

Микроконтроллерная система должна принимать информацию от объекта, преобразовывать ее в форму, удобную для хранения и обработки, обрабатывать по заданным алгоритмам и посылать результаты обратно по информационным каналам к объекту. Этот набор действий выполняется циклически на протяжении всего времени моделирования и является циклом реального времени.

Особенностью цикла есть безусловное требование к реактивности действий, которые бы отвечали заданным критериям реального времени исполнения. Таким образом, программно-аппаратные затраты времени, возникающие при передаче информации и работе планировщика в цикле реального времени, должны быть минимизированы.

Модель вычислительного процесса предполагает выполнение следующих действий: посредством датчиков в систему моделирования вводятся вычисляемые параметры Z = [z1,z2,...,zn]; их количество строго определено и не меняется на протяжении цикла моделирования; вычисление i-параметра должно быть обязательно выполнено за период Ti; задачи выполняются за время ti, которое определено на этапе построения модели.

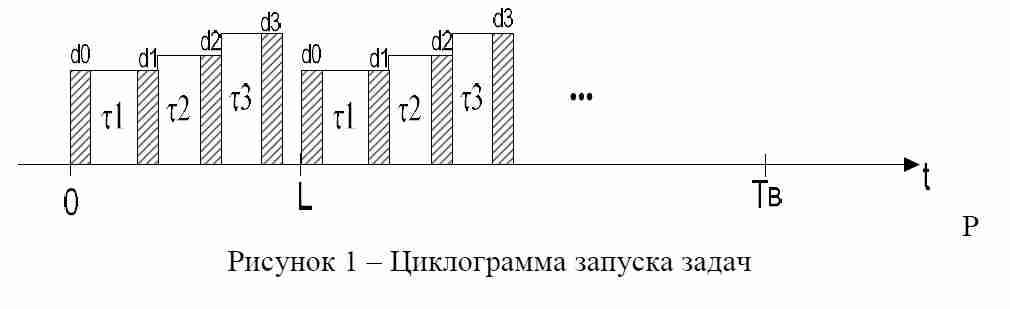

Большинство существующих алгоритмов управления циклом реального времени не учитывают многочастотность моделируемого объекта. В работах [1] и [2] предложены алгоритмы планирования вычислений для исследования многочастотных задач. Теоретические вопросы существования циклического расписания были рассмотрены ранее в [3], где сформулированы критерии существования цикла реального времени. Рассмотрим применение алгоритма равномерного планирования запуска задач согласно требуемых частот выполнения [4] для разработки диспетчера запуска задача микроконтроллерной системы. Особенностью предложенного алгоритма управления является одинаковое по времени вычисление каждой переменной моделирования на каждом из циклов реального времени. Циклограмма реального времени представляет размещение времен и порядок выполнения задач (ti), задержек на их запуск и переключение между задачами (di) (рис. 1). Каждая вычисляемая переменная занимает (L*ti)/Ti времени цикла.

Для предложенного алгоритма условие существования цикла реального времени будет описываться условием

где

– участок, на котором будет выполнена часть каждой задачи.

Таким образом, согласно размещению циклограммы на оси времени затраты диспетчеризации задач td при данной организации вычислительного процесса в каждом периоде L составят

где d0 – время, необходимое для заупска первой задачи цикла, di – время переключения между задачами. Тогда за все время выполнения Tb на диспетчеризацию будет затрачено:

Если считать время переключения с одной задачи на другую одинаковым, поскольку используется единый механизм переключения, то суммарное время на диспетчеризацию будет составлять

Отсюда следует, что важно исследовать параметр d для микроконтроллерной системы.

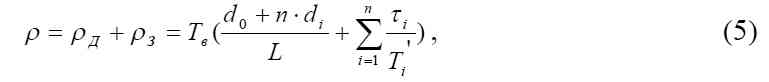

Одновременно с этим из (1) и (4) может быть определно полное значение нагрузки процессора p на периоде выполнения как сумма затрат времени на диспетчеризацию и вычисления:

где T'i – приведенный период вычисления к условию

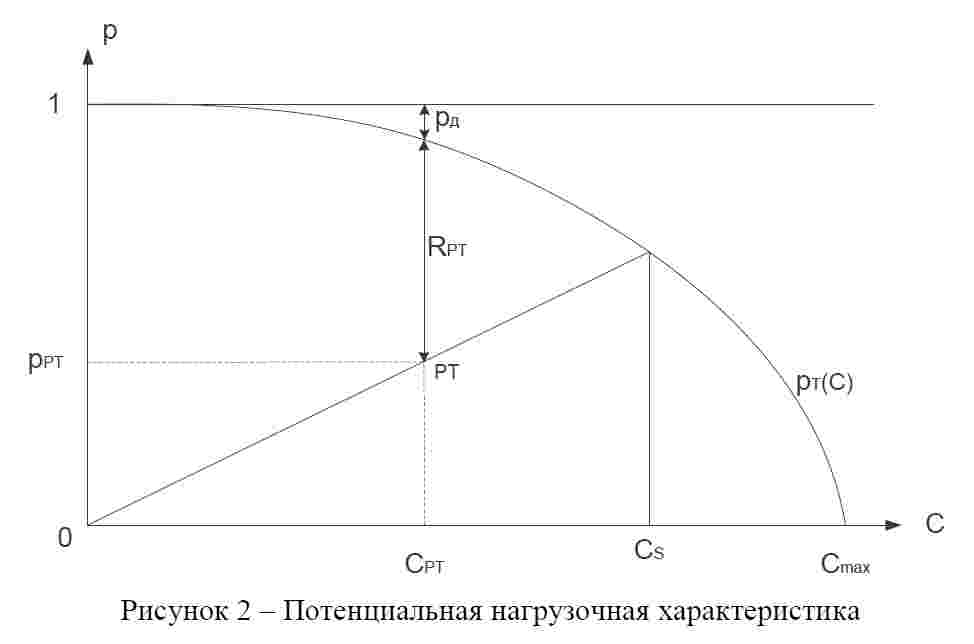

Оценка эффективности данной организации цикла реального времени может быть определена как максимально допустимое значение функции (5), представляющей потенциальную нагрузочную характеристику (ПНХ) [1]. Рабочему режиму системы моделирования на плоскости характеристик нагрузки можно поставить в соответствие точку с координатами:

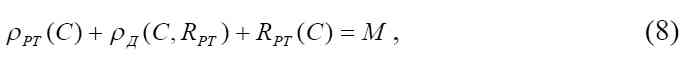

где Cpt – среднее значение интенсивности запуска задач; Ppt – средняя загрузка процессора задачами. Эта точка называется рабочей точкой (РТ). Величины Ct и Pt , которые стоят под знаком математического ожидания в (6) и (7), характеризуют параметры рабочей нагрузки процессора. Исходя из этого, ПНХ можно определить как траекторию гранично допустимых положений РТ (рис.2) [1]. Таким образом, для каждого значения интенсивности C справедливо уравнение, которое характеризует отношение затрат процессорного времени

где C – текущая абсцисса РТ; Ppt (C) – траектория РТ; Pd (C, Rpt) – затраты на работу диспетчера цикла реального времени системы моделирования.

Для каждого значения C РТ достигает своего граничного значения при Rpt (C) = 0 и тогда уравнение (8) примет вид (5).

Из уравнения ПНХ (8) следует, что одним из направлений повышения эффективности вычислительного процесса является оптимизации диспетчеризации, т.е. уменьшения использования на нее процессорных ресурсов. Применимо к данной задаче оптимизация предполагает уменьшение задержек d0 и di в (5).

Исследование динамических характеристик встроенных систем

Для исследования управления цилом реального времени был выбран отладочный FPGA-комплекс «NIOS II Embedded Evaluation Kit» (NEEK), так как он удовлетворяет основным требованиям к проектированию подсистем нижнего уровня [2].

Было проведено исследования NEEK и были разработаны тестовые программы для получения экспериментальных значений величин d0 и di. Разработка была проведена на базе встроенной операционной системы реального времени MicroC/OS-II, многозадачность ядра которой оптимизирована для микроконтроллерных систем.

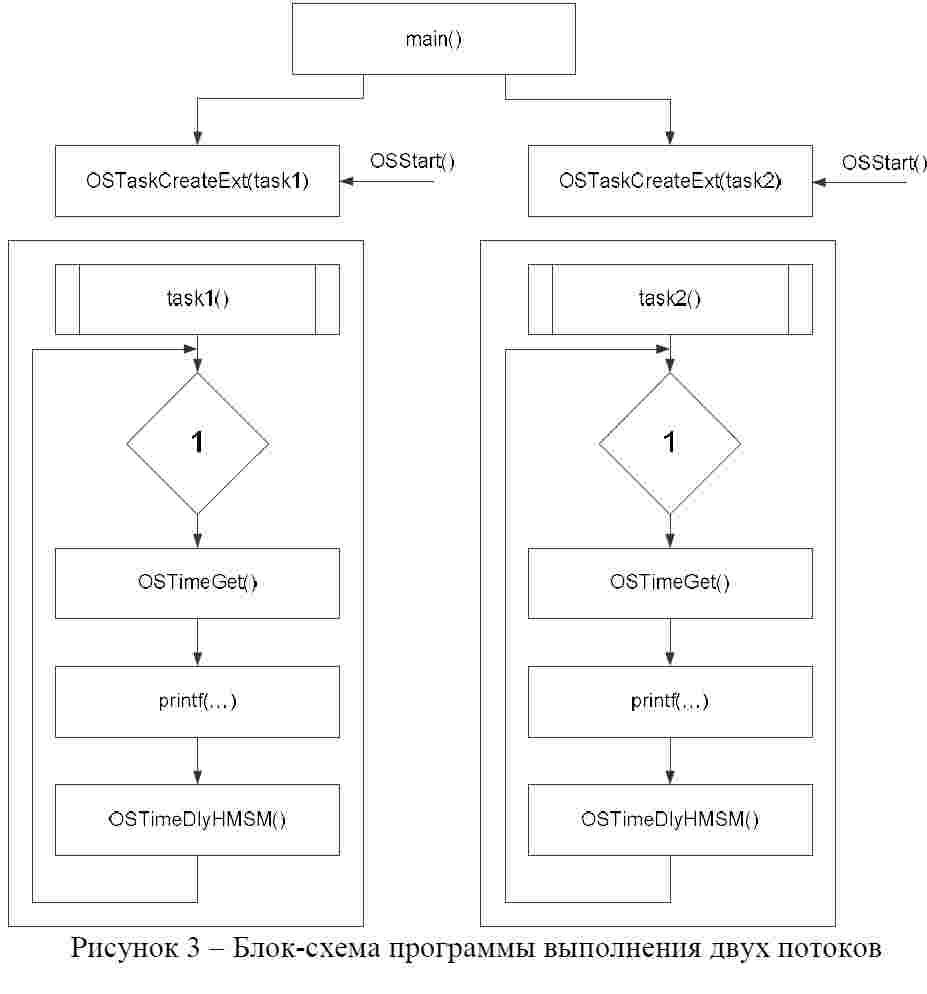

Эксперименты были выполнены с двумя типами программ. Во-первых, разработана тестовая программа, состоящая из двух задач, которые имеют идентичные настройки и запускаются синхронно. Блок-схема программы приведена на рис. 3. Функции задач представляют собой бесконечный цикл с небольшой задержкой и выводом текущего значения счетчика тактов.

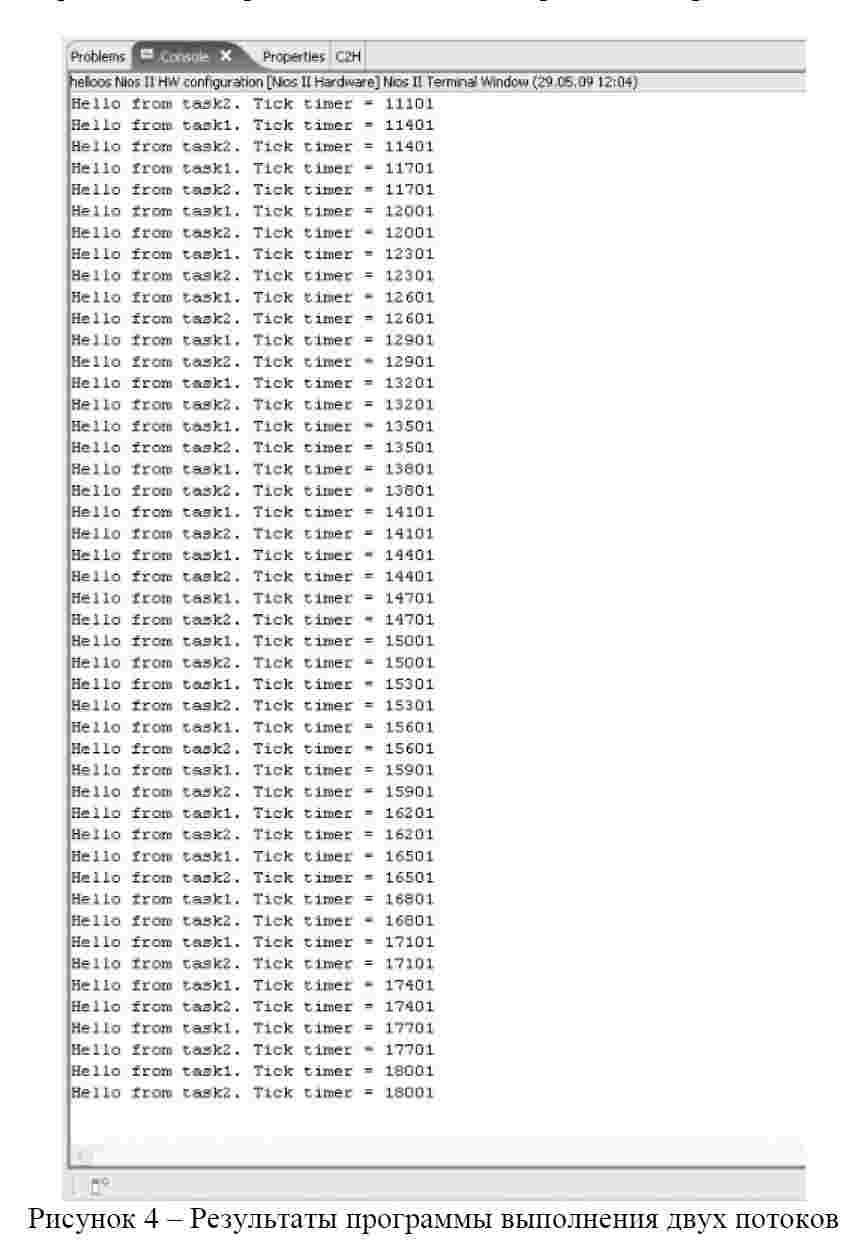

По результатам выполнения (фрагмент представлен на рис. 4), можно сделать вывод о правильности функционирования мультизадачной системы. Задачи исполнялись с одинаковым периодом 3с, при этом обе задачи получали управления в один такт системного времени, что свидетельствует о времени переключения между потоками меньше такта системного таймера. Это может быть объяснено спецификой SoPC-процессора и оптимизированностью системы реального времени.

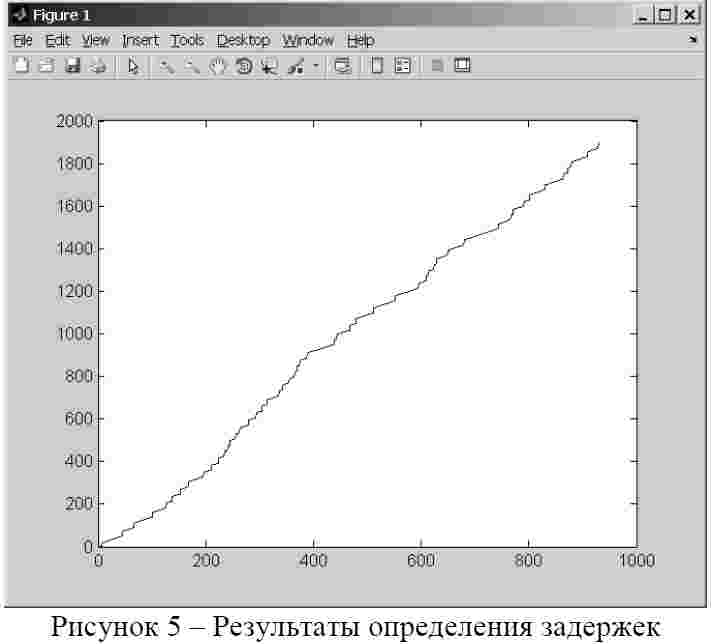

Для определения задержки, вносимой функциями измерения времени и подготовки задач, была разработана программа, которая аналогична первой задаче, но состоит из одной задачи и содержит минимально допустимую задержку, равную 1 мс. Были получены результаты вида: Tick timer = 1 … Tick coun timer = 1895 – всего 983 вычисления. Характер изменения времени для данного эксперимента иллюстрирует рис. 5.

На графике по оси Y отображена задержка, которая отвечает і-му вызову задачи, что отображено на оси Х. Безусловно, на линии графика есть определенные перепады, которые можно объяснить влиянием контроля MicrioC/OS-II и HAL. Но этот график имеет более линейный вид, а также не содержит резких скачков, характерных для аналогичных исследований различных операционных систем персонального компьютера [5].

Проведенные эксперименты показали, что в отдельных случаях задержка на переключение процессов может составить не более 1 мс. Поскольку в задачах систем реального времени самое главное – это гарантия временных интервалов, предложено для системы NEEK рассматривать наихудшую ситуацию, тогда (5) примет вид (мс):

олученная величина задержки является малой относительно тактовой частоты системного таймера микроконтроллерной системы. Таким образом, данные системы для исследуемых задач моделирования можно считать эффективными, что объясняется ПНХ для NEEK. За счет уменьшения величины pd (C, Rpt) в (8) кривая нагрузочной характеристики будет смещена вверх и вправо, что свидетельствует о более эффективной организации вычислительного процесса при равномерном алгоритме планирования цикла реального времени.

Управление циклом реального времени микроконтроллерной системы

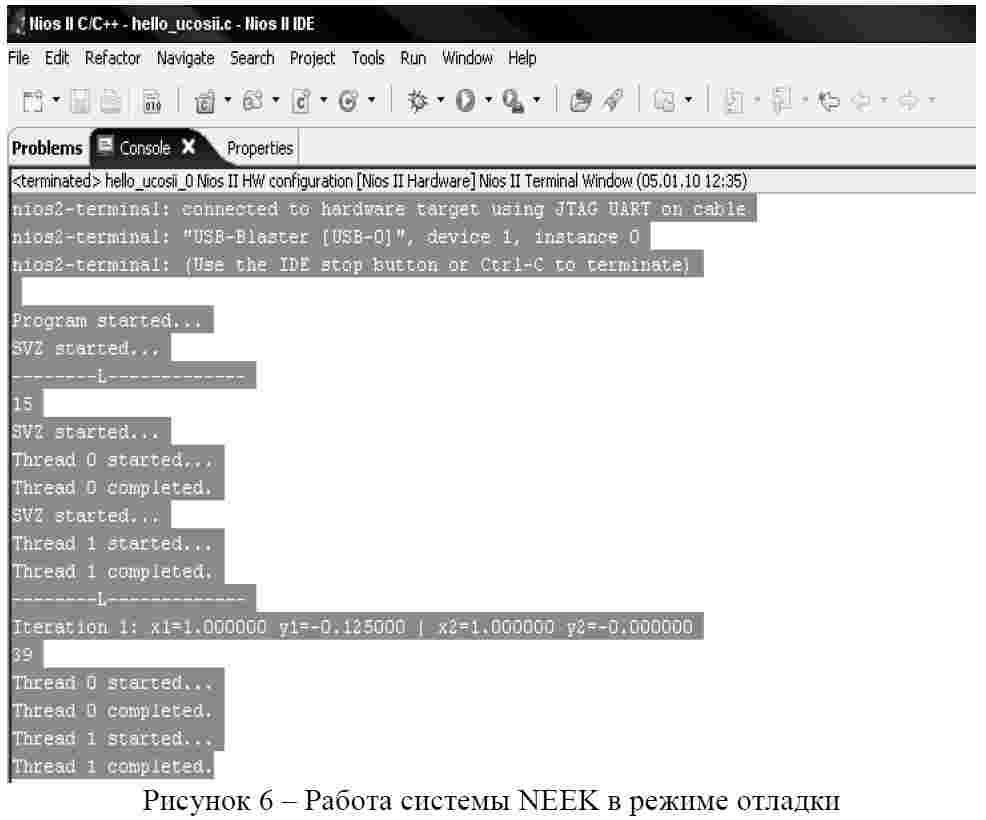

Опираясь на полученные данные, была разработана программа диспетчеризации цикла реального времени для системы NEEK (рис. 6).

В программе использованы функции системных библиотек:

- OSTaskCreateExt. Функция создает задачу с установленными параметрами: адресом функции обработки, памятью задачи, приоритетом, порядковым номером, размером стека, указателем на блок управления задачами и дополнительными опциями.

- OSStart. Функция запускает на исполнение систему.

- OSTimeGet. Функция возвращает значения 32-битного счетчика тиков системного таймера.

- OSTimeDlyHMSM. Функция устанавливает задержку на необходимое количество часов, минут, секунд, миллисекунд.

Выполнены отладка и профилирование программы управления циклом реального времени.

Для исследования алгоритма планирования и управления вычислениями было использовано численное интегрирование системы дифференциальных уравнений, описывающих модель гармонического осциллятора:

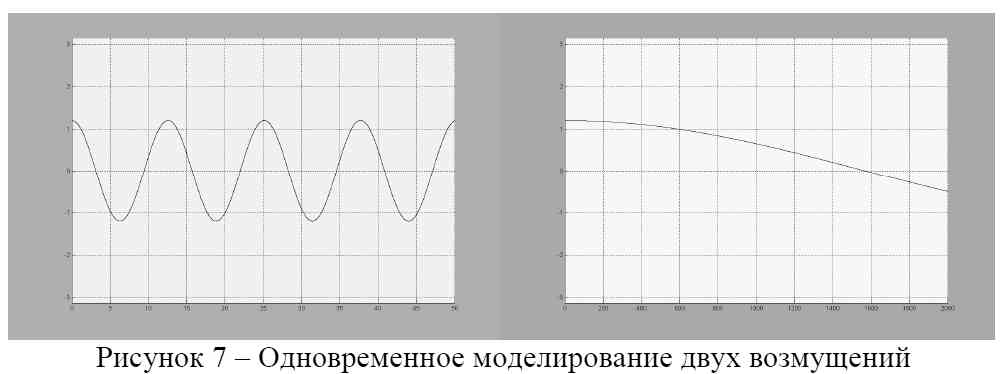

Для моделирования двух гармонических осцилляторов с разными частотами был использован численный алгоритм Эйлера. Один из осцилляторов моделировался программным потоком с частотой 0,5 рад/сек, а второй – другим потоком с частотой 0,001 рад/сек (рис. 7), которые соответствуют частотам реально возможных сигналов возмущений, характерных для системы проветривания угольной шахты.

Выводы

В статье исследована возможность создания средств моделирования на базе микроконтроллерных систем. Получены временные задержки при переключении и запуске процессов для NEEK, которые составили 1 мс. Реактивность данной системы по сравнению со стандартным цифровым процессором отличается линейностью и отсутствием резких перепадов.

Для микроконтроллерной системы разработана программа управления вычислительным процессом и протестирована на примере модели гармонического осциллятора. Анализ ПНХ показывает, что применение микроконтроллерных систем для реализации полунатурных средств моделирования является эффективным.

Одним из направлений развития результатов работы является создание на основе универсального планировщика библиотеки циклов реального времени различных динамических систем, опирающихся на технологии FPGA и SOPC-процессоров.

Список литературы

1. Виттих В.А. Оптимизация бортовых систем сбора и обработки данных / В.А. Виттих, В.А. Цыбатов. – М.:Наука,1985. – 175 с.:ил., с. 20-25.

2. П’явченко О.Н. Розподілені мікрокомп'ютерні системи збору й обробки інформації. Навчальний посібник. Частина 1 / О.Н.П’явченко. – ТРТУ.: Таганрог, 2007.

3. Гильман А.Л. Расписания в задачах организации периодической обработки инфомации / А.Л. Гильман, Я.Г. Хаит. – Харьков, 1970.

4. Святный В.А. Алгоритм организации цифровых вычислений в цикле реального времени АЦВС // А.Ю. Иванов, В.А. Святный. - Вопросы радиоэлектроники .Сер.ЭВТ. Вып.2,1986г.

5. Иванов Ю. А. «Измерение накладных расходов в операционной системе для построения системы моделирования процессов реального времени», Проблеми моделювання та автоматизації проектування динамічних систем. / Наукові праці Донецького національного технічного університету. Серія "Проблеми моделювання та автоматизації проектування динамічних систем". Випуск 7 (150)- Донецьк: ДонНТУ – 2008, с. 158-176.