Резюме - Динамические КМОП логические схемы широко используются в высокопроизводительных СБИС чипах с целью обеспечения очень высокой помехоустойчивости системы. Однако динамические входы КМОП обладают, по сути, меньшей помехоустойчивостью, чем статические. С увеличением требований к помехоустойчивости из-за стремительного развития технологии масштабирования, допустимый уровень помех динамических схем был в первую очередь увеличен для всех надёжных операций СБИС схем, разработанных используя технологию глубокого субмикронного процесса. В литературе предложено много технологий для увеличения допустимого отклонения шума динамических логических элементов. Обзор и классификация этих технологий впервые представлена в этой статье. Тогда мы представляем новую технологию допустимого уровня шума, используя графическое представление эффекта негативного отрицательного сопротивления. Мы продемонстрировали путём анализа и симуляции, что используя предложенный метод, допустимый уровень шума динамических логических элементов может быть улучшен намного, относительно уровня статических СБИС логических элементов, в то время как преимущества производительности динамических схем всё ещё удерживаются. Результаты симуляции на динамических логических элементах СБИС с большим коэффициентом объединения по входу показывают, что при напряжении 1,6 В входной уровень защиты от шума может быть увеличен до 0,8 В (около 10% задержки затрат) и до 1,0 В (около 20% задержки затрат).

Индексные термины - цифровые интегральные схемы, стиль логики домино, динамические схемы, отрицательное дифференциальное сопротивление, модель допустимого уровня шума.

I. Вступление

Помехи в цифровых интегральных схемах стали одной из главных проблем в разработке очень глубоких субмикронных VLSI чипов. Помехи в цифровых интегральных схемах соответствуют любому событию, происходящему с напряжением в узле и отклоняющему его от номинального значения. Пока эти помехи существовали, они совершали небольшое уменьшение производительности интегральных схем и часто ими пренебрегали. Открытые агрессивные технологии масштабирования постоянно пытаются улучшить производительность схемы и уровень интеграции, из-за которых помехи играют большую роль в сравнении с обычными метриками разработки, такими как область, скорость, потребляемая мощность.

Вместе с технологией масштабирования, агрессивные разработки используют по назначению динамических логических стилей, а также они широко использовались в последние годы для достижения более высокой производительности интегральных схем. Схемы, разработанные с использованием динамических логических стилей, могут быть значительно быстрее и более компактны, чем статические СБИС аналоги. Это особенно важно в случае с большим коэффициентом нагрузки по входу динамической логической схемы, когда один элемент может реализовать логическую функцию, которая в противном случае будет требовать много уровней логических элементов СБИС. Поэтому элементы с большим коэффициентом нагрузки по входу обычно используются в критически производительных блоках высокопроизводительных чипов, таких как микропроцессор, цифровой сигнальный процессор и так далее.

Критичность в динамических схемах часто связана с их относительно слабой помехоустойчивостью. Порог переключения напряжения динамических логических СБИС элементов, определённый как уровень входного напряжения, при котором меняется напряжение на выходе, обычно реализуется с помощью транзистора порогового напряжения Vt. Для сравнения, порог переключения напряжения статического СБИС логического элемента обычно составляет около половины напряжения источника. Поэтому динамические логические элементы, по сути, имеют меньшую помехоустойчивость, чем статические СБИС логические элементы и являются слабой связью в высокопроизводительных VLSI чипах, разработанных с использованием технологии глубокого субмикронного процесса.

Многие технологии производства были разработаны за последние два десятилетия, с целью усилить эту слабую связь. Например, обратные хранители были предложены для предохранения шумового диода от плавания; внутренние шумовые диоды были добавлены для устранения проблемы разделения заряда; небольшая дополнительная p-net-work была сконструирована для улучшения помехоустойчивости до уровня отклонения статических СБИС логических элементов. Однако, существует ремонтная технология улучшения помехоустойчивости динамических схем со значительной стоимостью с точки зрения одной или многих важных метрик разработки, таких как: площадь схемы, скорость и потребляемая мощность. Дело в том, что количество задержек увеличивается стремительно, когда требования к помехоустойчивости увеличиваются наряду с длительным уменьшением масштабирования процесса технологий. Поэтому эффективные помехоустойчивые технологии, которые включают в себя маленький излишек в силиконовой площади, требуют высокой скорости схемы и потребляемой мощности.

В этой статье мы предлагаем метод разработки для увеличения помехоустойчивости динамических схем. Мы покажем, что динамические логические элементы не обязаны иметь меньшую помехоустойчивость, если использованы правильные технологии помехоустойчивости. В самом деле, используя метода, предложенного в этой статье, можно улучшить помехоустойчивость динамических логических схем намного, в сравнении с с уровнем статических СБИС логических элементов, которые всё ещё удерживают преимущество в производительности. Более того, в отличие от многих предыдущих статей, которые описывают только по одной новой схеме в статье, предложенный метод конструирования помехоустойчивости может быть реализован с использованием множества различных схем, и поэтому имеет большее значение.

Остальная часть этой статьи организована следующим образом. Раздел II кратко описывает различные источники шума в динамических логических схемах, разработанных с использованием процесса глубокой субмикронной технологии. Раздел III предоставляет беглый обзор и классификацию существующих технологий увеличения помехоустойчивости. В разделе IV описан предложенный метод увеличения помехоустойчивости. Шумовой порог и задержка динамических схем, использующихся в предложенной технологии, анализируется в разделе V. В разделе VI показаны экспериментальные результаты нагрузочной способности по входу для элементов домино, основанные на симуляции SPICE (Simulation Program with Integrated Circuit Emphasis) – симулятор электронных схем общего назначения с открытым исходным кодом.

II. Помехи в динамических логических схемах.

Для простоты представления, в этой статье наш разговор будет сфокусирован на одном типе динамических схем, известном как логические СБИС схемы домино. Возможно, это наиболее широко используемый динамический логический тип. Однако следует отметить, что помехоустойчивые технологии, рассматриваемые в этой статье, могут также быть применены в других типах динамических схем.

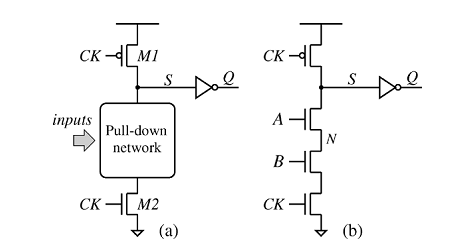

Типичная СБИС логическая домино схема n-типа типу (рис 1.1 (а)), состоит из управляемых сигналом clock транзисторов М1 и М2, выпадающей сети транзисторов n-типа и выходного усилителя мощности. Работа СБИС логической схемы домино может быть разделена на две фазы. В фазе предзарядки, когда сигнал СК имеет низкий уровень, динамический шумовой диод S заряжается до высокого уровня через М1 и выход схемы имеет низкий уровень. Оценочная стадия начинается, когда сигнал СК переходит на высокий уровень. В этой фазе М1 отключен и М2 включен. Динамический шумовой диод S разряжается или остаётся заряженным в зависимости от входов выпадающей сети (рис 2.1 (б)).

Рисунок 2.1 – Типичная СБИС логическая схема домино n-типа

Источники шума в динамических логических схемах могут быть широко классифицированы в двух основных типах:

- Шум разделения заряда вызывается перераспределением заряда между динамическим шумовым диодом и внутренними диодами выпадающей сети. Разделение заряда ослабляет уровень напряжения на динамическом шумовом диоде, что потенциально может привести к ложному переключению динамической логической схемы.

- Шум утечки возникает из-за возможной потери заряда в оценочной фазе из-за подпорогового тока утечки. Ток утечки возрастает экспоненциально по отношению к пороговому напряжению транзистора, который постоянно является масштабируемым как ослабитель источника напряжения. Поэтому утечка в транзисторах может быть значительным источником шума в широких логических схемах, разработанных с использованием процесса очень глубоких субмикронных технологий.

- Входной шум возникает из-за шума, имеющегося на входах логической схемы. Он первоначально обусловлен эффектом связи, известном как перекрёстная помеха, между расположенными рядом одиночными проводами. Этот тип шума стал выступающим источником неудач для глубоких субмикронных VLSI схем из-за агрессивных связей масштабирования в боковых размерах с относительно неизменными вертикальными размерами.

- Шум мощности и земли в основном объясняется паразитическим сопротивлением и индуктивностью на сетях мощности и земли и в корпусе микросхемы. Сети мощности и земли также могут быть загрязнены внешними шумами с контактов микросхемы. Кроме того, явное уменьшение шумового порога схемы, возможно, из-за сниженного напряжения источника, плохое сочетание мощности и напряжения земли, может перевести в постоянный ток шум на входе приёмника.

- Шум подложки может оказывать влияние на чистоту сигнала логической схемы через соединение подложки. Более того, так как пороговое напряжение транзистора является функцией от напряжения подложки, шум в подложке может моментально понизить пороговое напряжение транзисторов в выпадающей сети, делая их более восприимчивыми для других помех.

В общем, те помехи, вместе с другими источниками помех, как процесс вариации, альфа частицы излучения, и так далее, могут подвергать опасности правильное функционирование динамических логических схем, разработанных с использованием процесса очень глубокой субмикронной технологии. И желанные технологии помехоустойчивости должны иметь возможность улучшения защищённости от шума динамических логических схем вопреки всем упомянутым помехам.

III. Обзор предыдущих работ.

За прошедшие два десятилетия, были разработаны многие технологии микросхем с целью улучшить защищённость от шума динамических СБИС логических схем. Поскольку невозможно объединить все технологии в литературе, в этом разделе мы представляем обзор нескольких важных техник. И мы классифицировали те технологии в четыре основных категории, основываясь на принципе их работы:

- Использующие защёлку;

- Предзаряжающие внутренние шумовые диоды;

- Подымающие напряжения источника;

- Образующие дополнительную р-сеть.

А. Имеющие защёлку.

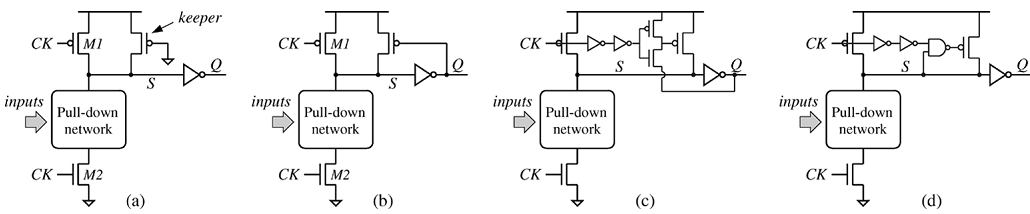

Возможно, простейший способ увеличить помехоустойчивость динамической СБИС логической схемы – это использование слабого транзистора, известного как защёлка, в динамическом узле (рис 3.1). Транзистор-защёлка выделяет маленький ток в энергоснабжение сети динамического шумового диода схемы так, что заряд, сохранённый на динамическом шумовом диоде, сохраняется. В исходной динамической логической работе домино схема защёлки р-МОП связана с землёй (рис 3.1 (а)). Поэтому защёлка всегда включена. Позже, обратные защёлки стали использоваться более широко (рис 3.1(b)), так как они исключают возможность возникновения проблемы потребления мощности непосредственной связью, благодаря использованию всегда открытой защёлки в оценочной фазе схем домино.

Рисунок 3.1 – Типичная СБИС логическая схема домино n-типа

Использование защёлок становится причиной конфликта, когда выпадающая сеть включена во время оценочной фазы, и в результате понижается общая производительность схемы. В схемах с большим коэффициентом объединения по входу, использующих процесс очень глубокой субмикронной технологии, большая утечка тока через n-сеть делает необходимым использования очень сильной защёлки для удержания напряжения на динамическом шумовом диоде. Для ослабления серьёзных проблем конфликта, связанных с сильной защёлкой, новые технологии защёлки были предложены Анисом (рис 3.1(с)) и Анвандпором (рис 3.1(d)). Обе технологии разделяют одинаковый основной принцип, то есть временное отключение защёлки в течение короткого промежутка времени, когда переключаются динамические элементы. Эти две технологии выглядели очень эффективными в увеличении помехоустойчивости динамических элементов от внутренних шумов схемы, таких как шум утечки. Однако, динамические схемы с теми защёлками всё ещё восприимчивы ко внешним шумам и создают аппаратные ошибки, так как динамический диод недостаточно защищён в течение промежутка времени переключения схемы. Мы объясним это детально в разделе IV и покажем новый класс защёлок, созданных по технологиям, увеличивающим защищённость схемы от шума как внутреннего, так и внешнего, с минимальными конфликтами.

Б. Предзаряженные внутренние шумовые диоды.

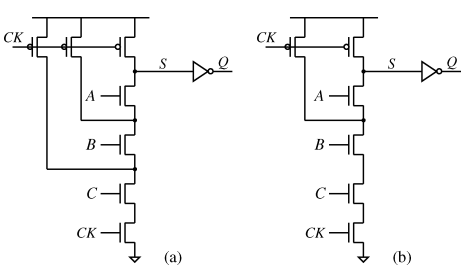

В сложных динамических логических схемах с большой выпадающей сетью, разделение заряда между динамическим шумовым диодом и внутренними диодами в выпадающей сети часто приводит к ложному переключению схемы. Простой эффективный способ предотвратить проблему разделения заряда – предзарядить внутренние диоды выпадающей сети вместе с предзарядкой динамического шумового диода. Пример динамического элемента 3-И, использующего эту технологию, показан на рисунке 3.2(а).

Когда все внутренние диоды предзаряжены, технология способна устранять проблему разделения заряда путём использования большого количества предзаряженных транзисторов и повышенной ёмкости загрузки на clock-сети. Частичная предзарядка, как показано на рисунке 3.2(b), также использовалась на практике как компромисс между защитой от шума и избытками площади микросхемы и clock-нагрузки. N-МОП транзисторы также могут быть использованы для предзарядки внутренних диодов, если стоимость инверторов, необходимых для генерации дополнительного clock-сигнала, будет оправдана. Так как внутренние диоды только предзаряжаются до напряжения Vdd – Vt, динамические логические элементы, использующие n-МОП предзарядку транзисторов, имеют сниженное время разрядки и уменьшенную динамическую потребляемую мощность. В конечном счёте, это означает, что технологии, основанные на предзарядке внутренних диодов, не очень эффективные в борьбе с внешними шумами.

Рисунок 3.2 – Предзарядка внуттенних диодов

В. Поднятие напряжения источника.

Эффективный способ улучшения помехоустойчивости от внутренних и внешних помех – увеличение напряжения источника для транзисторов в выпадающей сети. Так как напряжение элемента становится больше, сумма напряжения источника и порогового напряжения транзистора, когда он включен, стремится увеличить напряжение включения элемента. Более того, из-за основного эффекта пороговое напряжение транзистора увеличивается, когда растёт напряжение источника. Это тоже является жертвой для улучшения напряжения включения элемента.

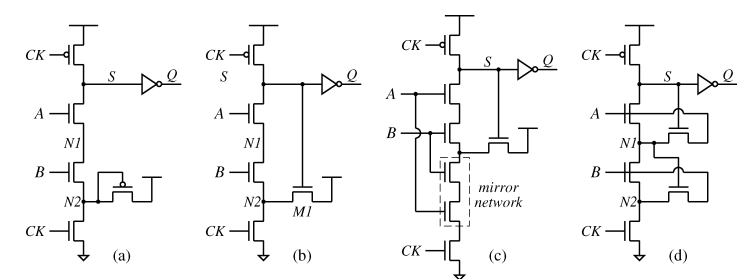

Технология р-МОП натяжения, показанная на рисунке 3.3(а), имеет р-МОП транзистор в узле N2, формирующий резистивный делитель напряжения управляемый нижним уровнем сигнала clock. Напряжение в узле N2, которое устанавливает переключение порогового напряжения динамического логического элемента, может быть установлено изменением относительного размера натяжения р-МОП транзистора. Большим недостатком этой технологии является непосредственная связь с потреблением мощности в резистивном напряжении. Более того, так как уровень напряжения на динамическом диоде S не может стать ниже напряжения в узле N2, колебание напряжения на диоде S невысокое. Когда размер натяжения р-МОП транзистора становится большим для повышения помехоустойчивости элемента, выход элемента может также не иметь размаха колебания.

Рисунок 3.3 – Поднятие напряжения источника

Улучшенный метод, показанный на рисунке 3.3(b), имеет растяжение транзистора с обратным управлением. Здесь n-МОП транзистор М1 используется для растяжения напряжения внутреннего диода. Выход транзистора растяжения подключен к динамическому шумовому диоду элемента домино. Такой дизайн позволяет транзистору растяжения быть в отсечке, когда напряжения шумового диода становится низким, поэтому, динамический шумовой диод S испытывает размах колебания напряжения. Также, непосредственная связь с проблемой потребляемой мощности частично решена. Это происходит только под управлением определённых входных комбинаций, которые не включают выпадающую сеть. Отметьте, что р-МОП транзистор может быть использован похожим образом в этой технологии, при условии, что выход р-МОП транзистора подсоединён к выходу динамического логического элемента.

Зеркальная технология имеет n-МОП транзистор с обратным контролем, похожий на технологию натяжения n-МОП. В дополнение, она дублирует выпадающую сеть с целью дальнейшего уменьшения непосредственной связи с потребляемой мощностью и дальнейшего улучшения помехоустойчивости элемента. Динамический элемент 2-И, созданный с использованием зеркальной технологии, показан на рисунке 3.3(c). Когда выпадающая сеть отключена, зеркальная сеть также отключена, следовательно, отключен потенциал, связывающий проводящий путь из n-МОП транзистора растяжения с транзистором, управляемым низким уровнем сигнала clock. Поэтому, проблема непосредственной связи с потреблением мощности полностью решена. Однако эта технология значительно удлиняет время разрядки выпадающей сети, которая потенциально может замедлить схему или значительно увеличить активную площадь схемы, когда транзисторы значительно увеличены.

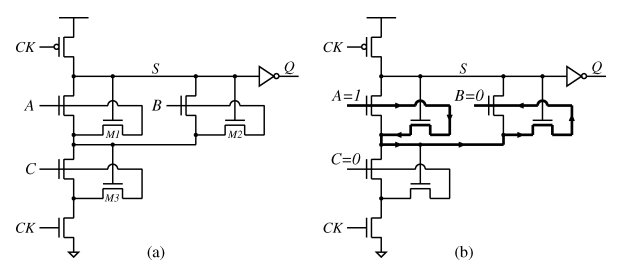

Технология транзисторов-близнецов принимает n-МОП транзисторы натяжения на всех внутренних узлах для дальнейшего улучшения помехоустойчивости динамического элемента. В дополнение, узлы утечки n-МОП транзисторов растяжения подключены ко входам вместо сети источника, как показано на рисунке 3.3(d). Таким образом, избегается ненужное добавление тока транзисторов растяжения, и в результате снижается потребляемая мощность элемента. Однако эта технология стремится увеличить входную ёмкость элемента, что может замедлить переключение элемента с предыдущего состояния. Далее, эта технология является неподходящей для определённых логических функций, потому что они могут закоротить входные диоды. Например, на рисунке 3.4(a), мы видим элемент 3-ИЛИ-И, выполняющий логическую функцию (А+В)*С. Вход А имеет высокий уровень, когда входы В и С имеют низкий. Динамический узел S имеет высокий уровень, потому что С имеет низкий уровень и нет разрядки через землю. По такому сценарию, есть непосредственная связь между входами А и В, показанная на рисунке 3.4(b). Поэтому логические состояния на входах А или В непонятны. Отметьте, что общее повреждение может выйти далеко за пределы одного рассматриваемого динамического элемента, если эти двусмысленные входы подключены к большому количеству других элементов.

Рисунок 3.4 - Возможные проблемы при использовании технологии поднятия напряжения