SimpleScalar: Инфраструктура для моделирования компьютерных систем

Авторы: Todd Austin, Eric Larson, Dan Ernst

Перевод с англ.: И.А. Антипенко, перевод 1, 2, 3 разделов статьи

Описание: В статье описаны особенности SimpleScalar. Виды моделирования, модели моделирования.

Источник (англ.): Todd Austin, Eric Larson, Dan Ernst SimpleScalar: An Infrastructure for Computer System Modeling // February 2002 https://web.eecs.umich.edu/~taustin/papers/IEEEcomp-simplescalar.pdf

Введение

Для ускорения разработки аппаратного обеспечения, инженеры часто используют программные модели аппаратного обеспечения, которое они производят. Разрабатываются модели с помощью традиционного программирования или языков описания аппаратного обеспечения. На этих моделях можно выполнять программы для проверки производительности и правильности проектирования.

Программисты могут использовать программные модели для разработки и тестирования программного обеспечения еще до того, как аппаратные средства будут доступны. Хотя программные модели работают медленнее, чем их аппаратные аналоги, они позволяют быстро построить и проверить модель без необходимости создания реального оборудования. Такой механизм обеспечивает быструю разработку качественного оборудования.

Развитие программных моделей аппаратного обеспечения движут три основных принципа: производительность, гибкость, детализация. Производительность определяет нагрузку, под которой может работать модель, используя доступные для симуляции машинные ресурсы. Гибкость определяет, насколько хорошо спроектирована модель для дальнейшей модификации. Детализация определяется уровнем абстракции, используемым для реализации компонентов модели. Высокодетализированная модель с большей точностью с эмулирует все аспекты машинных операций.

На практике оптимизировать эти три характеристики не представляется возможным. Поэтому в большинстве программных моделей оптимизированы только одна или две из них. Это объясняет наличие множества симуляторов на сегодняшний день.

Симуляторы SimpleScalar воспроизводят операции компьютерных устройств исполнением всех программных инструкций с использованием интерпретатора. Этот набор инструментов поддерживает популярные наборы команд, включая Alpha, Power PC, x86 и ARM.

Основы моделирования

Типичный подход к моделированию компьютерных систем использует модель простого приближения с хорошей производительностью моделирования и модульной структурой кода. Такой тип симуляторов подходит для исследований, потому что простая модель фокусируется на основных компонентах конструкции, не затрагивая подробно детали, которые могут отрицательно повлиять на производительность и гибкость модели.

С другой стороны, промышленность требует детализированные модели для минимизации конструкционных рисков. Детальное моделирование дает уверенность в том, что оборудование не будет содержать неисправные компоненты и узкие места.

Имитационное моделирование - это метод исследования, при котором изучаемая система заменяется моделью, с достаточной точностью описывающей реальную систему, с которой проводятся эксперименты с целью получения информации об этой системе.

Существующие имитационные модели позволяют детально рассмотреть все особенности работы исследуемого процессора и могут использоваться для анализа работы любых приложений и любых входных потоков. Недостатком имитационных моделей является сложность их разработки и узкая специализация. Обычно подобные модели разрабатываются только для одной или нескольких схожих структур, и их модернизация для поддержки других устройств оказывается чрезмерно трудоемкой. В силу этих причин, имитационные модели, в отличие от аналитических, сложно использовать для анализа большого числа структур. Но они позволяют более детально рассмотреть работу всех компонентов процессора, менее требовательны к форме описания входного потока данных и выполняемых приложений.

Моделирование с simplescalar

SimpleScalar был написан в 1992 году в рамках проекта Multisсalar в Университете штата Висконсин. В 1995 году набор инструментов был выпущен в качестве открытого исходного дистрибутива в свободном доступе для академических некоммерческих пользователей.

SimpleScalar обеспечивает инфраструктуру для компьютерной системы моделирования, что упрощает реализацию аппаратных моделей. В процессе моделирования измеряются динамические характеристики аппаратной модели и производительности программного обеспечения, работающего на ней.

SimpleScalar содержит несколько моделей, подходящих для различных общих задач архитектурного анализа. В таблице 1.1 приведен список симуляторов, которые включены в SimpleScalar, от sim-safe - минимального инструмента, который эмулирует только набор инструкций, до sim-outorder - детализированной микроархитектурной модели с динамическим планированием и многоуровневой системой памяти.

Все симуляторы SimpleScalar имеют сравнительно небольшой объем кода, так как используют компоненты инфраструктуры SimpleScalar, которые обеспечивают широкий выбор процедур для реализации множества общих задач моделирования. Такие задачи включают в себя моделирование набора команд, эмулирование ввода/вывода, управление дискретными событиями и моделирование общих микроархитектурных компонент, таких как модуль предсказания переходов, очереди инструкций и кэш. В общем, чем более детализированной становится модель, тем большим становится размер кода и тем медленнее она выполняется за счет возросшей сложности обработки каждой эмулируемой инструкции.

| Симулятор | Описание | Строк кода | Скорость симуляции |

|---|---|---|---|

| sim-safe | Простой функциональный симулятор | 320 | 6 MIPS |

| sim-fast | Функциональный симулятор, с оптимизированной скоростью | 780 | 7 MIPS |

| sim-profile | Динамический программный анализатор | 1300 | 4 MIPS |

| sim-bpred | Симулятор предсказания переходов | 1200 | 5 MIPS |

| sim-cache | Симулятор многоуровневой кеш-памяти | 1400 | 4 MIPS |

| sim-buzz | Генератор и тестер случайных инструкций | 2300 | 2 MIPS |

| sim-outorder | Симулятор детализированной микроархитектурной модели с динамическим планированием и многоуровневой системой памяти | 3900 | 0.3 MIPS |

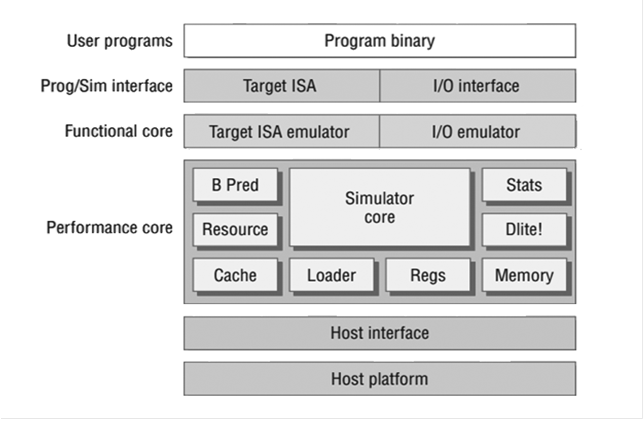

На рисунке 2 представлена программная архитектура SimpleScalar. Приложение запускается на модели используя технологию, называемую execution-driven simulation

, которая требует включения эмулятора набора команд и модуль эмуляции ввода/вывода. Эмулятор набора команд интерпретирует каждую инструкцию, направляя действия модели аппаратного обеспечения через callback-интерфейсы, предоставляемые интерпретатором.

Рисунок 2 – Архитектура симулятора SimpleScalar

SimpleScalar содержит интерпретаторы инструкций для набора команд ARM, x86, PPC и Alpha. Интерпретаторы написаны на языке, который обеспечивает комплексный механизм для описания того, как команды изменяют содержание регистров и состояние памяти. Препроцессор использует эти машинные определения чтобы синтезировать интерпретаторы, анализаторы зависимостей и генераторы микрокода, которые необходимы для модели SimpleScalar. С небольшим количеством дополнительных надстроек модели могут поддерживать определенное множество наборов команд.

Модуль эмуляции ввода/вывода обеспечивает имитацию программ, имеющих доступ к устройствам ввода/вывода. SimpleScalar поддерживает несколько модулей эмуляции ввода/вывода, от эмуляции системных вызовов до моделирования системы в целом. Система эмулирует вызов путем перевода его в эквивалентный вызов операционной системы и направляя симулятору на обработку вызов от имени эмулируемой программы. Например, если моделируемая программа пытается открыть файл, модуль эмуляции ввода/ вывода транслирует запрос на вызов open() и возвращает полученный дескриптор файла или код ошибки в регистр моделируемой программы.

Другие модули симуляции обеспечивают более детальное моделирование актуальных аппаратных устройств. Например, SimpleScalar/ARM версия включает эмулятор ввода/вывода для устройств Compaq IPaq. Этот эмулятор настолько детализирован, что позволяет загружать операционную систему ARM Linux. Эмуляция ввода/вывода на уровне устройств имеет преимущество для анализа роли операционной системы при выполнении приложения. Это показало себя эффективным в серверных приложениях, где сервисы работы с сетью и файловой системой зависят прежде всего от нагрузки во время выполнения.

В каждой модели код ядра симулятора определяет аппаратную организацию модели. Код симулятора определяет главный цикл, который выполняет одну итерацию для каждой инструкции в программе до окончания выполнения программы. Для синхронной модели главный цикл должен учитывать ход времени исполнения, измеренный в тактах для этой модели. Переменная cycle хранит время выполнения, записанное в количестве тактов, которое потребовалось для выполнения программы до текущей команды.

Модуль cache.c, поставляемый с дистрибутивом SimpleScalar, реализует кэш данных. Модуль кэширования использует хеш-таблицу для записи блоков кэша. Если адрес запроса соответствует записи в хеш-таблице, то такой запрос возвращает попадание в кэш. Если же адрес запроса не содержит записи в хеш-таблице, то запрос возвращает кэш-промах. При этом делается системный вызов обработчика кэш-промаха, который возвращает количество тактов, необходимое для обслуживания кэш-промаха. В модели определяется обработчик промаха, который может быть другим кэш-модулем или моделью DRAM-памяти. Кэш-модуль не возвращает значение, полученное по запросу в кэш, потому что это значение не влияет на латентность доступа кэша. Для конструкций, в которых значение кэша может повлиять на латентность, система может сконфигурировать кэш-модуль таким образом, что он будет возвращать значение по запросу.

В дополнение к стандартным компонентам, SimpleScalar предоставляет разнообразные вспомогательные модули, которые реализуют полезные функции, требуемые во многих моделях. Такие модели включают отладчик, загрузчик программ, процессор командной строки, пакет статистики.

Список использованной литературы

- R.M. Bentley, “Validating the Pentium 4 Microprocessor,” Proc. Int’l Conf. Dependable Systems and Networks (DSN-2001), IEEE CS Press, Los Alamitos, Calif., 2001, pp. 193-198.

- E. Schnarr and J. Larus, “Fast Out-of-Order Processor Simulation Using Memoization,” Proc. 8th Int’l Conf. Architectural Support for Programming Languages and Operating Systems (ASPLOS-VIII), ACM Press, New York, 1998, pp. 283-294.

- C. Weaver et al., “Performance Analysis Using Pipeline Visualization,” Proc. IEEE Int’l Symp. Performance Analysis of Systems and Software (ISPASS-2001), IEEE CS Press, Los Alamitos, Calif., 2001, pp. 18-21.

- R. Desikan, D. Burger, and S.W. Keckler, “Measuring Experimental Error in Microprocessor Simulation,” Proc. 28th Ann. Int’l Symp. Computer Architecture (ISCA-28), ACM Press, New York, 2001, pp. 266-277.

- E. Larson, S. Chatterjee, and T. Austin, “MASE: A Novel Infrastructure for Detailed Microarchitectural Modeling,” Proc. IEEE Int’l Symp. Performance Analysis of Systems and Software (ISPASS-2001), IEEE CS Press, Los Alamitos, Calif., 2001, pp. 1-9.