Введение

Для реализации системы реального времени может быть использовано два следующих подхода: программная реализация требуемых алгоритмов на базе микропроцессора и программноаппаратная реализация на базе программируемых логических интегральных схем (сюда же отнесём реализацию систем на кристалле). В данной работе внимание уделяется построению СРВ на базе ПЛИС. Преимуществом данного подхода, прежде всего, является возможность аппаратной реализации на одной микросхеме специализированных компонентов СРВ для взаимодействия с внешними компонентами или периферийными устройствами, например реализация VGA-адаптера интерфейса пользователя. Разработка устройств на базе ПЛИС достаточно проста. Серийно выпускаются отладочные платы, которые содержат микросхему ПЛИС, дополнительные микросхемы для организации её работы и реализации определённого количества внешних интерфейсов. Кроме того такие платы обычно оборудованы значительным количеством разъёмов, которые могут быть использованы для подключения периферийных устройств. В дальнейшем будет рассматриваться система на базе комплекса Xilinx Spartan-3E Starter Kit Board.

1 Разработка структуры аппаратных средств

Рассмотрим основные особенности устройства и программирования микросхем FPGA. Данные ПЛИС содержат большое число логических ячеек (десятки и сотни тысяч), которые реализуют сложные функции (например, функциональный генератор на 4, 5 или 6 входов + однобитный регистр). Кроме того, в состав FPGA входят аппаратные модули для реализации специальных функций (память, умножитель, сдвиговый регистр). Данный тип ПЛИС редко содержит встроенную энергонезависимую память, поэтому должен конфигурироваться при каждом включении питания [1].

В состав данной отладочной платы входят следующие основные компоненты: Xilinx XC3S500E Spartan-3E FPGA (232 доступных программисту внешних выводов и около 10000 LUT-ячеек), Xilinx XC2C64A CoolRunner CPLD (64 макроячейки), Xilinx XCF04S (512 килобайт Platform Flash), ST Micro 25P16V6G (2 мегабайта последовательной Flash-памяти, может быть использована для хранения кода для встраиваемого микропроцессора MicroBlaze), Intel TE28F128 (16 мегабайт параллельной Flashпамяти). В рассматриваемой отладочной плате реализовано два способа программирования ПЛИС. Возможна загрузка прошивки в микросхему FPGA непосредственно с персонального компьютера через встроенный интерфейс JTAG и из одной из трёх встроенных микросхем Flash-памяти. Прошивка для кристалла FPGA занимает 283 килобайта [2].

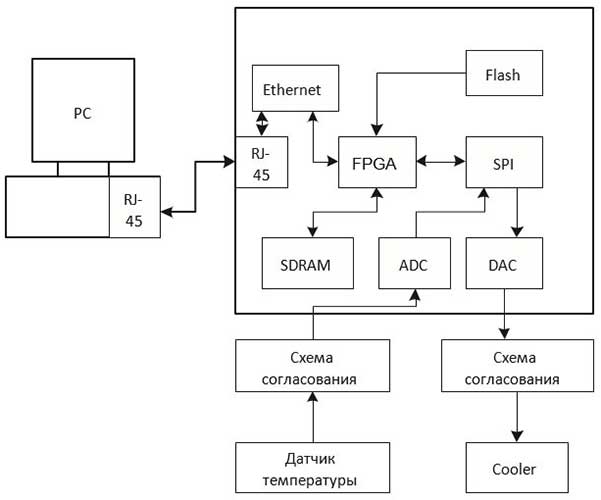

Рассмотрим пример реализации системы реального времени на данной отладочной плате. СРВ реализует удалённый контроль температуры и управление системой охлаждения объекта. Структурная схема системы приведена на рисунке 1.

Помимо рассмотренных выше компонентов, в состав отладочной платы входят также:

Рисунок 1. Структурная схема системы реального времени

аналого-цифровой преобразователь на два входа и цифро-аналоговый преобразователь на четыре входа, взаимодействующие с FPGA через SPI интерфейс, микросхема DDR SDRAM объёмом 64 мегабайта является оперативной памятью СРВ, встроенный контроллер Ethernet 10/100 обеспечивает физический уровень интерфейса для удалённого взаимодействия с пользователем (MAC-уровень реализуется в FPGA) [2].

В состав СРВ входят внешние компоненты: датчик температуры и исполнительный механизм (вентилятор), интерфейс пользователя и вычислитель (встраиваемый процессор). Ядром системы является вычислитель - встраиваемым процессор MicroBlaze. Конфигурирование FPGA чипа происходит из энергонезависимой Flash памяти, и в ней же храниться всё программное обеспечение для СРВ. Удалённое взаимодействие с пользователем реализовано по протоколу Ethernet. Для этого используется контроллер, расположенный на плате. Для реализации MAC-уровня используется соответствующее IP-ядро (XPS Ethernet MAC Lite) [4]. Для преобразования типов сигналов (дискретный в аналоговый или наоборот) используются ADC и DAC, которые также имеются на плате. Взаимодействие между ними и FPGA чипом осуществляется через интерфейс SPI.

Управление исполнительным механизмом осуществляется через 12-разрядный 4-канальный цифро-аналоговый преобразователь, напряжение, на выходе которого определяется по следующим формулам: для каналов A,B:

Vout = (D[11:0] / 4096) × (3.3V ±5%),

а для каналов C,D:

Vout = (D[11:0] / 4096) × (2.5V ±5%).

Ввод аналоговых значений от датчика температуры выполняется с помощью 2-канального 14разрядного аналого-цифрового преобразователя с программируемым предварительным усилителем сигнала. Код на выходе ADC определяется по формуле:

D[13:0] = GAIN × (Vin −1.65V) / 1.25V) × 8192,

где GAIN – код в регистре программируемого усилителя [2]. Как видно из формул, уровни сигналов для DAC и ADC имеют вполне определённые значения. Кроме того, нагрузочная способность цифро-аналогового преобразователя недостаточна для питания вентилятора. Поэтому, между терминальными элементами и преобразователями типов сигналов включены согласующие схемы. Схема для датчика температуры обеспечивает приведение верхнего и нижнего предела напряжения к одному из рабочих значений для ADC. Схема для вентилятора, помимо этого, также обеспечивает усиление по мощности для обеспечения требуемого тока потребления двигателя вентилятора.

46 «Информатика и компьютерные технологии-2011»

2 определение конфигурации вычислителя

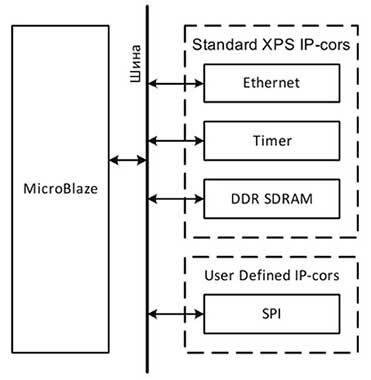

Система реального времени выдвигает особые требования к структуре вычислителя, поэтому процессор для СРВ должен содержать дополнительные компоненты, что показано на рисунке 2.

Итак, помимо стандартных компонентов MicroBlaze, в состав вычислителя также входит набор IP-ядер, которые подключаются на шину PLB (Processor Local Bus). При этом для устройства выделяется диапазон адресов в едином адресном пространстве, обмен данными с устройством организуется по этим адресам как через порты ввода/вывода. В системе используются преимущественно стандартные IP-ядра, исключение составляет специализированное устройство обмена данными по SPI (DAC, ADC, Flash-memory на данной отладочной плате осуществляет обмен данными с FPGA через последовательный интерфейс). Контроль температуры в режиме реального времени, функция обработки запускается через определённые интервалы времени, отмеряемые счётчиком-таймером. Поскольку на кристалле недостаточно встроенной памяти, в качестве оперативной будет использована внешняя DDR SDRAM (64 мегабайта) [3].

Рисунок 2. Структурные особенности процессора для СРВ

3 Разработка структуры программных средств

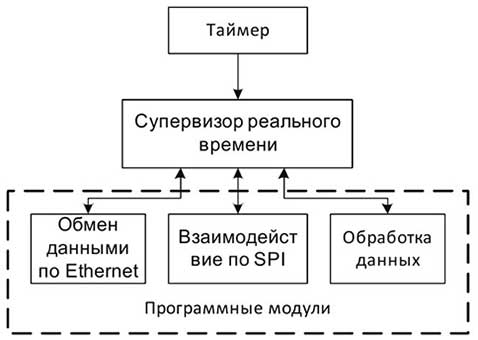

Помимо аппаратных особенностей, система реального времени имеет также специфическое программного обеспечения. Структура ПО изображена на рисунке 3.

Рисунок 3. Структура программного обеспечения СРВ

Разработка ПО полномасштабной системы реального времени целесообразна на базе встраиваемой операционной системы (подобной Linux) [5]. В данном случае возможно реализовать ПО без использования ОС. Так как в рассматриваемой системе отсутствуют задачи по проблемным прерываниям от внешних компонент, то, главный модуль нашего программного обеспечения (супервизор реального времени) вызывается только периодически по таймеру. Супервизор управляет вызовом подпрограмм и следит за процессом их выполнения. Рассмотрим один цикл работы ПО. После срабатывания таймера вызывается супервизор, который, прежде всего, запускает модуль обмена по SPI для считывания показаний датчика температуры, далее вызывается модуль обработки данных, который анализирует эти показания и вычисляет управляющее воздействие, затем опять вызывается модуль обмена по SPI для сообщения этого воздействия управляющему механизму (вентилятору), затем вызывается модуль обмена с удалённым пользователем, которому сообщается текущая информация о состоянии объекта.

Выводы

Рассмотрим основные преимущества реализации систем реального времени на FPGA по сравнению традиционной реализацией на микроконтроллерах:

1. Возможность значительного повышения быстродействия за счёт аппаратной реализации или распараллеливания ресурсоёмких операций.

2. Возможность оптимизации быстродействия и затрат оборудования за счёт тонкого конфигурирования встраиваемого процессора специально для решаемой задачи.

3. Возможность подключения большого числа нестандартных периферийных устройств (в рассматриваемой системе ПЛИС имеет более 230 доступных программисту выводов).

4. Возможность реализации на том же кристалле дополнительных быстродействующих устройств, работающих на тактовой частоте, значительно превышающей тактовую частоту встраиваемого процессора.

Реализация СРВ на базе FPGA имеет и некоторые недостатки, а именно:

1. С позиции времени выхода на рынок, сложность совместного программно-аппаратного проектирования, отладки и тестирования ПЛИС.

2. Отсутствие в FPGA встроенной Flash-памяти в отличие от микроконтроллеров.

Литература

[1] ПЛИС. Материал из Википедии – свободной энциклопедии. Электронный ресурс. Режим доступа: http://ru.wikipedia.org/wiki/ПЛИС

[2] Spartan-3E Starter Kit Board User Guide. UG230 (v1.0) March 9, 2006

[3] Xilinx Spartan-3E FPGA Family: Complete Data Sheet. DS312 May 19, 2006

[4] EDK Concepts, Tools and Techniques. UG683 September 21, 2010

[5] Using EDK to Run Xilkernel on a MicroBlaze Processor. UG758 August 11, 2010