Реферат за темою випускної роботи

Зміст

- Вступ

- 1. Актуальність теми

- 2. Постбінарне уявлення даних

- 3. Апарата модель

- 4. Очікувані результати

- Висновки

- Список літератури

Вступ

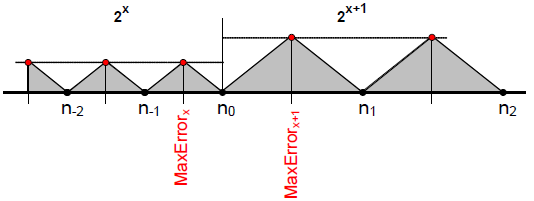

Сьогодні апаратна складова сучасних комп'ютерів оперує різноманітними операціями над числами, які можуть бути представлені в двох форматах – в цілому або у форматі з плаваючою комою. Виникнення і накопичення похибки обчислень при виконанні арифметичних операцій з плаваючою комою є невід'ємною частиною сучасного комп'ютинга, так як числа у форматі IEEE754 представляють кінцеву множину, на яку відображається нескінченна множина дійсних чисел і крок чисел дорівнює величині найменшого розряду: h = 2Em-off. Таким чином графік помилки уявлення і виглядає як показано на рисунку 1. Тому актуальним і затребуваним є вирішення проблеми точності та достовірності комп'ютерних обчислень шляхом мінімізації похибок, їх обліку та контролю при роботі з числами у форматі з плаваючою комою.

Рисунок 1 – Графік помилки подання

В роботі [1, с. 196-210] розглянуті проблеми комп'ютерних обчислень, що викликані використанням стандарту IEEE 754, а також наведено класифікацію помилок з прикладами отримання несподіваних

результатів. Аналіз матеріалу показав, що до формату числа з плаваючою комою неможливо точно привести дійсне число на увазі того, що формат містить безліч кінцевих значень (точок розрядної сітки) якими неможливо уявити нескінченну безліч дійсних чисел. Цей фактор є основним і найважливішим недоліком стандартного плаваючого формату, що підтверджується і досліджується в цілому сегменті наукових публікацій, наприклад в [2; 3].

Серед інших рішень даної проблеми можна виділити можливість переходу від числа точки на числовій осі

до числа інтервального, що підтверджується розвитком інтервального аналізу [4] та розповсюдженням інтервальних підходів при вирішенні широкого кола завдань [5]. Інтервальний підхід дозволяє враховувати помилки обчислень, а також вирішує проблему комп'ютерного подання й обробки ірраціональних (в тому числі і трансцендентних) чисел. У дослідженнях [6; 7] виділений недолік переходу до машинних інтервалів, оскільки при занесенні значень меж інтервального числа в пам'ять ЕОМ виникає необхідність знову використовувати речові формати чисел, які є стандартними форматами чисел з плаваючою комою одинарної або подвійної точності. Також до недоліків можна віднести можливе розростання інтервалу.

У циклі наукових робіт, найбільш значущими з яких є монографії [1] і [7], пропонується рішення поставленої проблеми. Авторами розроблені постбінарние уявлення та обробка числових даних, постбінарное округлення, а також запропоновані відповідні формати чисел.

Тому метою даної роботи є проведення аналізу можливостей постбінарного представлення чисел. Виявлення та аналіз доцільності застосування постбінарних чисел в інтервального арифметики. У рамках позначеного аналізу необхідно запропонувати конфігурацію арифметико–логічного пристрою (АЛП) як основної частини спеціалізованого математичного співпроцесора [8].

1. Актуальність теми

Сьогодні, для представлення числової інформації з плаваючою комою використовують стандарт IEEE 754. Даний стандарт використовується як в апаратних, так і в програмних реалізаціях арифметичних дій. Перший стандарт був прийнятий в 1985 році, останній же варіант прийнятий в 2008 році. У редакції стандарту від 2008 року збережені всі бінарні формати з початкового стандарту і додані ще три базових стандарту (один бінарний і два десяткових).

Робота з числами з плаваючою комою стандарту IEEE 754 є відображенням теоретичної математики на множині дійсних чисел. Тому здається логічним називати числа, представлені в стандарті IEEE 754, але цей термін не відображає дійсні властивості стандарту IEEE 754.

Стандарт чисел IEEE 754 визначає представлення чисел у вигляді ступеня і мантиси. Стандартне подання має мантису і ступінь, що вказує двійковий показник ступеня вкрай лівого розряду мантиси. При цьому стандарт встановлює формати представлення по довжинах, представлені в таблиці 1.

Таблиця 1 – Формати по довжинах

| Name | Common name | BaseDigit | E min | E max | E max | Emax Dec |

|---|---|---|---|---|---|---|

| binary 16 | Half precision | 2 | -14 | +15 | 3.31 | 4.51 |

| binary 32 | Single precision | 2 | -126 | +127 | 7.22 | 38.23 |

| binary 64 | Double precision | 2 | -1022 | +1023 | 15.95 | 307.95 |

| binary 128 | Quadruple precision | 2 | -16382 | +16383 | 34.02 | 4931.77 |

| decimal 32 | 10 | -95 | +96 | 7 | 96 | |

| decimal 64 | 10 | -383 | +384 | 16 | 384 | |

| decimal 128 | 10 | -6143 | +6144 | 34 | 6144 |

Перше, що виділяється в цій таблиці – довжини мантис. Десятки точних знаків після коми є зайвими. У наші дні метрологія може виміряти час і швидкість світла поки лише з десятизначної точністю. У техніці ж використовуються числа, як правило, не перевищують п'яти знаків після коми.Тому більшість мантисс чисел стандарту IEEE754, особливо в форматах подвійний і розширеної точності, фактично безглузда і являє собою так званий інформаційний шум. Можна зробити висновок, що сучасний комп'ютинг, заснований на стандарті чисел з плаваючою комою IEEE754 є просто обробкою шумів. І як наслідок вихідні дані цього компьютинга не є достовірними і зашумленими. Виділення змістовної частини з цих шумів чисел з плаваючою комою здійснюється людиною (наприклад, програмістом при плануванні виводу результатів) по інтуїції, а не на основі твердих математичних правил і алгоритмів.

Таким чином, математична модель з плаваючими числами може бути адекватною і працездатною лише в разі забезпечення контролю похибок обчислень.

Для реалізації такого контролю можливе використання постбінарного подання чисел, а також використання інтервального математики. Цінність інтервальних обчислень полягає в отриманні найбільш достовірних рішень вихідних завдань, враховуючи можливі зміни вихідних і результуючих значень, пов'язані з неточністю арифметики з плаваючою комою. Але слід зауважити, що для складних обчислень результати можуть виявитися незадовільними, перш за все через занадто великої довжини одержуваних інтервалів.

Одне з можливих рішень цієї проблеми лежить у переході до постбінарних обчислень. При цьому з'являється можливість максимально використовувати той науково–технічний заділ, який накопичено в рамках інтервальних обчислень, але при цьому усунути або мінімізувати деякі проблеми інтервального аналізу, пов'язані, наприклад, з протиріччям між точністю представлення самих кордонів інтервальних значень і фактичної неточністю тих даних, які вони представляють.

2. Постбінарне уявлення даних

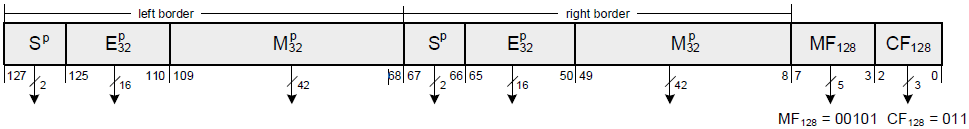

У цьому випадку доцільно використовувати постбінарні інтервальні формати одинарної (pbinary128/32ip) і подвійний (pbinary256/64ip) точності [7, c. 216]. Структура формату одинарної точності наведена на рисунку 2.

Рисунок 2 – Структура формату pbinary128/32ip (Індекс р – постбінарне кодування; S, E і M – поля знака, порядку і мантиси; MF і CF – модифікатор і код формату) [7, с. 207]

Для кодування тетралогіки в сучасній бінарної логіки були запропоновані відповідності:

- 01 – Логічний

0

- 10 – Логічна

1

- 00 – стан

А

– абсолютна невизначеність (невідомо, чиІстина

абоБрехня

), що можна представити в вигляді об'єднання даних множин - 11 – стан

М

– Множинність, багатозначність (іістина

ібрехня

одночасно

Згідно рисунку 2, розглянутий формат має дві частини (умовно ліву

– left border, діапазон [127:68] і праву

– right border, діапазон [67:8]) для опису відповідних меж інтервалу. Для кончини даних в цьому форматі використовуються принципи постбінарного кодування, а в якості кодової системи застосовується тетракод [7, c. 53-59].

Оскільки структура постбінарного інтервального формату для кожного кордону однакова, то обчислювальний блок АЛУ для підтримки цього формату може бути спроектований так, щоб в єдиний момент часу робити вибірку однієї межі кожного з двох операндів для виконання арифметичних (або, точніше, інтервальних) і логічних операцій. Такий підхід відповідає виконанню класичних інтервальних операцій [4, с. 31-32]. І забезпечує скорочення апаратних витрат на побудову даного постбінарного ітервального арифметичне–логічного пристрою, так як фактично кількість можливо використовуваних блоків скорочується вдвічі.

3. Апаратна модель

Для розробки апаратної моделі постбінарного інтервального АЛУ (надалі ПІАЛУ, PIALU) була вибрана мова проектування VHDL – мова опису апаратури інтегральних схем, який є базовою мовою при розробці апаратури сучасних обчислювальних систем. Надалі використання VHDL для розглянутого блоку дозволить спроектувати FPGA–рішення, що на початковому етапі зробить продуктивними дослідження моделі пристрою (одержання тимчасових діаграм, моделювання нестандартних ситуацій), а в наступних – виконати його фізичну реалізацію.

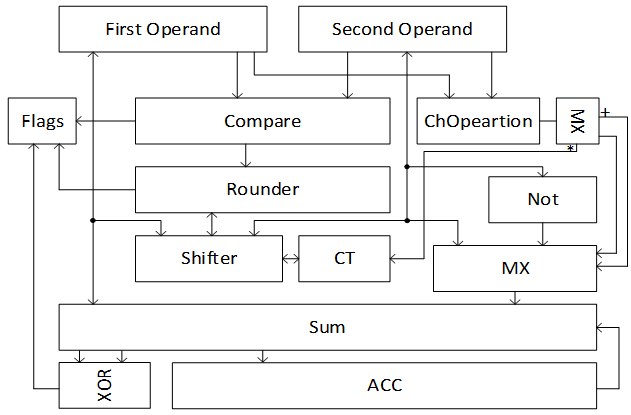

Поточний варіант ПІАЛУ передбачає реалізацію чотирьох основних інтервальних операцій: додавання, віднімання, множення і ділення. Схема ПІАЛУ зображена на рисунку 3.

Рисунок 3 – Структурна схема ПІАЛУ

Структурна схема на рисунку 3 має узагальнений характер, але дає чітке уявлення про деякі кількісних і якісних показників розроблюваного обчислювального пристрою. У ПІАЛУ все реєстрові блоки (First Operand

, Second Operand

, ACC

) мають повне структурне відповідність формату pbinary128/32ip. Блок Compare

– компаратор, здатний порівнювати два тетракодових слова, а блок Rounder

– блок, в якому виконується постбінарное округлення [1, с. 211-219]. Блок ChOperation

дозволяє вибрати тип операції (сложние, віднімання, множення, ділення), а мультиплексори MX, залежно від операції і знаків операндів, дозволяють подати на суматор Sum

операнди в потрібному порядку. У схемі також використовуються сдвігатель Shifter

, регістр прапорів Flags

, лічильник CT

. Акумулятор ACC використовується для реалізації постбінарного множення [1, с. 254-255].

Робота однотетрітного суматора з повним перебором вихідних даних зображена на рисунку 4, яка повністю відповідає таблиці постбінарного складання [1, с. 103]. Де:

А

– перший операнд;B

– другий операнд;- ie – вхідний перенос (в нашому випадку зафіксований в значенні

01

, що відповідає бінарним 0); - oe – вихідний перенос;

- S – сума

Рисунок 4 – Часова діаграма роботи однотетрітного суматора

(анімація:670х370px, 17 кадрів, 3 цикла повторення, 50 кілобайт)

4. Очікувані результати

Фінальним етапом роботи є отримання повноцінної апаратної моделі ПІАЛУ, яке дозволить виконувати елементарні арифметичні дії (додавання, віднімання, ділення, множення) з числами, представленими в постбінарному інтервальному форматі 128/32ip, і подальша реалізація на FPGA платі, так як реалізація на замовний БІС є дуже дорогою.

Апаратна модель дозволить простежити логічні особливості постбінарної арифметики, поведінка кожного окремого блоку при надходженні різних наборів вихідних даних, оцінити ефективність постбінарного підходу.

Так як, для побудови апаратної моделі використовується мова VHDL, це дозволить з легкістю реалізувати даний проект на FPGA–рішеннях, доступних в лабораторіях ДонНТУ (Xilinx Spartan–3E Starter Kit). Тестування та налагодження на FPGA–платі, дозволить наблизиться до наступного етапу розробки – фізичної реалізації ПІАЛУ.

Висновки

Проведено аналіз поточного стану комп'ютерних обчислень з плаваючою комою. Розглянуто можливість використання інтервальних обчислень та особливості їх постбінарної реалізації. Запропоновано використання постбінарних інтервальних форматів одинарної і подвійної точності для організації комп'ютерних обчислень з плаваючою комою. Обгрунтовано проектування і реалізація постбінарного інтервального арифметико–логічного пристрою. Озвучені плани на майбутнє.

При написанні даного реферату магістерська робота ще не завершена. Остаточне завершення: грудень 2014 року. Повний текст роботи та матеріали по темі можуть бути отримані у автора або його керівника після зазначеної дати.

Список літератури

- Аноприенко А. Я. Тетралогика, тетравычисления и ноокомпьютинг. Исследования 2010–2012. / А. Я. Аноприенко, С. В. Иваница — Донецк: ДонНТУ, Технопарк ДонНТУ УНИТЕХ, 2012. — 308 с.

- Юровицкий В. М. IEEE754–тика угрожает человечеству МФТИ, РГСУ, Москва. — Інтернет–ресурс. – Режим доступу: http://www.yur.ru.

- IEEE 754 – стандарт двоичной арифметики с плавающей точкой. — Інтернет–ресурс. – Режим доступу: http://www.softelectro.ru/teoriy.html.

- Добронец Б. С. Интервальная математика: Учеб. пособие / Б. С. Добронец; Краснояр. гос. ун–т — Красноярск, 2004. — 216 с.

- Moore R. E. Introduction to interval analysis. / R.E. Moore, R.B. Kearfott, M.J. Cloud — Philadelphia: SIAM, 2009. — p. 223.

- Аноприенко А. Я., Иваница С. В. Интервальные вычисления и перспективы их развития в контексте кодо–логической эволюции. / А. Я. Аноприенко, С. В. Иваница. // Научные труды Донецкого национального технического университета. Серия «Проблемы моделирования и автоматизации проектирования динамических систем» (МАП–2010). Выпуск 8 (168): Донецк: ДонНТУ, 2010. — С. 150–160.

- Аноприенко А. Я. Постбинарный компьютинг и интервальные вычисления в контексте кодо–логической эволюции. / А. Я. Аноприенко, С. В. Иваница — Донецк: ДонНТУ, УНИТЕХ, 2011. — 248 с.

- Анопрієнко О. Я. Принцип роботи, структура і моделювання блоку перетворювача форматів у складі постбінарного співпроцесора. / О. Я. Анопрієнко, С. В. Іваниця, С. В. Кулібаба // Міжнародний науково–технічний журнал «Інформаційні технології та комп’ютерна інженерія», № 1 (26). — Вінниця, 2013. — С. 59–65.

- Kahan W. Lecture Notes on the Status of IEEE Standard 754 for Binary Floating–Point Arithmetic / W. Prof. W. Kahan — Elect. Eng. & Computer Science, Berkeley, 1997 — р. 30.