Аннотация

О.Е. Новикова, А.В. Лавшонок Повышение эффективности микропроцессорной системы импульсно-фазового управления. Разработан программный алгоритм СИФУ для трехфазного нереверсивного мостового выпрямителя на базе микроконтроллера AVR серии ATMega.

В процессе развития науки и техники повышаются требования к производственным процессам. Поскольку аналоговые системы не всегда удовлетворяют поставленным задачам, все большую актуальность приобретают системы цифрового управления.

Поэтому возникла необходимость разработки микропроцессорной системы управления для 3-х фазного нереверсивного мостового выпрямителя.

Эффективность алгоритма управления микропроцессорной системы импульсно фазового управления определяется следующими параметрами:

- Возможность реализации алгоритма на базе недорогих однокристальных микроконтроллеров.

- Точность выполнения временных задержек для каждого выходного канала.

- Гибкость алгоритма, позволяющего без существенных доработок изменять порядок коммутации, в том числе введение дополнительных функций.

Возможные варианты платформ для реализации алгоритма управления:

- AVR – 8-битные микроконтроллеры. Большинство инструкций выполняется за один такт. Поддерживают прерывания. Возможна реализация ШИМ, но имеют низкую тактовую частоту;

- Arduino – платформа для быстрой разработки различных электронных систем. Проста в освоении, но дорогостоящая и характеризуется низким быстродействием;

- STM32 – 32-разрядный микроконтроллер на основе ядра ARM Cortex-M. Подсемейство Cortex-M предназначено для устройств отличающихся невысокой стоимостью и низким энергопотреблением. По стоимости микроконтроллеры STM32 сопоставимы, а иногда дешевле AVR, однако выпускаются в малогабаритных корпусах LQFP и BGA, затрудняющих моделирование и практическую реализацию в производстве;

- MCS, MSP430, PIC – довольно распространенные семейства микроконтроллеров по характеристикам не превосходящие выше перечисленные.

Каждое из рассмотренных решений обладает своими достоинствами и недостатками, поэтому для разработки был принят наиболее доступный и распространенный вариант – микроконтроллер AVR серии ATMega. Его преимущество в том, что возможно программирование на языке высокого уровня C и моделирование работы МК в среде пакета Proteus, что позволяет на предварительном этапе оценить эффективность алгоритмических решений.

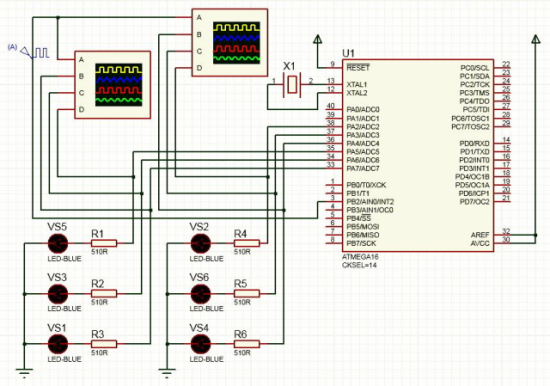

Модель для исследования быстродействия программного решения представлена на рисунке 1.

Рисунок 1 – Модель трехфазного тиристорного моста на примере светодиодов в среде Proteus

Реализация алгоритма СИФУ сводится к управлению тиристорами с осуществлением заданных временных задержек с высокой точностью. Временные задержки требуется осуществлять независимо для каждого из каналов, а время отсчитывается от входа синхронизации. Для отсчета времен средствами микроконтроллера удобно использовать встроенные интегральные таймеры, причем учитывая длительность счета и требования к точности счета, эти таймеры должны быть как минимум шестнадцатибитные. При этом такие таймеры должны быть независимые для каждого канала, что не реализовано в доступных микроконтроллерах. Второй подход состоит в отсчете времени при помощи виртуальных счетчиков, модифицируемых при прерывании по переполнению одного интегрального таймера. Такой подход позволяет реализовать простой алгоритм СИФУ, отличающийся гибкостью и универсальностью. Однако параметры точности в данном случае будут определяться периодом прерываний и на практике для микроконтроллеров серии AVR составят 50-100мкс, что в некоторых случаях не допустимо. Альтернативным способом является принцип осуществления временных задержек при помощи виртуальных счетчиков, которые модифицируются в основном цикле программы. При этом счетчики модифицируются на величину времени, которое физически отсчитывается одним встроенным интегральным таймером, при переполнении которого прерывания не осуществляются. Для синхронизации при этом может быть использован вход микроконтроллера, при изменении сигнала на котором формируется прерывание INT.

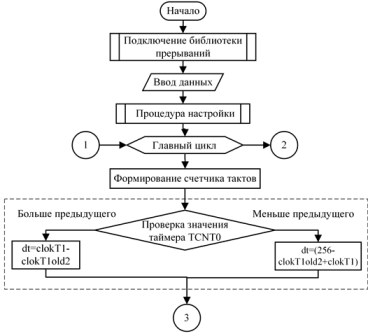

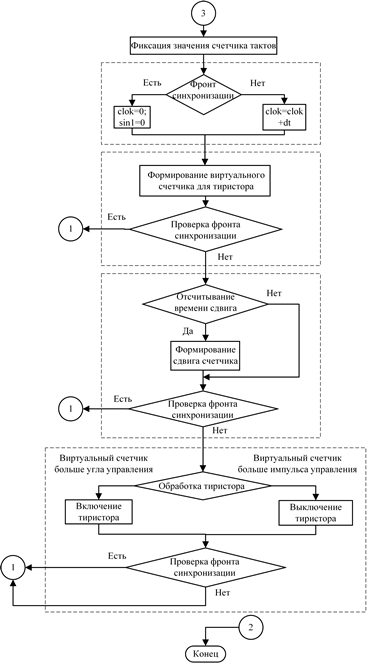

Алгоритм, реализующий описанный выше принцип для схемы на рисунке 1 приведен на рисунках 2 и 3. Практически алгоритм для моделирования и дальнейшего использования реализован на языке C.

Рисунок 2.1 – Блок-схема программного алгоритма

Рисунок 2.2 – Блок-схема программного алгоритма (продолжение)

В предложенной схеме, алгоритме и программе источником синхронизации является вход PB2, с которым ассоциировано прерывание INT2. Для отсчета времени используется интегральный таймер Timer0, осуществляющий счет каждые 0,5мкс.

При появлении нарастающего фронта на входе синхронизации PB2 в процедуре обработчика прерываний устанавливается флаг синхронизации sin1, после в главном цикле программы основной счетчик синхронизации clok сбрасывается и начинает отсчет времени. Одновременно с этим сбрасывается флаг синхронизации sin1.

Далее формируются виртуальные счетчики для каждого тиристора (clok, clokAP, clokBP, clokCP, clokAM, clokBM, clokCM). Переменные счетчиков применены типа long int, что позволяет отсчитать до 2 147 483 647 интервалов по 0,5мкс что составляет более 17 минут.

При работе программы виртуальные счетчики модифицируются путем прибавления величины dt, которая соответствует величине времени отсчитанного интегральным таймером за время одного цикла программы. Когда значение clok превысит значение переменной fazaSTART, начнется отсчет времени для первого тиристора clokAP. Поскольку необходимо управлять работой трехфазной мостовой схемы, импульсы управления тиристорами будут поступать с интервалом 60°. Следовательно, и виртуальные счетчики, будут формироваться последовательно друг за другом каждые 60°. При помощи переменной faza60 отсчитывается 3,333 мс, что соответствует 60°. Когда значение счетчика clokAP превысит значение faza60, начнется отсчет виртуального счетчика clokCM для второго тиристора и т.д. При сбросе базового счетчика все последующие досчитываются автономно.

Угол управления α тиристорами задается переменной faza. Далее значение каждого виртуального счетчика сравнивается со значением угла управления α. Если значение счетчика тиристора больше, чем значение переменной faza – на выход поступает логическая единица, то есть выдается сигнал управления. Таким образом, реализуется вертикальный принцип управления. Длина импульса задается переменной dlina. Алгоритм позволяет осуществлять произвольное число импульсов за период длительностью от 20мкс и выше.

Разработанный алгоритм требует коррекции для отдельно взятых тиристоров по следующим причинам:

- флаг синхронизации проверяется после каждой операции, и эти проверки дают погрешность 1-2 мкс;

- таймер Timer0 работает на высокой частоте, и момент синхронизации крайне редко или вовсе не будет совпадать с нулевым значением счетного регистра таймера, что приводит к дополнительной погрешности 0,5 мкс;

- при совпадении момента отпирания тиристора с синхронизацией, возможна погрешность до 20 мкс.

Погрешность проверки синхронизации для каждого тиристора корректируется с помощью констант fazaKor. Каждая из них учитывается при обработке очередного тиристора, то есть при формировании импульса управления.

Для устранения совпадения момента коммутации какого-либо тиристора с моментом синхронизации по прерыванию исключены некоторые углы.

Запретными углами, учитывая, что для трехфазной мостовой схемы импульсы управления следуют друг за другом каждые 60°, а диапазон регулирования угла управления α для активной нагрузки составляет от 0° до 120°, являются 0°, 60°, 120°.

Таким образом, разработанный алгоритм позволяет построить эффективную СИФУ, отличающуюся:

- Высокой точностью формирования временных задержек синхроимпульсов. Погрешность составляет 1-2мкс.

- Алгоритм позволяет гибко настраивать и наращивать возможности путем подключения дополнительных тиристоров и изменения принципов подачи управляющих сигналов, что позволит применять данное СИФУ для любых устройств, где они необходимы.

- Алгоритм является переносимым и может быть выполнен на более мощном микроконтроллере.

- Синхронизация производится по одной фазе для многофазного устройства, что существенно упрощает схемную реализацию канала управления, особенно для напряжений 660В и выше.

Перечень ссылок

- Datasheet. ATmega16(L)/ Электронный ресурс. Режим доступа: http://www.atmel.com/...

- Программирование на языке C для AVR и PIC микроконтроллеров./ Сост. Ю.А. Шпак – К.: «МК-Пресс», 2006. 400 с., ил.