УДК 004.274 DOI: 10.30748/soi.2017.148.06

И.Я. Зеленева, С.С. Грушко, Д.В. Арапин

Запорожский национальный технический университет, Запорожье

## ЭКСПЕРИМЕНТАЛЬНОЕ ИССЛЕДОВАНИЕ МЕТОДОВ ОПТИМИЗАЦИИ АППАРАТУРНЫХ ЗАТРАТ ПРИ РЕАЛИЗАЦИИ УПРАВЛЯЮЩЕГО АВТОМАТА МУРА НА CPLD

В статье рассмотрены результаты экспериментального исследования способов уменьшения разрядности входного кода в структуре управляющего автомата Мура при реализации в базисе CPLD. В ходе исследований были выведены формулы для оценки требуемой площади кристалла CPLD, а также определен коэффициент отношения практического числа используемых макроячеек и теоретически рассчитанного количества логических вентилей, необходимых для реализации схемы управляющего автомата. Полученный коэффициент позволяет заранее оценить стоимость реализации проекта. Исследования проведены на основе алгоритма управления бортовым цифровым вычислительным комплексом.

**Ключевые слова:** управляющий автомат, CPLD, псевдоэквивалентные состояния, аппаратурные затраты, макроячейка, алгоритм управления.

### Введение

Сегодня применение программируемых логических интегральных схем (ПЛИС) - распространенная практика при производстве электроники в самых различных отраслях. Использование современных ПЛИС при проектировании любых сложных цифровых устройств, включая и встроенные системы, обеспечивает выигрыш по габаритам, потребляемой мощности и функциональности конечного продукта по сравнению с применением не только стандартных логических микросхем, но и микроконтроллеров, микропроцессоров, сигнальных процессоров. В данной статье рассматриваются ПЛИС типа CPLD (complex programmable array logic devices), на базе которых решена задача синтеза и оптимизации логических схем устройств управления, являющихся важной частью практически любой цифровой системы. Устройство управления в виде микропрограммного управляющего автомата (МПА), реализованное на базе CPLD, обеспечивает выполнение всех необходимых функций для решения поставленных задач при умеренных материальных затратах.

В работе рассматривается актуальная научнопрактическая задача оптимизации схемы устройства управления по критерию аппаратурных затрат за счет уменьшения разрядности входного кода. Целью исследования является экспериментальное определение степени эффективности различных методов уменьшения разрядности входного кода в матричных структурах управляющих автоматов в базисе СРLD. Предметом исследования являются входные и выходные параметры управляющего автомата Мура, внутренние макроячейки микросхемы СРLD, в которые имплементируются модели, а также временные диаграммы работы оптимизированных схем управляющих автоматов.

Методы исследования основываются на известных из литературы теоретических способах уменьшения разрядности входного кода в структуре управляющего автомата Мура, а также программных инструментах для синтеза и имплементации. Достоверность результатов обеспечивается корректностью постановки задачи, системным подходом к исследованию, а также подтверждением основных теоретических положений практическими результатами.

В качестве исходных данных для синтеза и дальнейшего исследования схем микропрограммного автомата Мура используется алгоритм функционирования блока управления конфигурацией бортового цифрового вычислительного комплекса (БУК БЦВК), представленный в виде граф-схемы алгоритма (ГСА).

#### Постановка задачи исследования

Любое цифровое устройство можно структурно разделить на управляющую часть и исполнительную, т.е. управляющий и операционный автомат [1]. При этом операционный автомат обеспечивает собственно обработку информации по заданному алгоритму, а управляющий автомат как раз обеспечивает порядок функционирования операционной части в строгом соответствии с этим алгоритмом.

При проведении данных экспериментальных исследований нас интересует управляющий автомат, представленный в виде микропрограммного автомата Мура [1; 3], который теоретически может быть описан, как вектор

$$S = \langle A, X, Y, \delta, \lambda, a_1 \rangle \tag{1}$$

В векторе (1) имеются следующие компоненты:  $A = \left\{a_1,...,a_M\right\} - \text{множество внутренних состояний,}$   $X = \left\{x_1,...,x_L\right\} - \text{множество входных переменных,}$   $Y = \left\{y_1,...,y_N\right\} - \text{множество выходных переменных автомата, } \delta - \text{функция переходов; } \lambda - \text{функция выходов автомата Мура; } a_1 \in A - \text{исходное состояние МПА. Функции } \delta$  и определяются следующим образом:

$$a_s = \delta(a_m, X),$$

где  $a_1 \in A;$  (2)

$$y_n = \lambda(a_m),$$

где  $y_n \in Y$  . (3)

Функция  $\delta$  служит для определения состояния перехода  $a_s \in A$  в зависимости от текущего состояния  $a_m \in A$  и вектора входных переменных. Из (3) следует, что выходные переменные автомата Мура зависят только от состояний, что будет использовано при дальнейшем проектировании.

Поскольку данные исследования проводятся в базисе CPLD с макроячейками типа PAL (programmable array logic), рассмотрим некоторые особенности проектирования логической схемы управляющего автомата Мура на интегральных схемах с матричной структурой, к которым относится CPLD [2; 5–7].

Логическая схема МПА Мура задаётся системой булевых функций, соответственно (2) и (3):

$$\Phi = \Phi(T, X), \qquad (4)$$

$$Y = Y(T), (5)$$

где для представления состояний используются внутренние переменные, образующие множество  $T=\left\{T_1,...,T_R\right\}$ . Кодирование состояний  $a_m\in A$  двоичными кодами  $K(a_m)$  разрядности R, где  $R=\left[\log_2 M\right]$  и M — число состояний автомата Мура. Для изменения содержимого регистра памяти состояний автомата RG используют функции возбуждения памяти, образующие множество  $D=\left\{D_1,...,D_R\right\}$  [1; 3]. Переменная  $D_r$  поступает на вход r-го D-триггера (  $r=\overline{1,R}$  ) регистра RG, распределенного среди матричных ресурсов микросхемы CPLD [8–11]. Отметим, что на основании вышесказанного функция (4) далее используется в виде

$$D = D(T,X). (6)$$

В соответствии с (3) и (4) выходные сигналы Y зависят только от состояний автомата [3; 5]. Фактически коды состояний  $K(a_m)$  могут также являться и кодами наборов микроопераций, записанных в опе-

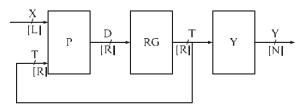

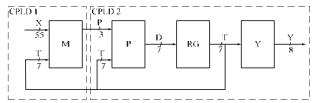

раторных вершинах, которые отмечают состояниями  $a_m \in A$ . Это порождает (с учетом общей матричной структуры ПЛИС) матричную структуру логической схемы автомата Мура (рис. 1), содержащую Р-подсхему для реализации (4) и Y-подсхему для реализации (5). Подсхемы реализуются на внутренних компонентах типа PLA (programmable logic аггау), что соответствует понятию ПЛМ (программируемая логическая матрица).

Рис. 1. Матричная структурная схема автомата Мура

Для дальнейших исследований нас особенно интересуют параметры: L – число входных сигналов МПА Мура, R – разрядность кода состояния, N – число выходных сигналов автомата.

Как видно из рис. 1, в простейшем случае автомат Мура представляется двухуровневой структурой. При реализации схемы автомата в базисе CPLD системы (4) и (5) реализуются на макроячейках PAL или PLA [6; 7]. Основой для синтеза схемы автомата является прямая структурная таблица (ПСТ) [1; 3], формируемая по исходной граф-схеме алгоритма. По ПСТ строится система (4) в виде:

$$\phi_r = \bigvee_{h=1}^{H} C_{rh} A_m^h X_h = \bigvee_{h=1}^{H} C_{rh} F_h \quad (r=1,...,9),$$

(7)

где  $C_{rh}$  – булева переменная, равная единице, если и только если в h-й строке ПСТ  $D_r$ =1.

Для синтеза Y-подсхемы необходимо построить таблицу микроопераций со столбцами  $a_m$ ,  $K(a_m)$ ,  $Y_m$ , m, где в столбце  $Y_m$  записаны микрооперации, формируемые в состоянии  $a_m \in A$ .

При этом система (5) должна быть представлена в виде ДНФ [1]:

$$y_n = V_{m=1}^M C_{nm} A_m \quad (n=1,...,N),$$

(8)

где  $C_{nm}$  – булева переменная, равная единице, если и только если в состоянии  $a_m$  вырабатывается микрооперация  $y_n$ .

Для синтеза Р-подсхемы применяются известные общие методы реализации систем булевых функций на ПЛИС [2; 5]. В наших исследованиях обратим внимание на особенности архитектуры ПЛИС СРLD.

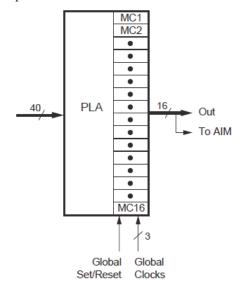

Архитектура CPLD напоминает архитектуру ПЛМ, когда логические ресурсы реализуются массивом элементов И, объединенных элементами ИЛИ, в свою очередь заведенным на триггеры или

непосредственно на выход микросхемы [8-11]. Такая логическая структура достаточно проста для понимания, обеспечивает чрезвычайно короткое время компиляции и минимальные задержки pin-topin. CPLD состоят из блоков макроячеек, объединенных программируемой коммутационной матрицей. Современные CPLD, как правило, электрически перепрограммируемы и сохраняют логическую структуру после отключения питания. CPLD различных фирм-изготовителей и разной сложности имеют функциональные блоки (рис. 2), которые в принципиальном отношении мало отличаются друг от друга по своей архитектуре и составу элементов. Однако всем микросхемам свойственны ограничения по количеству входов макроячеек и числу внутренних термов в функциональных блоках. Эти ограничения приходится учитывать при проектировании, для чего нужно заранее определять размерности систем булевых функций, реализуемых на данной микросхеме.

Рис. 2. Обобщенная структура функционального блока CPLD

В процессе проектирования управляющих автоматов нередко возникает ситуация, при которой количество входных сигналов проектируемого устройства больше, чем предусмотрено производителями ПЛИС для обработки задач определенной размерности. Иными словами, задача имеет большую размерность, чем соответствующие параметры микросхемы. Такая ситуация приводит к необходимости использовать микросхемы большей площади, в результате чего аппаратурные, а значит, и материальные затраты на разработку управляющего автомата существенно увеличиваются.

Для уменьшения аппаратурных затрат при синтезе логических схем управляющих автоматов можно применять методы структурной редукции, гетерогенной реализации, алгоритмические методы [4;

6–7]. В литературе также описаны методы уменьшения разрядности входного кода в структуре управляющего автомата. К ним относятся метод замены входных переменных [13], а также метод классов псевдоэквивалентных состояний [7; 15], которые далее будут рассмотрены в исследованиях. Однако при использовании любых методов структурной оптимизации в схему МПА вносятся изменения, которые могут повлиять на производительность разрабатываемого устройства.

Таким образом, в задачи данного исследования входит:

- анализ способов уменьшения разрядности входного кода в матричных структурах управляющих автоматов;

- разработка базовой модели МПА Мура на ПЛИС СРLD;

- разработка модели МПА Мура с применением способа замены входных переменных;

- разработка модели МПА Мура с применением способа псевдоэквивалентных состояний;

- экспериментальное исследование разработанных моделей МПА Мура с помощью программного пакета Aldec Active-HDL 9.1 с последующим синтезом и имплементацией в микросхемы Xilinx [16], широко применяющиеся в настоящее время, наряду с микросхемами фирм Altera и др. [10, 11].

# Анализ теоретических источников и обоснование стратегии исследований

Для разработки модели МПА Мура с последующим применением различных способов уменьшения разрядности входного кода используем базовую модель (рис. 1), которая будет составлять основу для всех последующих моделей оптимизации. Назовем базовую модель Р-автомат. В простейшем случае, описанном в литературе [6], автомат Мура представляется двухуровневой структурой, в которой система функций возбуждения памяти (СФВП) (7) реализуется на ПЛМ или ПМЛ, а система функций выходных сигналов (СФВС) (8) - на ППЗУ (программируемом постоянном запоминающем устройстве, также имеющем матричную структуру). На данный момент этот элементный базис уже достаточно устарел и здесь используется в качестве базовой теоретической информации. В дальнейшем будут проведены необходимые преобразования, ориентированные на новый базис CPLD.

Оптимизация схем P-автомата возможна путём различных подходов к кодированию логических условий (ЛУ)  $x_1 \in X$  [12], а также путем замены входных переменных – этот метод подробно описан в литературе [6–7; 13]. Суть метода замены входных переменных состоит в следующем. Пусть в ПСТ в

массиве переходов из состояния  $a_m \in A$  встречается множество переменных  $X(a_m)$  мощностью  $L_m$ . На практике  $L_m << L$ . Пусть  $G=\max(L_1,...,L_M)$ , образуем новое множество  $P=\{p_1,...,p_G\}$  и для каждого  $a_m \in A$  построим функцию  $X(a_m)=P$ . После этого можно перейти от множества логических условий X к множеству кодирующих переменных P, где G<< L, следующим образом: в состоянии  $a_m$  переменная  $x_l \in X(a_m)$  заменяется переменной  $p_g$ , такой, что при  $A_m=1$   $p_g=x_l$  [6]. Таким образом:

$$P_{g} = \bigvee_{m=1}^{M} \bigvee_{l=1}^{L} C_{ml} A_{m} x_{l} \quad (g=1,...,G),$$

(9)

где  $C_{ml}$  – булева переменная, равная единице, если и только если переменная  $p_{g}$  соответствует в состоянии  $a_{m}$  переменной  $x_{l}$ .

Теперь система функций (4) и (5), с учетом (6), может быть заменена системой функций [6]:

$$P = P(T,X), \tag{10}$$

$$Y = Y(T), \tag{11}$$

$$D = D(T,P). (12)$$

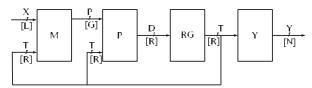

Это порождает MP-автомат (рис. 3), в котором появляется М-подсхема, реализуемая на мультиплексорах [6–7; 13] и формирующая функции (10). При этом P-подсхема реализуется на ПЛМ и формирует функции (11) и (12). Метод синтеза MP-автомата включает следующие этапы:

- формирование таблицы замены X → P;

- формирование преобразованной ПСТ МРавтомата;

- реализация систем функций (11–12) в заданном элементном базисе.

Основной целью замены входных переменных, очевидно, является оптимизация необходимого числа входов матричной структуры управляющего автомата.

Рис. 3. Структурная схема МР-автомата

Рассмотрим еще один способ оптимизации схемы МПА Мура по критерию аппаратурных затрат – метод псевдоэквивалентных состояний [4; 6–7]. Как видно, в силу зависимости (5), каждая операторная вершина ГСА отмечается отдельным состоянием. Отметим, что в определенной степени недостатки автомата Мура связаны с тем, что при синтезе формул для функций переходов и выходных сигналов по ПСТ необходимо рассматривать переходы из всех операторных вершин, в то время как в автомате Мили, в принципе рассматриваются переходы из групп операторных вершин. Этот факт может быть

использован для сжатия таблицы переходов автомата Мура до длины таблицы переходов эквивалентного автомата Мили [4–7].

Назовём состояния  $a_m$ ,  $a_s \in A$  автомата Мура, соответствующие вершинам, выходы которых на ГСА объединены, псевдоэквивалентными состояниями (ПЭС) [6].

Построим разбиение  $\Pi_A=\{B_1,\ldots,B_I\}$  множества состояний A на классы псевдоэквивалентных состояний таким образом, что каждый класс  $B_i$  разбиения  $\Pi_A$  соответствует одному состоянию эквивалентного автомата Мили. Если каждый класс  $B_i\in\Pi_A$  идентифицировать одним объектом, то можно построить сокращённую ПСТ автомата Мура, столбец которой  $a_m$  заменен столбцом  $B_i$ . Сокращённая ПСТ строится следующим образом [6]:

- в столбце  $B_i$  состояние  $a_s \in B_i$  исходной ПСТ заменяется классом  $B_i$ ;

- из  $M_i$ = $|B_i|$  одинаковых подтаблиц ПСТ остаётся только одна, таким образом, каждому классу  $B_i \in \Pi_A$  соответствует только одна подтаблица.

Таким образом, однозначная идентификация классов псевдоэквивалентных состояний позволяет уменьшить длину ПСТ автомата Мура [4; 6–7].

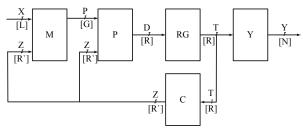

Комплексное применение методов замены входных переменных и псевдоэквивалентных состояний порождает структуру МПА Мура, называемую МРС-автомат (рис. 4). При этом важно соблюдение условий R < R и G < L.

При реализации кодирования классов ПЭС структурная схема МПА модифицируется и в ней появляется преобразователь кодов, условно называемый С-подсхемой. В нашем случае в качестве базовой структурной схемы возьмем схему МРавтомата (рис. 3), в виду того что в комплексе с методом замены входных переменных предполагается вполне существенное уменьшение разрядности входного кода, а также уменьшение числа термов в системе функций возбуждения памяти за счет сжатия таблицы ПСТ.

Рис. 4. Структурная схема МСР-автомата Мура

Применение любого из рассмотренных методов оптимизации входного кода МПА Мура привносит в схему дополнительные функциональные узлы — преобразователи кодов. Известны условия целесообразности: методы можно применять, если в ре-

зультате общие аппаратурные затраты уменьшаются. Логично предположить также, что внесение в схему новых функциональных узлов отразится на быстродействии. Таким образом, эффективность применения рассмотренных методов оптимизации может быть очень разной (вплоть до нецелесообразности) и зависит от свойств элементного базиса и параметров заданной ГСА. Поэтому стратегической задачей данных исследований является определение степени эффективности методов замены входных переменных и псевдоэквивалентных состояний путем проведения экспериментов с имплементацией схем МПА Мура в различные микросхемы CPLD. Наиболее известными производителями микросхем CPLD являются фирмы Xilinx и Altera. В результате анализа логических и физических характеристик микросхм [10; 11] было принято решение использовать микросхемы фирмы Xilinx серии CoolRunner II.

# Оценка параметров исследуемых моделей автомата Мура

Примем модель МПА Мура на рис. 1 в качестве базовой для дальнейших исследований. Для оценки возможности размещения полученных в результате синтеза схем автомата в реальных микросхемах необходимо рассчитать предполагаемую площадь занимаемого кристалла. Так как в СРLD все структурные компоненты располагаются на одном кристалле, формула расчета оценки занимаемой площади будет составлять сумму оценок всех составляющих компонентов. Исходя из структурной схемы МПА Мура (рис. 1), формула, ориентированная на предшествующий базис, будет иметь вид [6]:

$$S_{P} = S_{PLA} + S_{PROM}, \tag{13}$$

где S<sub>P</sub> – общая площадь кристалла CPLD;

$S_{PLA}$  — площадь кристалла, занимаемая Р-подсхемой;

$S_{PROM}$  – площадь кристалла, занимаемая Y-подсхемой.

Формула для расчета площади  $S_{PLA}$ :

$$S_{P} = 2 \cdot (L + R) \cdot H + R \cdot H, \qquad (14)$$

где 2 – константа, отражающая наличие парафазного входа;

L – мощность множества входных сигналов |X|;

R – разрядность кода состояния |T|;

H – число термов в прямой структурной таблице автомата Мура.

Однако, ввиду того, что внутри современных CPLD Y-подсхема функционально реализована не на PROM, а на PLA, формула для вычисления S<sub>PROM</sub> (15) преобразуется согласно структурным особенностям PLA:

$$S_{PROM} = 2 \cdot R \cdot 2R + 2R \cdot N, \tag{15}$$

где  $2^R$  – число внутренних термов Y-подсхемы;

N – число выходных сигналов Y-подсхемы.

Таким образом, получаем:

$$S_P = 2 \cdot (L + R) \cdot H + R \cdot H + 2 \cdot R \cdot 2R + 2R \cdot N.$$

(16)

Примем полученную формулу (16) как базовую для расчета оценки занимаемой площади кристалла CPLD.

После анализа актуальных на данных момент микросхем CPLD было принято решение использовать для дальнейших исследований микросхемы серии Coolrunner II производства фирмы Xilinx.

Первым из исследуемых методов уменьшения разрядности входного кода является метод замены входных переменных (МР-автомат, рис. 3). Как было сказано ранее, М-подсхема выполняет функции мультиплексирования, поэтому здесь введем условное обозначение  $S_{\text{MUX}}$ . Преобразуя выведенную ранее формулу расчета оценки занимаемой площади (13) для MP-автомата получим:

$$S_{P} = S_{PLA} + S_{PROM} + S_{MUX}, \qquad (17)$$

где  $S_{MUX}$  — площадь кристалла, занимаемая М-подсхемой.

Исходя из того, что в CPLD М-подсхема функционально реализована на PLA, основываясь на уже известных ранее формулах (14) и (15), а также исходя из структурной схемы MP-автомата (рис. 3) расчет  $S_{\text{MUX}}$  будет выполняться по формуле:

$$S_{MUX} = 2 \cdot (L + R) \cdot M + M \cdot G, \qquad (18)$$

где 2 – константа, отражающая наличие парафазного входа;

М – число термов, полученных при кодировании логических условий методом замены переменных [13; 15];

G – число выходов М-подсхемы.

Формула для вычисления  $S_{PLA}$  (19) также будет отличаться от рассмотренной ранее (14) из-за изменений в структурной схеме (рис. 3) и будет иметь вид:

$$S_{PLA} = 2 \cdot (G + R) \cdot H + R \cdot H. \tag{19}$$

Таким образом, получаем:

$$S_{MP} = 2 \cdot (L + R) \cdot M + M \cdot G + 2 \cdot (G + R) \cdot H + + R \cdot H + 2 \cdot R \cdot 2^{R} + 2^{R} \cdot N.$$

(20)

Примем полученную формулу (20) как формулу расчета оценки занимаемой площади для MP-автомата.

Далее выполним оценку площади кристалла CPLD, необходимой для реализации MCP-автомата. Ввиду того что структурно MCP-автомат отличается от MP-автомата наличием С-подсхемы, выведенную ранее формулу расчета оценки занимаемой площади (17) можно представить для MCP-автомата в виде:

$$S_{P} = S_{PLA} + S_{PROM} + S_{MUX} + S_{CODER}, \qquad (21)$$

где  $S_{CODER}$  — площадь кристалла, занимаемая С-подсхемой;

Исходя из того, что в CPLD С-подсхема функционально реализована на PLA, основываясь на уже известных ранее формулах (14) и (15), а также исходя из структурной схемы МСР-автомата (рис. 4) расчет  $S_{CODER}$  выполняется по формуле:

$$S_{CODER} = 2 \cdot R \cdot 2^{R} + A \cdot 2^{R}, \qquad (22)$$

где 2 – константа, отражающая наличие парафазного входа;

$2^{R}$  — число термов в таблице кодирования классов состояний;

R – число входов С-подсхемы;

А – число выходов С-подсхемы.

Формулы для вычисления  $S_{MUX}$  (23) и  $S_{PLA}$  (24) также будут отличаться от рассмотренных ранее (18) и (19) соответственно из-за изменений в структурной схеме (рис. 4) и будут иметь вид:

$$S_{MUX} = 2 \cdot (L + R') \cdot M + M \cdot G, \qquad (23)$$

$$S_{PLA} = 2 \cdot (G + R) \cdot H + R \cdot H, \qquad (24)$$

Таким образом, получаем:

$$S_{MCP} = 2 \cdot (L + R') \cdot M + M \cdot G + 2 \cdot (G + R') \cdot H + R' \cdot H + 2 \cdot R \cdot 2^{R} + 2^{R} \cdot N + 2 \cdot R \cdot 2^{R} + R' \cdot 2^{R}$$

(25)

Примем полученную формулу (25) как формулу расчета оценки занимаемой площади для МСР-автомата.

# Экспериментальные исследования моделей УА Мура в базисе CPLD

В качестве исходных данных для исследования был использован алгоритм работы бортового управляющего комплекса в виде функционального графа. Фрагмент данного алгоритма был закодирован, и принят как исходный для исследуемой модели.

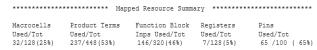

Исследование МР-автомата. Как показала временная диаграмма, модель функционирует корректно, и она готова к синтезу и имплементации в реальную микросхему. Основным критерием выбора является количество входов и выходов микросхемы. Изучив характеристики существующих микросхем СРLD и входные данные автомата, выбор остановился на микросхеме XC2C128-7TQ144C [11], которая позволяет использовать до 100 пользовательских входов и выходов. Результатом синтеза и имплементации являются отчеты, формируемые программным обеспечением. Рассмотрим фрагмент одного из отчетов на рис. 5.

| *******     | *********** Mapp | ed Resource Summary | *******   | ******      |

|-------------|------------------|---------------------|-----------|-------------|

| Macrocells  | Product Terms    | Function Block      | Registers | Pins        |

| Used/Tot    | Used/Tot         | Inps Used/Tot       | Used/Tot  | Used/Tot    |

| 36/128(28%) | 280/448(62%)     | 189/320(59%)        | 7/128(5%) | 65/100(65%) |

Рис. 5. Отчет MP\_FULL.rpt (фрагмент)

Из данного фрагмента видно, что количество используемых входов и выходов составляет 65%, и соответственно большая часть не используется. Для уменьшения разрядности входного кода предлагается разделить структуру автомата на две микросхемы (рис. 6), применяя структурную редукцию [6; 13].

Рис. 6. Структурное разделение МР-автомата

Такой вариант структурного разделения автомата может дать эффект в плане уменьшения общих аппаратурных затрат в схеме, так как на этом участке имеется возможность изменения разрядности входов и выходов Р-автомата.

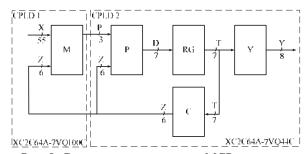

Исследование модели МСР-автомата осуществляется аналогичным образом, как и исследование МР-автомата. На первом этапе выполняется создание VHDL-описания структурных блоков МСР-автомата: мультиплексора, ПЛМ, регистра, преобразователя кода и ППЗУ. На втором — модель проверяется на достоверность функционирования с помощью временных диаграмм.

Используем для имплементации ту же микросхему, что и для MP-автомата – XC2C128-7TQ144C. Рассмотрим фрагмент отчета имплементации на рис. 7.

Рис. 7. Отчет MCP FULL.rpt (фрагмент)

Из данного фрагмента видно, что количество используемых входов и выходов по-прежнему составляет 65%, и соответственно большая часть как их, так и внутренних ресурсов микросхемы попрежнему не используются. Для уменьшения разрядности входного кода разделим структуру автомата на две микросхемы (рис. 8).

Рис. 8. Структурное разделение МСР-автомата

После анализа параметров CPLD на возможность использования пользовательских входов и выходов для реализации CPLD 1 и CPLD 2 были выбраны микросхемы XC2C64A-7VQ100C и XC2C64A-7VQ44C соответственно. Проведем синтез и имплементацию для данных микросхем.

Рассмотрим фрагмент отчета по имплементации для CPLD 1 на рис. 9.

| *******    | ****** Map    | ped Resource Summa | ary ******* | ******      |

|------------|---------------|--------------------|-------------|-------------|

| Macrocells | Product Terms | Function Block     | Registers   | Pins        |

| Used/Tot   | Used/Tot      | Inps Used/Tot      | Used/Tot    | Used/Tot    |

| 3/64(5%)   | 55/224(25%)   | 73/160(46%)        | 0/64(0%)    | 64/64(100%) |

Рис. 9. Отчет MCP\_CPLD1.rpt (фрагмент)

Из данного фрагмента следует, что количество используемых входов и выходов для CPLD 1 составляет 100%, а внутренние ресурсы задействованы менее чем наполовину. Также рассмотрим фрагмент отчета по имплементации для CPLD 2 на рис. 10.

| ************************************** |               |                |           |            |

|----------------------------------------|---------------|----------------|-----------|------------|

| Macrocells                             | Product Terms | Function Block | Registers | Pins       |

| Used/Tot                               | Used/Tot      | Inps Used/Tot  | Used/Tot  | Used/Tot   |

| 29/64(45%)                             | 172/224(77%)  | 46/160(29%)    | 7/64(11%) | 19/33(58%) |

Рис. 10. Отчет МСР CPLD2.rpt (фрагмент)

Этот фрагмент показывает, что количество используемых входов и выходов для CPLD 2 составляет 58%, при этом внутренние ресурсы задействованы более эффективно.

## Выводы по результатам экспериментальных исследований

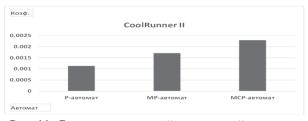

Отметим, что оптимизация моделей не вносит изменений в корректность работы алгоритма. В этом мы можем убедиться, сравнив временные диаграммы Р-автомата, MP-автомата и MCP-автомата.

Проведем сравнение значений расчетной оценки занимаемой площади с числом используемых макроячеек, полученным из отчетов по имплементации (табл. 1).

Таблица 1 Сравнение значений занимаемой площади кристалла

|                                       | 1       |         |         |

|---------------------------------------|---------|---------|---------|

| Модель                                | Р-      | MP-     | MCP-    |

| автомата                              | автомат | автомат | автомат |

| Расчетное<br>значение<br>(лог. вент.) | 31767   | 18689   | 13929   |

| Практическое значение (макроячейки)   | 36      | 32      | 32      |

Рис. 11. Сравнение значений занимаемой площади кристалла

Как видно из табл. 1 и рис. 11, между теоретическим и практическим значением однозначно прослеживается зависимость. Можно предположить, что коэффициент отношения практического значения к теоретическому в среднем составляет 0,0017. Следовательно, при выполнении предпроектной оценки занимаемой площади для микросхем серии CoolRunner II можно пользоваться данным коэффициентом для оценки предполагаемого количества используемых макроячеек.

Рассмотрим экономический эффект от применения оптимизации. Для размещения Р-автомата или MP-автомата в CPLD, учитывая количество входов и выходов, необходимо использовать микросхему XC2C128-7TQ144С стоимостью 8,65\$. При размещении MCP-автомата используются 2 CPLD емкости - XC2C64A-7VQ100C и меньшей XC2C64A-7VQ44C стоимостью 3,8\$ и 3,05\$ [11]. Таким образом, уменьшение разрядности входного кода с помощью совмещения способа замены входных переменных и способа применения псевдоэквивалентных состояний позволяет сократить материальные затраты на 20%. Стоит отметить, что данный эффект наблюдался при использовании микросхем сравнительно небольшого размера, и при увеличении объема алгоритма эффектность оптимизации может быть еще выше. При разработке микросхем в коммерческом и промышленном масштабе данное сокращение материальных затрат выливается в значительную экономию. Также в определенных, не рассмотренных в рамках исследований случаях, раздельное использование каждого из способов уменьшения разрядности входного кода может дать положительный эффект.

При материальной выгоде применения оптимизации существует также отрицательный эффект, который выражается в увеличении временных задержек при передаче сигналов между разделенными микросхемами. Таким образом, реализация схемы автомата на двух микросхемах целесообразна только в тех случаях, когда приоритетным критерием оптимизации является стоимость устройства.

#### Заключение

Результаты, полученные в данных исследованиях, являются решением научно-практической задачи по экспериментальному определению степени эффективности применения способов уменьшения разрядности входного кода в матричных структурах управляющих автоматов в базисе CPLD.

Новизна полученных результатов состоит в том, что выведены формулы для предпроектной оценки площади кристалла CPLD, занимаемой базовой схемой УА Мура, а также модифицированными схемами. Также экспериментальным путем была установлена однозначная зависимость между теоре-

тическими расчетами и практически полученными количественными характеристиками используемых ресурсов микросхемы CPLD. В результате экспериментальных исследований была определена возможная экономическая выгода от использования способов уменьшения разрядности входного кода в структуре управляющего автомата.

### Список литературы

- 1. Baranov S. Logic and System Design of Digital Systems [Текст] / S. Baranov. Tallinn: TUT Press, 2008. 267 p.

- 2. Соловьев В.В. Логическое проектирование цифровых систем на основе программируемых логических интегральных схем [Текст] / В.В. Соловьев, А. Климович. М.: Горячая Линия Телеком, 2008. 376 с.

- 3. Baranov S. Logic Synthesis for Control Automata [Text] / S. Baranov. Boston: Kluwer Academic Publishers, 1994 312 p.

- 4. De Micheli G. Synthesis and Optimization of Digital Circuits [Text] / G. De Micheli. New York: Mc Graw-Hill, 1994. 636 p.

- 5. Czerwinski R. Finite State Machine Logic Synthesis for Complex Programmable Logic Devices [Text] / R. Czerwinski, D. Kania. – Berlin: Springer, 2013. – 172 p.

- 6. Баркалов А.А. Синтез устройств управления на программируемых логических устройствах: учебное пособие [Текст] / А.А. Баркалов. Донецк: ДонНТУ, 2002. 261 с.

- 7. Barkalov A. Reduction in the number of PAL macrocells in the circuit of the Moore FSM [Text] / A. Barkalov, L. Titarenko, S. Chmielewski // International Journal of Applied Mathematics and Computer Science. − 2007, №17. − P. 101-112.

- 8. Сложные программируемые логические устройства (CPLD) [Электронный ресурс]. Режим доступа: http://digteh.ru/digital/CPLD/.

- 9. Технология устройств CPLD [Электронный ресурс]. Режим доступа: https://parallel.ru/fpga/cpld.html.

- 10. Altera documentation [Электронный ресурс]. Режим доступа: www.altera.com.

- 11. Xilinx documentation [Электронный ресурс]. Режим доступа: www.xilinx.com.

- 12. Yang S. Optimum and suboptimum algorithms for input encoding and its relationships to logic minimization [Text] / M. Ciesielski, S. Yang // IEEE Transactions on CAD of Integrated Circuits and Systems. − 1991, №10. − P. 117-131.

- 13. Баркалов А.А. Оптимизация логической схемы устройства управления с заменой переменных [Текст] / А.А. Баркалов, И.Я. Зеленёва // Управляющие системы и машины. Киев, 2001. №1. С. 75-78.

- 14. Garcia-Vargas I. ROM-based finite state machine implementation in low cost FPGAs [Text] / I. Garcia-Vargas, R. Senhadji-Navarro, A. Civit-Balcells, P. Guerra-Gutierrezz // IEEE International Symposium of Industrial electronics. Vigo 2007. P. 342-347.

- 15. Barkalov A. Optimization with Replacement of logical conditions for an automaton with bidirectional transitions [Text] / I. Zelenjova, A. Barkalov // Avtomatics and Computer Science. 2000. №5. P. 48-53.

- 16. Tutorial on Simulation using Aldec Active-HDL [Электронный pecypc]. Режим доступа: https://ece.gmu.edu/sites/ece/files/student-resource/7971/tutorial-simulation-aldec-active-hdl 0.pdf.

Поступила в редколлегию 22.10.2017

**Рецензент:** д-р техн. наук проф. Д.М. Пиза, институт информатики и радиоэлектроники, ЗНТУ, Запорожье.

# ЕКСПЕРИМЕНТАЛЬНЕ ДОСЛІДЖЕННЯ МЕТОДІВ ОПТИМІЗАЦІЇ АПАРАТУРНИХ ВИТРАТ ПРИ РЕАЛІЗАЦІЇ КЕРУЮЧОГО АВТОМАТА МУРА НА CPLD

І.Я. Зеленьова, С.С. Грушко, Д.В. Арапін

У статті розглянуто результати експериментального дослідження способів зменшення розрядності вхідного коду в структурі керуючого автомата Мура при реалізації в базисі СРLD. В ході досліджень були виведені формули для оцінки необхідної площі кристала СРLD, а також визначено коефіцієнт відносини практичного числа використовуваних макроячеек і теоретично розрахованої кількості логічних вентилів, необхідних для реалізації схеми керуючого автомата. Отриманий коефіцієнт дозволяє заздалегідь оцінити вартість реалізації проекту. Дослідження проведені на основі алгоритму управління бортовим цифровим обчислювальним комплексом.

**Ключові слова:** керуючий автомат, CPLD, псевдоеквівалентні стани, апаратурні витрати, макрокомірки, алгоритм керування.

## EXPERIMENTAL RESEARCH OF THE HARWARE EXPENSES OPTIMIZATION METHODS FOR THE MOORE FSM IMPLEMETATION ON CPLD

I. Zeleneva, S. Hrushko, D. Arapin

The article describes the results of an experimental study ways to reduce the bit depth of the input code in the structure of the Moore FSM for the implementation in a CPLD basis. The studies derived formulas for estimating the required area CPLD chip, as well as the defined ratio relationship of practical use of macrocells and the theoretical amount of logic gates needed to implement the schemes of control of the automaton. The resulting ratio enables to assess in advance the cost of the project. Investigations were carried out on the basis of the control algorithm onboard digital computer complex.

Keywords: control automaton, CPLD, pseudoequivalent state, hardware expenses, macrocell, control algorithm.