Разработка базовых компонентов цифровых устройств, реализуемых на базе ПЛИС FPGA фирмы Xilinx с помощью генератора параметризированных модулей CORE Generator

Автор: Зотов В.

Источник: САПР серии Xilinx ISE // Компоненты и Технологии. 2007. №67.

Аннотация

В предыдущей публикации цикла, знакомящего с инструментами САПР серии Xilinx ISE (Integrated Synthesis Environment/Integrated Software Environment), которые повышают эффективность процесса разработки цифровых устройств на основе ПЛИС семейств FPGA (Field Programmable Gate Array) [1], были представлены характеристики, пользовательский интерфейс и методы использования генератора параметризированных модулей CORE Generator [2]. Этот инструмент позволяет в считанные минуты cформировать отлаженные узлы и функциональные блоки проектируемых устройств. В настоящей статье рассматриваются отличительные особенности, технические характеристики и параметры настройки параметризированных модулей базовых компонентов цифровых устройств, поддерживаемых средствами CORE Generator. Все рассматриваемые модули не требуют лицензии на их применение и могут использоваться в любой конфигурации САПР серии Xilinx ISE (ISE Foundation и ISE WebPack) [3,4].

Формирование компараторов с помощью генератора параметризированных модулей CORE Generator

В составе генератора параметризированных модулей CORE Generator представлено несколько версий ядра Comparator vN_M (где N_M — номер версии), предназначенных для создания цифровых компараторов. Из этих версий только последние три целесообразно использовать в новых проектах, остальные являются устаревшими. Наиболее широким спектром возможностей обладает параметризированный модуль Comparator версии v9_0, который позволяет формировать компараторы с различной конфигурацией входных и выходных сигналов для последующей оптимальной реализации в ПЛИС следующих семейств: Spartan–II; SpartanIIE; Spartan–3; Spartan–3E; Virtex; Virtex–E; Virtex–II; Virtex–II PRO; Virtex–II PRO X; Virtex–4; Virtex–5.

Данный модуль относится одновременно к двум категориям ядер: к группе базовых элементов цифровых устройств Basic Elements и к группе ядер, предназначенных для реализации математических функций Math Functions.

Отличительными особенностями рассматриваемого модуля являются:

- выполнение операций сравнения значений двух цифровых сигналов, поступающих во входные порты A и B, и формирование активного уровня выходного сигнала, который соответствует одному из возможных соотношений входных данных (A=B, A<>B, A<=B, A < B, A>=B или A>B), который определяется пользователем;

- возможность выбора разрядности входных портов (операндов) (от 1 до 256 разрядов);

- поддержка операций сравнения цифровых данных, представленных в виде кода со знаком и без него;

- возможность создания компараторов, реализующих операции сравнения значения входного цифрового сигнала с константой, значение которой определяется пользователем при генерации ядра;

- возможность генерации компараторов с комбинационным (обычным) и/или регистровым (триггерным) выходом;

- наличие синхронных и асинхронных входов сброса и/или установки, а также входа разрешения синхронизации в выходном регистре (триггере) по выбору пользователя;

- возможность реализации конвейерной организации выполнения операций.

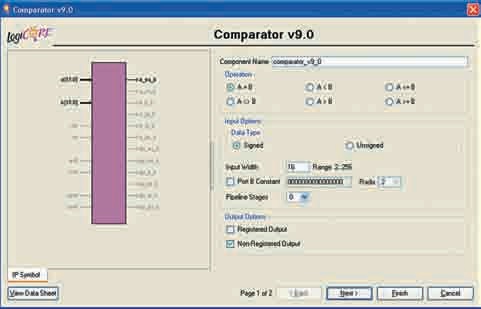

Формирование требуемой разновидности

компаратора на основе рассматриваемого параметризированного модуля осуществляется

с помощью соответствующего мастера

настройки параметров, включающего в себя две

диалоговые панели, вид которых показан на

рис. 1, 2. Стартовая диалоговая панель предназначена для определения типа выполняемой операции, а также параметров входных

и выходных портов генерируемого компаратора. В этой же диалоговой панели в поле редактирования Component Name указывается

название формируемого вида компаратора.

Тип операции, выполняемой компаратором,

задается в виде соотношения значений входных сигналов, которому соответствует активный уровень выходного сигнала. Выбор выходной функции осуществляется с помощью

группы кнопок с зависимой фиксацией A=B, A<>B, A<=B, A < B, A>=B или A>B, которые

расположены во встроенной панели Operation (рис. 1)

Рисунок 1 — Стартовая диалоговая панель «мастера» настройки параметров ядра цифрового компаратора

Система представления входных данных

указывается с помощью двух кнопок с зависимой фиксацией, находящихся во встроенной панели

Data Type (рис. 1). Если в нажатом состоянии зафиксирована кнопка Signed,

то значения входных сигналов интерпретируются как операнды со знаком. При нажатой кнопке Unsigned

входные данные воспринимаются как операнды без знака. Разрядность входных портов A и B определяется

с помощью поля редактирования Input Width.

Требуемое число разрядов портов (в диапазоне от 1 до 256 для значений без знака и от

2 до 256 для значений со знаком) указывается с помощью клавиатуры, после активизации данного поля редактирования.

Если необходимо сформировать компаратор, выполняющий сравнение значений входного

сигнала с константой, то следует перевести

в состояние включено

индикатор Port B Constant.

После этого станут доступными поле редактирования значения константы и поле выбора основания системы счисления Radix.

Прежде всего нужно выбрать основание системы счисления, в которой будет представлено значение константы. Выпадающий

список значений параметра Radix содержит

три возможных варианта: 2, 10, 16. Таким образом, значение константы может быть задано в двоичном, десятичном и

шестнадцатеричном представлении. По умолчанию установлена двоичная система счисления. Затем

следует активизировать поле редактирования

значения константы и с помощью клавиатуры ввести требуемую последовательность цифровых символов, соответствующих выбранной системе счисления.

Количество ступеней

конвейера указывается с помощью поля выбора Pipeline Stages. Допустимое значение этого

параметра зависит от разрядности входных портов и вида сигнала, подаваемого на

входы порта B (сигнал с изменяющимися значениями или константа). Максимальное число ступеней конвейера может достигать четырех, если разрядность входных портов

больше 128. Нулевое значение параметра Pipeline Stages, установленное по умолчанию, указывает на отсутствие конвейерной

организации в формируемом компараторе.

Тип выходных портов генерируемого компаратора указывается с помощью двух индикаторов состояния,

расположенных во встроенной панели Output Options. Включенное состояние индикатора Non-Registered Output,

установленное по умолчанию, соответствует компаратору с комбинационным (обычным) выходом. Для включения

в состав формируемого компаратора выходного регистра (триггера) нужно перевести индикатор

Registered Output в состояние включено

.

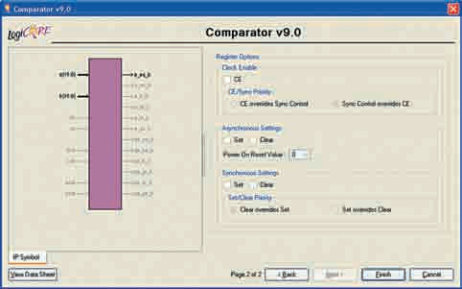

Вторая (заключительная) диалоговая панель мастера

настройки параметров ядра

цифрового компаратора позволяет выбрать

тип сигналов управления выходного регистра (триггера) компаратора (рис. 2). Если

для формируемого компаратора не была выбрана опция создания регистрового выхода

(установки выходного регистра (триггера)),

то все элементы управления, предназначенные для определения соответствующих значений указанных параметров, находятся в недоступном состоянии.

Чтобы включить в состав компаратора выходной триггер с входом разрешения синхронизации, следует воспользоваться индикатором состояния и кнопками, находящимися

во встроенной панели Clock Enable (рис. 2).

Для формирования входа разрешения синхронизации нужно установить индикатор CE

в состояние включено

. При наличии в выходном триггере цепей синхронного сброса

и/или установки необходимо определить

приоритеты сигналов разрешения синхронизации и сброса/установки с помощью группы кнопок с зависимой фиксацией CE/Sync

Priority. Чтобы сигнал на входе разрешения

синхронизации имел более высокий приоритет по сравнению с сигналами на входах синхронного сброса/установки, следует зафиксировать в нажатом состоянии кнопку CE

overrides Sync Control. Для установки обратного соотношения приоритетов нужно перевести в нажатое состояние кнопку Sync Control

overrides CE.

Если в выходном триггере формируемого компаратора требуются входы асинхронного сброса и/или установки, то следует установить в состояние «включено» индикаторы Clear и/или SET соответственно, которые расположены во встроенной панели Asynchronous Settings (рис. 2). При этом поле выбора Power On Reset Value, находящееся в этой же встроенной панели, позволяет определить состояние, в котором выходной триггер будет находиться сразу после подачи напряжения питания.

Рисунок 2 — Заключительная диалоговая панель «мастера» настройки параметров ядра цифрового компаратора

Для генерации выходного триггера с цепями синхронного сброса и/или установки нужно использовать индикаторы состояния Clear и/или SET соответственно, которые находятся во встроенной панели Synchronous Settings (рис. 2). Приоритеты сигналов синхронного сброса и установки задаются с помощью группы кнопок с зависимой фиксацией SET/Clear Priority. Если в нажатом состоянии зафиксирована кнопка Clear overrides SET, то сигнал на входе синхронного сброса будет иметь более высокий приоритет, чем на входе синхронной установки. При нажатии кнопки SET overrides Clear более высокий приоритет будет иметь сигнал на входе синхронной установки.

В рассматриваемом параметризированном модуле используется следующая система условных обозначений входных и выходных портов:

- a [N:0] и b [N:0] — входы сравниваемых операндов с разрядностью N+1;

- clk — вход сигнала синхронизации;

- ce — вход сигнала разрешения синхронизации;

- aclr — вход сигнала асинхронного сброса;

- sclr — вход сигнала синхронного сброса;

- aset — вход сигнала асинхронной установки;

- sset — вход сигнала синхронной установки;

- a_eq_b — выход сигнала эквивалентности значений входных операндов;

- qa_eq_b — регистровый выход сигнала эквивалентности входных значений;

- a_ne_b — выход сигнала неравенства входных значений;

- qa_ne_b — регистровый выход сигнала неравенства входных значений;

- a_lt_b — выход сигнала a

- qa_lt_b — регистровый выход сигнала a

- a_gt_b — выход сигнала a>b;

- qa_gt_b — регистровый выход сигнала a>b;

- a_le_b — выход сигнала a<=b;

- qa_le_b — регистровый выход сигнала a<=b;

- a_ge_b — выход сигнала a>=b;

- a_ge_b — регистровый выход сигнала a>=b.

- qa_lt_b — регистровый выход сигнала a

Из всех перечисленных идентификаторов в описании интерфейса сгенерированного компаратора (и, соответственно, в условном графическом образе данного компонента) будут представлены условные обозначения только тех входных и выходных портов, которые были указаны пользователем при определении его параметров. В качестве примера далее приводится описание шестнадцатиразрядного компаратора с комбинационным и регистровым выходом, входами разрешения синхронизации, синхронного и асинхронного сброса, синхронной и асинхронной установки, который сгенерирован с помощью параметризированного модуля Сomparator версии v9_0

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- synopsys translate_off

Library XilinxCoreLib;

-- synopsys translate_on

ENTITY comparator_v9_0 IS

port (

a: IN std_logic_VECTOR(15 downto 0);

b: IN std_logic_VECTOR(15 downto 0);

clk: IN std_logic;

ce: IN std_logic;

aclr: IN std_logic;

aset: IN std_logic;

sclr: IN std_logic;

sset: IN std_logic;

a_eq_b: OUT std_logic;

qa_eq_b: OUT std_logic

);

END comparator_v9_0;

ARCHITECTURE comparator_v9_0_a OF comparator_v9_0 IS

-- synopsys translate_off

component wrapped_comparator_v9_0

port (

a: IN std_logic_VECTOR(15 downto 0);

b: IN std_logic_VECTOR(15 downto 0);

clk: IN std_logic;

ce: IN std_logic;

aclr: IN std_logic;

aset: IN std_logic;

sclr: IN std_logic;

sset: IN std_logic;

a_eq_b: OUT std_logic;

qa_eq_b: OUT std_logic

);

end component;

-- Configuration specification

for all : wrapped_comparator_v9_0 use entity XilinxCoreLib.c_compare_v9_0(behavioral)

generic map(

c_has_qa_ge_b => 0,

c_has_aset => 1,

c_has_qa_lt_b => 0,

c_has_qa_ne_b => 0,

c_has_a_gt_b => 0,

c_has_a_eq_b => 1,

c_data_type => 0,

c_sync_priority => 1,

c_has_sclr => 1,

c_has_qa_gt_b => 0,

c_width => 16,

c_has_qa_eq_b => 1,

c_enable_rlocs => 0,

c_infered_rtl_const_compare => 0,

c_carry_chain_eq_ne => 0,

c_has_a_le_b => 0,

c_ainit_val => «0»,

c_dense_lut_packing => 0,

c_has_ce => 1,

c_pipe_stages => 0,

c_has_aclr => 1,

c_sync_enable => 1,

c_has_sset => 1,

c_has_qa_le_b => 0,

c_b_constant => 0,

c_has_a_ge_b => 0,

c_has_a_ne_b => 0,

c_has_a_lt_b => 0,

c_b_value => «0000000000000000»

);

-- synopsys translate_on

BEGIN

-- synopsys translate_off

U0 : wrapped_comparator_v9_0

port map (

a => a,

b => b,

clk => clk,

ce => ce,

aclr => aclr,

aset => aset,

sclr => sclr,

sset => sset,

a_eq_b => a_eq_b,

qa_eq_b => qa_eq_b

);

-- synopsys translate_on

END comparator_v9_0_a;

Для декларации сформированного компаратора comparator_v9_0 в составе VHDL–описания проектируемого устройства нужно использовать следующую последовательность выражений:

component comparator_v9_0

port (

a: IN std_logic_VECTOR(15 downto 0);

b: IN std_logic_VECTOR(15 downto 0);

clk: IN std_logic;

ce: IN std_logic;

aclr: IN std_logic;

aset: IN std_logic;

sclr: IN std_logic;

sset: IN std_logic;

a_eq_b: OUT std_logic;

qa_eq_b: OUT std_logic

);

end component;

-- FPGA Express Black Box declaration

attribute fpga_dont_touch: string;

attribute fpga_dont_touch of comparator_v9_0: component is «true»;

-- Synplicity black box declaration

attribute syn_black_box : boolean;

attribute syn_black_box of comparator_v9_0: component is true;

Создание экземпляров компаратора comparator_v9_0 выполняется с помощью следующего оператора:

<идентификатор_экземпляра_компаратора> : comparator_v9_0 port map ( a => a, b => b, clk => clk, ce => ce, aclr => aclr, aset => aset, sclr => sclr, sset => sset, a_eq_b => a_eq_b, qa_eq_b => qa_eq_b );

Создание счетчиков с помощью генератора параметризированных модулей CORE Generator

Разработку различных счетчиков, предназначенных для реализации в ПЛИС с архитектурой FPGA, целесообразно осуществлять с помощью параметризированного модуля Binary Counter. К моменту подготовки материала данной статьи рекомендуемой версией этого модуля являлась модификация Binary Counter v8.0. Эта версия позволяет создавать двоичные счетчики с различной разрядностью и разнообразным набором управляющих сигналов, которые оптимальным образом могут быть реализованы в ПЛИС следующих семейств: Spartan-II; Spartan-IIE; Spartan-3; Spartan-3E; Virtex; Virtex-E; Virtex-II; Virtex-II PRO; Virtex-4.

Данная версия параметризированного модуля Binary Counter обладает некоторыми отличительными особенностями. К ним относятся:

- возможность формирования счетчиков с различным направлением счета, включая реверсивные;

- поддержка широкого диапазона разрядности генерируемых счетчиков (от 2 до 30 разрядов);

- возможность создания счетчиков с параллельными входами загрузки;

- наличие синхронных и асинхронных входов сброса и установки, входов инициализации, а также входа разрешения синхронизации, используемых по выбору пользователя;

- возможность выбора шага изменения состояния в формируемых счетчиках;

- наличие дополнительных выходов (синхронного и/или асинхронного), период переключения которых определяется пользователем;

- возможность установки предельного значения счета по выбору разработчика.

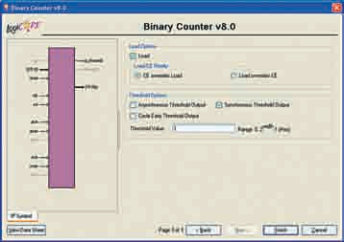

Мастер

настройки параметров рассматриваемого модуля включает в себя три диалоговые панели. Стартовая диалоговая панель,

вид которой представлен на рис. 3, используется для определения основных параметров

генерируемого счетчика.

Идентификатор создаваемого вида счетчика указывается в поле редактирования Component Name. Для определения разрядности генерируемого счетчика предназначено поле редактирования Output Width, которое находится во встроенной панели Width Options (рис. 3). По умолчанию для данного параметра предлагается значение 16. Значение шага изменения состояния создаваемого счетчика (инкремента или декремента) задается в поле редактирования Step Value, расположенном во встроенной панели Count Restrictions. Допустимые значения этого параметра находятся в диапазоне от 1 до 2width – 1, где width — выбранная разрядность счетчика. В качестве значения, установленного по умолчанию, в поле редактирования Step Value отображается единица. Следует обратить внимание на то, что значение шага изменения состояния счетчика указывается в шестнадцатеричном формате. Для определения предельного значения счета следует установить индикатор Restrict Count, находящийся во встроенной панели Count Restrictions, в состояние «включено». После этого становится доступным поле редактирования параметра Final Count Value, расположенное в этой же встроенной панели. Требуемое значение данного параметра (в диапазоне от 0 до 2width– 2) в шестнадцатеричном представлении указывается с помощью клавиатуры в этом поле редактирования. Тип генерируемого счетчика (в соответствии с направлением счета) определяется с помощью группы кнопок с зависимой фиксацией Count Mode (рис. 3). Для создания счетчика, функционирующего в инкрементном режиме, в нажатом состоянии должна быть зафиксирована кнопка UP. Если необходимо сформировать счетчик, работающий в декрементном режиме, следует переключить в нажатое состояние кнопку DOWN. Генерация реверсивных счетчиков производится при нажатой кнопке UP/DOWN.

Рисунок 3 — Стартовая диалоговая панель мастера

настройки параметров ядра счетчика

Вторая диалоговая панель мастера

настройки параметров ядра счетчика, вид которой приведен на рис. 4, позволяет указать

требуемые входы управления.

Рисунок 4 — Вторая диалоговая панель «мастера» настройки параметров ядра счетчика

Для формирования счетчиков с асинхронным сбросом и/или установкой нужно воспользоваться индикаторами состояния, которые расположены во встроенной панели Asynchronous Settings (рис. 4). Чтобы включить в состав генерируемого счетчика входы асинхронного сброса и/или установки, нужно перевести в состояние «включено» индикаторы Clear и/или SET соответственно. В том случае, если входы асинхронного сброса и установки не будут задействованы (индикаторы Clear и SET находятся в сброшенном состоянии), можно использовать вход асинхронной инициализации. При подаче активного уровня сигнала на данный вход, счетчик устанавливается в заранее определенное состояние. Для активизации входной цепи инициализации в формируемом счетчике следует переключить в состояние «включено» индикатор Init, находящийся во встроенной панели Asynchronous Settings. После этого становится доступным поле редактирования Asynchronous Init Value, находящееся в этой же встроенной панели. Состояние счетчика в режиме инициализации указывается в этом поле в виде шестнадцатеричного значения, которое должно находиться в пределах диапазона от 0 до 2width– 1. По умолчанию в поле редактирования Asynchronous Init Value предлагается нулевое значение

Включение в состав генерируемых счетчиков входных цепей синхронного сброса и/или синхронной установки осуществляется с помощью индикаторов состояния Clear и/или SET соответственно, которые находятся во встроенной панели Synchronous Settings (рис. 4). При отсутствии данных входов (индикаторы Clear и SET находятся в состоянии «выключено») можно задействовать вход синхронной инициализации. Для этого нужно использовать индикатор состояния Init и поле редактирования Synchronous Init Value, которые расположены во встроенной панели Synchronous Settings.

Если в генерируемом счетчике одновременно присутствуют входы синхронного сброса и установки, то необходимо установить приоритеты сигналов, подаваемых на эти входы. Для этого следует воспользоваться группой кнопок с зависимой фиксацией SET/Clear Priority (рис. 4). Чтобы сигнал на входе синхронного сброса имел более высокий приоритет, чем сигнал на входе синхронной установки, следует зафиксировать в нажатом состоянии кнопку Clear overrides SET. При переключении в нажатое состояние кнопки SET overrides Clear более высокий приоритет будет иметь сигнал на входе синхронной установки.

Для создания счетчиков с входом разрешения синхронизации (счета) следует воспользоваться индикатором состояния и кнопками, которые находятся во встроенной панели Clock Enable (рис. 4). Чтобы в формируемом счетчике присутствовал вход разрешения синхронизации (счета), необходимо установить индикатор CE в состояние «включено». При наличии в создаваемом счетчике входов синхронного сброса и/или установки необходимо определить приоритеты сигналов разрешения синхронизации и сброса/установки с помощью группы кнопок с зависимой фиксацией Sync/CE Priority. Чтобы сигнал на входе разрешения синхронизации имел более высокий приоритет по сравнению с сигналами синхронного сброса/установки, нужно зафиксировать в нажатом состоянии кнопку CE overrides Sync Control. Установка обратного соотношения приоритетов выполняется при переключении в нажатое состояние кнопки Sync Control overrides CE.

Заключительная диалоговая панель «мастера» настройки параметров ядра счетчика предназначена для указания дополнительных возможностей генерируемого счетчика. Вид этой панели приведен на рис. 5.

Рисунок 5 — Заключительная диалоговая панель «мастера» настройки параметров ядра счетчика

Для генерации счетчиков с возможностью параллельной загрузки данных нужно установить индикатор LOAD, расположенный во встроенной панели LOAD Options, в состояние «включено». При этом в состав формируемого описания счетчика добавляется входной порт параллельной загрузки, количество разрядов которого соответствует разрядности счетчика, а также вход управления записью данных. Группа кнопок с зависимой фиксацией LOAD/CE Priority позволяет определить приоритеты сигналов управления параллельной загрузкой и разрешения синхронизации. Если в нажатом состоянии зафиксирована кнопка CE overrides LOAD, то сигнал разрешения синхронизации будет иметь более высокий приоритет, чем сигнал управления параллельной загрузкой. При нажатой кнопке LOAD overrides CE более высоким приоритетом будет обладать сигнал разрешения параллельной записи данных в счетчик.

Чтобы сформировать счетчики с дополнительными выходами, на которых период переключения сигнала определяется разработчиком, нужно воспользоваться индикаторами состояния и полем редактирования, которые находятся во встроенной панели Threshold Options (рис. 5). Для создания счетчиков с синхронным дополнительным (пользовательским) выходом следует установить в состояние «включено» индикатор Synchronous Threshold Output. При установке в активное состояние индикатора Asynchronous Threshold Output генерируемый счетчик будет иметь асинхронный дополнительный выход. Если хотя бы один из указанных индикаторов переводится в состояние «включено», становится доступным поле редактирования Threshold Value. Это поле предназначено для определения состояния счетчика, при котором происходит переключение сигнала на дополнительном (пользовательском) выходе. Указываемое значение должно быть представлено в шестнадцатеричном формате и находится в пределах интервала от 0 до 2width– 1. С помощью индикатора состояния Cycle Early Threshold Output (рис. 5) можно установить режим переключения сигнала на пользовательском выходе формируемого счетчика с опережением на один период тактового сигнала. Для этого необходимо перевести указанный индикатор в состояние «включено».

Система условных обозначений входных и выходных портов параметризированного модуля Binary Counter v8.0 включает в себя следующие идентификаторы:

- clk — вход тактового сигнала;

- ce — вход сигнала разрешения счета;

- aclr — вход сигнала асинхронного сброса;

- aclr — вход сигнала асинхронного сброса;

- aset — вход сигнала асинхронной установки;

- sset — вход сигнала синхронной установки;

- ainit — вход сигнала асинхронной инициализации;

- sinit — вход сигнала синхронной инициализации;

- up — вход сигнала, определяющего направление счета для реверсивных счетчиков;

- l[N:0] — входы параллельной загрузки данных с разрядностью N+1;

- load — вход разрешения параллельной загрузки данных;

- q[N:0] — выходы счетчика с разрядностью N+1;

- thresh0 — дополнительный (пользовательский) асинхронный выход счетчика;

- q_thresh0 — дополнительный (пользовательский) синхронный выход счетчика.

Описание интерфейса и условный графический образ сформированного счетчика содержат идентификаторы только тех входных и выходных портов, которые были указаны на этапе определения его параметров. Для примера ниже приведено VHDL-описание 24-разрядного счетчика c_counter_binary_v8_0 с асинхронным сбросом и установкой, синхронной инициализацией, входами разрешения синхронизации (счета), параллельной загрузки и пользовательским выходом, сигнал на котором переключается при достижении состояния 00001F.

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- synopsys translate_off

Library XilinxCoreLib;

-- synopsys translate_on

ENTITY c_counter_binary_v8_0 IS

port (

clk: IN std_logic;

up: IN std_logic;

ce: IN std_logic;

load: IN std_logic;

l: IN std_logic_VECTOR(23 downto 0);

aclr: IN std_logic;

aset: IN std_logic;

sinit: IN std_logic;

thresh0: OUT std_logic;

q: OUT std_logic_VECTOR(23 downto 0)

);

END c_counter_binary_v8_0;

ARCHITECTURE c_counter_binary_v8_0_a OF c_counter_binary_v8_0 IS

-- synopsys translate_off

component wrapped_c_counter_binary_v8_0

port (

clk: IN std_logic;

up: IN std_logic;

ce: IN std_logic;

load: IN std_logic;

l: IN std_logic_VECTOR(23 downto 0);

aclr: IN std_logic;

aset: IN std_logic;

sinit: IN std_logic;

thresh0: OUT std_logic;

q: OUT std_logic_VECTOR(23 downto 0)

);

end component;

-- Configuration specification

for all : wrapped_c_counter_binary_v8_0 use entity XilinxCoreLib.

c_counter_binary_v8_0(behavioral)

generic map(

c_count_mode => 2,

c_has_aset => 1,

c_load_enable => 1,

c_load_low => 0,

c_count_to => «1»,

c_sync_priority => 1,

c_has_iv => 0,

c_has_sclr => 0,

c_restrict_count => 0,

c_width => 24,

c_has_q_thresh1 => 0,

c_enable_rlocs => 0,

c_has_q_thresh0 => 0,

c_thresh1_value => «0»,

c_has_load => 1,

c_has_up => 1,

c_thresh_early => 0,

c_has_thresh1 => 0,

c_has_thresh0 => 1,

c_ainit_val => «0»,

c_has_ce => 1,

c_pipe_stages => 0,

c_has_aclr => 1,

c_sync_enable => 0,

c_has_ainit => 0,

c_sinit_val => «0»,

c_has_sset => 0,

c_has_sinit => 1,

c_count_by => «1»,

c_has_l => 1,

c_thresh0_value => «11111»

);

-- synopsys translate_on

BEGIN

-- synopsys translate_off

U0 : wrapped_c_counter_binary_v8_0

port map (

clk => clk,

up => up,

ce => ce,

load => load,

l => l,

aclr => aclr,

aset => aset,

sinit => sinit,

thresh0 => thresh0,

q => q

);

-- synopsys translate_on

END c_counter_binary_v8_0_a;

Декларация сформированного вида счетчика c_counter_binary_v8_0 в описании разрабатываемого устройства выполняется с помощью следующей последовательности выражений:

component c_counter_binary_v8_0

port (

clk: IN std_logic;

up: IN std_logic;

ce: IN std_logic;

load: IN std_logic;

l: IN std_logic_VECTOR(23 downto 0);

aclr: IN std_logic;

aset: IN std_logic;

sinit: IN std_logic;

thresh0: OUT std_logic;

q: OUT std_logic_VECTOR(23 downto 0)

);

end component;

-- FPGA Express Black Box declaration

attribute fpga_dont_touch: string;

attribute fpga_dont_touch of c_counter_binary_v8_0: component is «true»;

-- Synplicity black box declaration

attribute syn_black_box : boolean;

attribute syn_black_box of c_counter_binary_v8_0: component is true;

Для создания экземпляра сгенерированного вида счетчика c_counter_binary_v8_0 нужно включить в состав описания проектируемого устройства следующий оператор:

<идентификатор_экземпляра_счетчика> : c_counter_binary_v8_0 port map ( clk => clk, up => up, ce => ce, load => load, l => l, aclr => aclr, aset => aset, sinit => sinit, thresh0 => thresh0, q => q );

Формирование дешифраторов с использованием ядра генератора параметризированных модулей CORE Generator

Параметризированный модуль Binary Decoder предназначен для генерации дешифраторов, преобразующих входной двоичный код в активный уровень сигнала на одном из выходов. Актуальной версией данного модуля является модификация Binary Decoder v7.0, которая позволяет создавать дешифраторы с различной разрядностью входного и выходного кода и разнообразным сочетанием управляющих сигналов. Формируемые дешифраторы рассчитаны на оптимальную реализацию в ПЛИС следующих семейств: Spartan-II; Spartan-IIE; Spartan-3; Spartan-3E; Virtex; Virtex-E; Virtex-II; Virtex-II PRO.

Отличительными особенностями данной версии параметризированного модуля Binary Decoder v7.0 являются:

- поддержка широкого диапазона разрядности входного двоичного кода и количества выходов (от 2 до 256);

- возможность выбора активного уровня выходных сигналов;

- наличие синхронных и асинхронных входов сброса и/или установки, входов инициализации, а также входа разрешения синхронизации, использование которых определяется пользователем;

- озможность создания дешифраторов с входом разрешения выходного сигнала;

- возможность формирования выходов различного типа (комбинационного и/или регистрового);

- возможность генерации дешифраторов в виде макросов с относительным размещением Relationally Placed Macro (RPM).

Мастер

настройки параметров рассматриваемого ядра содержит одну основную диалоговую панель и одну вспомогательную.

Основная диалоговая панель, вид которой

приведен на рис. 6, предназначена для определения ключевых параметров генерируемого дешифратора.

Рисунок 6 — Основная диалоговая панель «мастера» настройки параметров ядра двоичного дешифратора (страница Parameters)

Название формируемого вида двоичного дешифратора указывается в поле редактирования Component Name. Значение параметра Number of Outputs определяет количество выходов генерируемого дешифратора. При этом количество информационных входов (разрядность входного двоичного кода) вычисляется автоматически в соответствии с формулой N = Log2M, где M — число выходов дешифратора. Если результат вычислений не является целым числом, то он округляется в большую сторону до ближайшего целого значения. Требуемое количество выходов дешифратора в интервале от 2 до 256 указывается с помощью клавиатуры в поле редактирования Number of Outputs (рис. 6). Значение этого параметра, предлагаемое по умолчанию, равно восьми.

Для генерации дешифраторов с функцией разрешения выходных сигналов необходимо установить индикатор Decoder Enable (рис. 6) в состояние «включено». При этом формируемый дешифратор будет содержать дополнительный вход разрешения выходных сигналов. Если на этом входе отсутствует разрешающий уровень сигнала, то все выходы дешифратора находятся в неактивном состоянии.

Выбор типа выходов в создаваемом дешифраторе осуществляется с помощью группы кнопок с зависимой фиксацией Output Options (рис. 6). Когда в нажатом состоянии зафиксирована кнопка Non Registered, генерируемый дешифратор будет иметь только обычные (комбинационные) выходы. Для включения в состав дешифратора выходного регистра (выходных триггеров) нужно переключить в нажатое состояние кнопку Registered. Чтобы сформировать дешифратор с обычными и регистровыми выходами, следует нажать кнопку Both. Если выбрана опция использования выходных регистров, то становится доступной клавиша Register Options, которая позволяет открыть вспомогательную диалоговую панель «мастера» настройки параметров ядра двоичного дешифратора.

Активный уровень сигналов на выходах дешифратора выбирается с помощью группы кнопок с зависимой фиксацией Output Sense. По умолчанию в качестве активного установлен высокий логический уровень сигнала (в нажатом состоянии зафиксирована кнопка Active High). Для генерации дешифраторов с активным низким уровнем сигнала на выходах следует установить в нажатое состояние кнопку Active Low

Параметр Create RPM позволяет выбрать форму представления создаваемого дешифратора. Чтобы сгенерировать дешифратор в виде макроса с относительным размещением, нужно установить одноименный индикатор (рис. 6) в состояние «включено».

Вспомогательная диалоговая панель «мастера» настройки параметров ядра двоичного дешифратора используется для выбора параметров выходного регистра (выходных триггеров). Вид этой панели показан на рис. 7.

Рисунок 7 – Вспомогательная диалоговая панель «мастера» настройки параметров ядра двоичного дешифратора

Чтобы выходной регистр формируемого дешифратора содержал вход разрешения синхронизации, следует воспользоваться индикатором состояния и кнопками, находящимися во встроенной панели Clock Enable (рис. 7). Для применения входа разрешения синхронизации необходимо установить одноименный индикатор в состояние «включено». Если в выходном регистре задействованы входы синхронного сброса и/или установки, то следует определить приоритеты сигналов разрешения синхронизации и сброса/установки с помощью группы кнопок с зависимой фиксацией CE Overrides. Чтобы сигнал на входе разрешения синхронизации имел более высокий приоритет по сравнению с сигналами на входах синхронного сброса/установки, следует зафиксировать в нажатом состоянии кнопку CE overrides Sync Control. Для установки обратного соотношения приоритетов сигналов необходимо нажать кнопку Sync Controls override CE.

Для использования в выходном регистре формируемого дешифратора режимов (и входов) асинхронного сброса и/или установки или инициализации следует воспользоваться кнопками с зависимой фиксацией и полем редактирования, которые расположены во встроенной панели Asynchronous Settings (рис. 7). Чтобы добавить вход асинхронной установки или сброса, нужно зафиксировать в нажатом состоянии кнопку SET или Clear соответственно. Если в выходном регистре должны использоваться режимы и асинхронного сброса, и асинхронной установки, нужно нажать кнопку Set and Clear. При отсутствии входов асинхронного сброса и асинхронной установки можно использовать вход асинхронной инициализации. Для этого нужно нажать кнопку Init, после чего становится доступным поле редактирования Asynchronous Init Value. В этом поле указывается шестнадцатеричное значение, соответствующее состоянию выходов дешифратора в режиме асинхронной инициализации. Если выходной регистр не должен содержать никаких управляющих входов, следует оставить в нажатом состоянии кнопку None, в котором она находится по умолчанию.

Для генерации выходного регистра дешифратора с входами синхронного сброса и/или установки или инициализации нужно использовать аналогичные кнопки с зависимой фиксацией, которые находятся во встроенной панели Synchronous Settings (рис. 7). Состояние выходов дешифратора в режиме синхронной инициализации указывается в поле редактирования Synchronous Init Value в виде шестнадцатеричного значения. Если в формируемом дешифраторе будут одновременно присутствовать входы синхронного сброса и установки, то нужно с помощью группы кнопок с зависимой фиксацией SET/Clear Priority определить приоритеты соответствующих сигналов. Для установки более высокого приоритета сигнала на входе синхронного сброса по сравнению с сигналом на входе синхронной установки следует зафиксировать в нажатом состоянии кнопку Clear overrides SET. При нажатии кнопки SET overrides Clear более высокий приоритет будет иметь сигнал на входе синхронной установки.

В рассматриваемом параметризированном модуле двоичного дешифратора Binary Decoder v7.0 используется следующая система условных обозначений интерфейсных портов:

- S[N:0] — информационные входы дешифратора;

- EN — вход разрешения выходных сигналов;

- CLK — вход тактового сигнала;

- CE — вход сигнала разрешения синхронизации;

- ACLR — вход сигнала асинхронного сброса;

- ASET — вход сигнала асинхронной установки;

- SCLR — вход сигнала синхронного сброса;

- SSET — вход сигнала синхронной установки;

- AINIT — вход сигнала асинхронной инициализации;

- SINIT — вход сигнала синхронной инициализации;

- O[M:0] — комбинационные выходы дешифратора;

- Q[M:0] — регистровые выходы дешифратора.

В составе описания интерфейса сформированного дешифратора и, соответственно, в его условном графическом образе будут присутствовать идентификаторы только тех входных и выходных портов, которые были указаны пользователем при определении его параметров. Использование параметризированного модуля Binary Decoder v7.0 иллюстрирует пример генерации дешифратора из 5 в 32 с функцией разрешения выходных сигналов, входом разрешения синхронизации, асинхронным сбросом и синхронной установкой, комбинационными и регистровыми выходами. VHDL-описание созданного дешифратора decode5_32e имеет следующий вид:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- synopsys translate_off

Library XilinxCoreLib;

-- synopsys translate_on

ENTITY decode5_32e IS

port (

S: IN std_logic_VECTOR(4 downto 0);

O: OUT std_logic_VECTOR(31 downto 0);

EN: IN std_logic;

Q: OUT std_logic_VECTOR(31 downto 0);

CLK: IN std_logic;

CE: IN std_logic;

ACLR: IN std_logic;

SSET: IN std_logic

);

END decode5_32e;

ARCHITECTURE decode5_32e_a OF decode5_32e IS

-- synopsys translate_off

component wrapped_decode5_32e

port (

S: IN std_logic_VECTOR(4 downto 0);

O: OUT std_logic_VECTOR(31 downto 0);

EN: IN std_logic;

Q: OUT std_logic_VECTOR(31 downto 0);

CLK: IN std_logic;

CE: IN std_logic;

ACLR: IN std_logic;

SSET: IN std_logic

);

end component;

-- Configuration specification

for all : wrapped_decode5_32e use entity XilinxCoreLib.C_DECODE_BINARY_V7_0(behavioral)

generic map(

c_out_width => 32,

c_has_aset => 0,

c_has_en => 1,

c_sync_priority => 1,

c_has_sclr => 0,

c_out_high => 1,

c_height => 0,

c_enable_rlocs => 0,

c_sel_width => 5,

c_ainit_val => «00000000000000000000000000000000»,

c_has_ce => 1,

c_pipe_stages => 0,

c_has_aclr => 1,

c_sync_enable => 1,

c_has_ainit => 0,

c_sinit_val => «0»,

c_has_sset => 1,

c_has_sinit => 0,

c_has_q => 1,

c_has_o => 1

);

-- synopsys translate_on

BEGIN

-- synopsys translate_off

U0 : wrapped_decode5_32e

port map (

S => S,

O => O,

EN => EN,

Q => Q,

CLK => CLK,

CE => CE,

ACLR => ACLR,

SSET => SSET);

-- synopsys translate_on

END decode5_32e_a;

Выражения декларации дешифратора decode5_32e в составе описания разрабатываемого устройства выглядят следующим образом:

component decode5_32e

port (

S: IN std_logic_VECTOR(4 downto 0);

O: OUT std_logic_VECTOR(31 downto 0);

EN: IN std_logic;

Q: OUT std_logic_VECTOR(31 downto 0);

CLK: IN std_logic;

CE: IN std_logic;

ACLR: IN std_logic;

SSET: IN std_logic

);

end component;

-- FPGA Express Black Box declaration

attribute fpga_dont_touch: string;

attribute fpga_dont_touch of decode5_32e: component is «true»;

-- Synplicity black box declaration

attribute syn_black_box : boolean;

attribute syn_black_box of decode5_32e: component is true;

Для создания экземпляра дешифратора decode5_32e нужно использовать следующий оператор:

<идентификатор_экземпляра_дешифратора> : decode5_32e port map ( S => S, O => O, EN => EN, Q => Q, CLK => CLK, CE => CE, ACLR => ACLR, SSET => SSET );

Продолжение следует.

Литература

1. Кузелин М. О., Кнышев Д. А., Зотов В. Ю.

Современные семейства ПЛИС фирмы Xilinx.

Справочное пособие. М.: Горячая линия-Телеком. 2004

2. Зотов В. Проектирование цифровых устройств,

реализуемых на базе ПЛИС FPGA фирмы Xilinx,

с использованием средств CORE Generator //

Компоненты и технологии. 2006. № 12. 2007. № 1.

3. Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx. М.: Горячая линия-Телеком. 2006.

4. Зотов В. Ю. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР

WebPack ISE. М.: Горячая линия-Телеком. 2003.