## В.Ф.Гузик, А.О.Пьявченко, Е.С.Синютин, Д.А.Беспалов, В.В.Пустовалов

# УЧЕБНО-ЛАБОРАТОРНЫЙ СТЕНД ДЛЯ РАЗРАБОТКИ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ С ПРИМЕНЕНИЕМ ПЛИС-ТЕХНОЛОГИИ

В статье рассматриваются результаты выполненной на кафедре ВТ силами авторов инициативной разработки эскизного проекта учебно-лабораторного стенда (УЛС), предназначенного для создания на его основе микропроцессорной и/или микроконтроллерной системы универсального или специального назначения с возможностью объединения в сетевые конфигурации.

Актуальность разработки

Актуальность и необходимость разработки такого проекта, на взгляд авторов статьи, состоит в том, что современный инженер, специалист в области эксплуатации и разработки компонентов и узлов компьютерной техники, должен:

- владеть практическими навыками работы с современными САПР, успешно применяя их в реальных схемотехнических проектах;

- уметь проектировать малые мобильные цифровые устройства, имеющие микроконтроллерное управление, поддерживающие различного рода периферийные интерфейсы, реализуемые в базисе ПЛИС;

- уметь решать задачи отладки и тестирования спроектированного устройства, задачи разработки и отладки необходимого программного обеспечения, задачи организации функционального взаимодействия устройства со стандартным компьютерным оборудованием.

В реализуемом проекте отразилась идея разработки лабораторного базиса, увязывающего цели и задачи учебных дисциплин схемотехнического цикла кафедры, позволяющего студенту проявить в наиболее полной мере свои собственные знания и приобрести комплексные практические навыки на различных стадиях разработки и создания функционально законченного устройства цифровой вычислительной техники: от разработки электрических схем, их временного и логического моделирования средствами САПР до практического применения в "железе" результатов разработки с учетом этапов отладки, программирования и первоначальной эксплуатации.

Структурная организация стенда

УЛС представляет собой совокупность аппаратных и программных средств в сопровождении примеров кодов программ и конфигураций, а также документации по их применению.

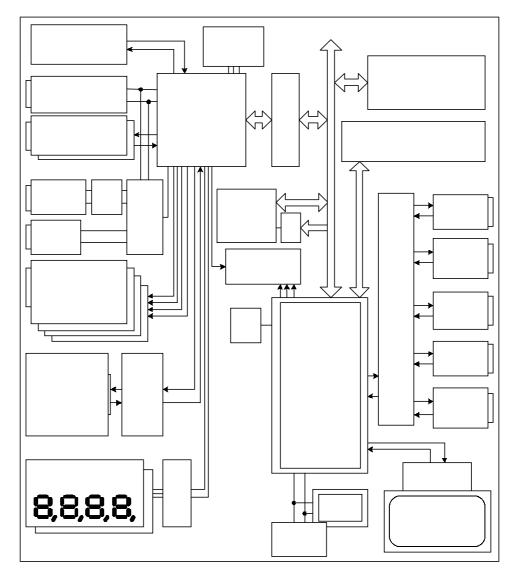

Структурная схема стенда представлена на рис. 1. Как видно из данной структурной схемы, основными элементами стенда являются микроконтроллер и FPGA-модуль.

Рис. 1

Микроконтроллер выполняет функции управляющего и базового вычислительного ядра стенда. FPGA-модуль представляет собою многократно программируемую интегральную схему сверхбольшой интеграции, имеющей от 10 тыс. до 100 тыс. вентилей на кристалле, в зависимости от установленной версии. На основе ресурсов модуля пользователь получает возможность разрабатывать и отлаживать схемотехнические проекты различных цифровых блоков вычислительной техники, в том числе, проекты интерфейсных узлов для организации сопряжения микроконтроллера стенда с такими устройствами, как внешний персональный компьютер, принтер, ЖКИ-модуль, электронный Flash-диск, устройство мобильной связи, модем и др.

В качестве базовой модели микроконтроллера была выбрана модель ATMega128L семейства AVR-микроконтроллеров фирмы ATMEL. Этот микроконтроллер относится к классу RISC-микроконтроллеров с Гарвардской архитектурой, является одной из самых

последних и широко применяемых в настоящее время разработок фирмы. Микроконтроллер характеризуется наличием встроенного конвейера: пока выполняется текущая команда, из встроенной памяти программ считывается следующая; наличием аппаратного двухтактного умножителя; выполнением большинства арифметико-логических операций за один такт; наличием широкого набора встроенных стандартизированных интерфейсов; наличием многоканального 10-разрядного аналого-цифрового интерфейса, быстродействие которого достаточно для оцифровки аналоговых сигналов звукового диапазона стандартной телефонной линии; наличием независимых многократно программируемых встроенных модулей FLASH-памяти программ и EEPROM данных, а также встроенного модуля ОЗУ с возможностью расширения объема последнего за счет дополнительно устанавливаемых внешних модулей памяти. Особо следует отметить возможность блокировки в микроконтроллере участка памяти программ с целью защиты его от дальнейшей перезаписи. Данная возможность позволит разработчикам создать, отладить и закрыть от доступа на кристалле AVR-микроконтроллера коды системных и сервисных программ стенда. Последнее, на взгляд авторов, снизит вероятность пиратского тиражирования стенда, повысит надежность и живучесть стенда в целом в условиях интенсивной эксплуатации.

При выборе типа FPGA-модуля основным критерием, которым руководствовались разработчики, является критерий обеспечения оптимального соотношения производительность/стоимость при снижении общего уровня потребляемой мощности. В связи с этим и с учетом вариантов применения были выбраны микросхемы FPGA с исполнением в 208-выводном PQFP-корпусе с питанием 3,3В (или 2,5В). Такой подход позволит в зависимости от финансовых возможностей и функциональных требований заказчика устанавливать на стенде микросхемы семейств FLEX10KA(E), APEX с количеством вентилей от 10 тыс. до 100 тыс. включительно. Указанные типы микросхемы поддерживают JTAG-интерфейс для внутрисхемного контроля, обладают свойством многократной загрузки конфигурационных проектов, что особенно важно в условиях массового применения и длительной эксплуатации.

В качестве конфигурационного ППЗУ предложено использовать микросхему EPC2 производства Altera, объем которой достаточен для хранения конфигурационных проектов под микросхемы FPGA указанного класса. Многократное программирование микросхемы (до 1000 раз) и ее PLCC корпусное исполнение с установкой на плате в PLCC-панель расширяют эксплуатационные свойства стенда.

Для отработки навыков применения различного рода периферийных интерфейсов, изучения принципов их построения в архитектуру стенда были включены часто применяемые в современной технике интерфейсы:

- асинхронные последовательные интерфейсы RS-232, RS-485, RS-422, функционирующие либо в дуплексном, либо в полудуплексном режимах;

- синхронно-асинхронный последовательный интерфейс USART, синхронные последовательные интерфейсы SPI,  ${\rm I}^2{\rm C}$ ;

- интерфейс JTAG (совместимый с IEEE 1149.1);

- параллельные интерфейсы 8-разрядный Centronics в режимах SPP/EPP/ECP, а также, 16-битный IDE;

- параллельный многофункциональный программно-настраиваемый интерфейс для подключения модуля расширения памяти, NAND FLASH-памяти, в частности;

- интерфейс внутренней параллельной шины адреса/данных для подключения к ней дополнительных модулей функционального расширения;

- интерфейсы сопряжения с электретным микрофоном для приема речи и с звуковым динамиком мощностью до 2 Вт для ее воспроизведения;

- встроенный клавиатурный интерфейс для организации командного ручного управления стендом со стороны пользователя, ввода им требуемой информации. Интерфейс рассчитан на применение пленочной клавиатурной матрицы, размерностью 5х5 клавиш типа TS-SK10 или ей подобной;

- интерфейс взаимодействия с символьными ЖКИ, а также, в перспективе, с графическими ЖКИ типа EL640.480-AF1(Planar) и его аналогами. На стенде предполагается использование двухстрочного символьного ЖКИ с подсветкой типа EL1602A-NL-FBW-R или ему подобного.

Следует отметить, что часть из указанных интерфейсов аппаратно реализована в самом микроконтроллере — это интерфейсы UART/USART, SPI, I<sup>2</sup>C, а часть — с применением ПЛИС и внешних схем электрического сопряжения (соответствующих драйверов). К последним относятся интерфейсы NAND-памяти, IDE, Centronics, RS232/422/485 и ряд других. Выбор типа интерфейса определяется пользователем посредством загрузки в ПЛИС соответствующего конфигурационного проекта и установкой переключателей на плате стенда. Здесь пользователь получает навыки не только в программном управлении подобными интерфейсами, но и познает основы их схемотехнического проектирования. Интерфейсы SPI, JTAG используются в составе стенда для внутрисхемного программирования встроенной памяти микроконтроллера (Flash, EEPROM памяти, перемычек и битов блокировки), конфигурационной структуры ПЛИС.

При разработке как программных, так и схемотехнических проектов требуется своевременное отображение информации на различного рода индикаторах. При этом в микропроцессорных системах преимущественно используются светодиодные и жидкокристаллические индикаторы. Для отработки алгоритмов управления такими средствами индикации в состав комплекса включены восьмисегментные светодиодные индикаторы, светодиодные линейки с раздельным, поразрядным управлением, двухстрочный символьный ЖКИ со встроенным контроллером. Эти же средства индикации могут быть использованы отладочными и тестовыми программами в процессе начальной загрузки стенда, а также отладки пользователем на ПЛИС какого-либо конфигурационного проекта

Такое разнообразие интерфейсов, а также использование встроенного в микро-контроллер 10-разрядного восьмиканального АЦП с диодными ограничителями на вхо-де, встроенных ШИМ совместно с установленными на плате транзисторными усилителями позволяют, на взгляд авторов, расширить области применения стенда, в частности, позволяют применить его для построения действующей модели локальной микроконтроллерной системы сбора и обработки данных, системы управления малыми динамическими объектами.

Расширить область применения стенда также возможно за счет применения модуля функционального расширения. К такого рода модулю в первую очередь следует отнести модуль расширения сетевого интерфейса, удовлетворяющего спецификациям 2.0A/2.0B фирмы Bosch, модуль цифровой обработки сигналов на основе микропроцессора семейства ADSP218x, модуль сетевого адаптера для организации 10-мегабитного EtherNet и ряд других, разрабатываемых на заказ.

Программная поддержка

Все программное обеспечение проектируемого стенда следует разделить на четыре части: инструментальное, системное, конфигурационное и прикладное ПО.

Инструментальное ПО – это, как правило, покупное либо бесплатно распространяемое ПО, предназначенное для разработки, отладки и эмуляции кодов системного и прикладного ПО стенда, управления внутрисхемным программированием ресурсов стенда, удаленного тестирования его программно-доступных аппаратных средств. Ин-

струментальное ПО устанавливается на инструментальном персональном компьютере (ИПК), в обязательном порядке входящем в состав комплекса.

Системное ПО предназначено для управления режимами работы стенда и обеспечивает его корректное функционирование в минимальной конфигурации. В частности, поддерживаются режимы начальной загрузки, настройки и диагностики состояния программно-доступных аппаратных ресурсов стенда после включения питания, а также режимы обслуживания клавиатуры и управления ЖКИ, режим командного монитора, предоставляющий пользователю необходимый минимальный сервис для командного управления стендом посредством клавиатурного интерфейса или со стороны ИПК.

Конфигурационное ПО представляет собою ранее разработанные либо вновь создаваемые проекты конфигурирования ресурсов установленной ПЛИС, в зависимости от номенклатуры используемых в проекте аппаратных средств стенда, а также заданных режимов функционирования.

Как и системное, конфигурационное ПО является резидентным в стенде, т.е. хранится в специальной микросхеме Flash-памяти. Загрузка ПО в ПЛИС выполняется автоматически после включения питания либо по аппаратному сигналу начальной загрузки, формируемому на плате в результате нажатия пользователем соответствующей кнопки на лицевой панели стенда.

Прикладное ПО — это функциональное ПО, разработанное пользователем и имеющее прикладной характер применения. Этот вид ПО является загружаемым и при выключенном питании не хранится в энергонезависимой памяти стенда. Загрузка в память стенда кодов прикладного ПО производится со стороны и под управлением ИПК, а также под управлением системного загрузчика, резидентного в энергонезависимой памяти AVR-микроконтроллера.

Основными инструментальными программными средствами для разработки, отладки и эмуляции программ микроконтроллера, конфигурационных схемотехнических проектов ПЛИС являются, соответственно, AVR Studio 4.0+ (или 3.56) фирмы ATMEL и MAX Plus 10 фирмы ALTERA. Оба программных пакета характеризуются простотой в обучении и эксплуатации. Так, AVR Studio предоставляет пользователю инструментальную среду разработки программ на языке ассемблера для AVR-микроконтроллеров либо на языке С (IAR C, в частности) создания библиотечных модулей и загрузочных кодов программ и данных; предоставляет возможность отладки программных кодов на встроенном симуляторе микроконтроллера выбранного типа, совмещая процесс отладки с временным моделированием, используя средства визуализации содержимого программно-доступных ресурсов моделируемого микроконтроллера, а также развитый механизм log-файлов и контрольных точек.

В качестве внутрисхемного программатора AVR-микроконтроллера используется программатор PonyProg v.2.05а+ (<a href="http://www.LancOS.com">http://www.LancOS.com</a>). Данный программатор характеризуют простая схемотехническая реализация, подключение к LPT-порту ИПК, наличие средств визуализации загружаемых кодов и результатов программирования, возможность удаленной верификации загруженного кода, поддержка микроконтроллера ATmega128L. Следует отметить, что указанный программатор может быть с успехом заменен на программатор фирмы Argussoft — AS1, подключаемый к внешнему порту ИПК типа СОМ. Стоимость программатора AS1 на порядок выше (от 30 у.е.), чем программатора PonyProg. Тем не менее, применение AS1 остается привлекательным ввиду того, что внутрисхемное программирование ПЛИС предполагается осуществлять посредством интерфейса ВуtеВlaster, который подключается к LPT-порту, а СОМ-порт ИПК остается свободным. Для подключения программатора AS1 к разъему программирования микроконтроллера стенда потребуется небольшой кабельный переходник. Наличие такого переходника предполагается в составе проектируемого технологического 162

обеспечения стенда. Сам же программатор не входит в базовый состав технологической оснастки стенда.

Другой инструментальный пакет – программный пакет MAX+Plus II (v.10+) – обладает мощными возможностями по созданию и эмуляции конфигурационных проектов для ПЛИС, FPGA-модулей в частности. При этом пользователю, как правило, доступны текстовый редактор, позволяющий создавать описания проектируемых модулей на языках проектирования аппаратуры AHDL, VHDL, VerilogHDL; редактор схем, позволяющий выполнять схемотехническое проектирование узлов цифровой техники; редактор символов вновь создаваемых элементов, имеющих текстовое или схемотехническое описание и используемых при иерархическом построении проектов; режимы функционального и временного моделирования проекта; редактор компоновки кристалла ПЛИС, предназначенный для предварительного размещения проектов внутри моделируемого пространства ПЛИС согласно заданным критериям проектирования и требуемому распределению выводов микросхемы. Кроме того, данный САПР обеспечивает многократное внутрисхемное программирование реальной микросхемы ПЛИС, например, посредством интерфейса ByteBlaster с последующим контролем результатов загрузки конфигурации. Возможности пакета по созданию схемотехнических библиотек так называемых мегафункций удовлетворяют требованиям сквозного курсового проектирования в рамках схемотехнического цикла учебного процесса кафедры.

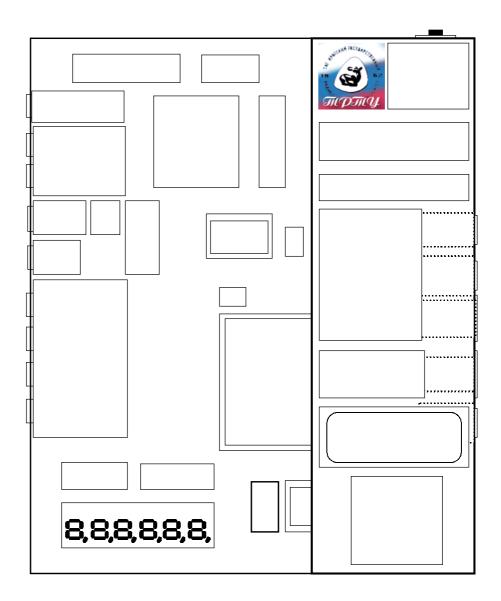

Конструктивное исполнение

Конструктивно стенд предполагается изготавливать в виде пластикового корпуса с прозрачной верхней крышкой. Причем, как смонтированную печатную плату стенда, так и покупной блок сетевого электропитания стенда предполагается разместить внутри его корпуса. На рис. 2 приведен эскиз будущего вида стенда.

Сквозь пластиковую верхнюю крышку можно наблюдать как внутреннее устройство стенда, в частности установленную микросхему ПЛИС, ведущий микроконтроллер, так и осуществлять контроль за состоянием программно-управляемых светодиодных и восьмисегментных индикаторов, установленных на плате. Выведенные на верхнюю правую панель разъемы контрольных точек позволят пользователю при помощи измерительного оборудования контролировать состояние хода проводимых экспериментов. Там же размещены кнопка перевода аппаратуры стенда в исходное состояние и коммутационная режимная панель, выполненная на PLD-линейках.

С целью удобства доступа на верхней панели также размещаются разъемы для подключения дополнительных модулей функционального расширения (модуля сигнального процессора и модуля расширения памяти), двухстрочный символьный ЖКИ-дисплей и пленочная клавиатурная матрица 5х5. Функциональные и технологические интерфейсные разъемы, сетевой выключатель, а также вентиляционные прорези предполагается разместить на боковых и торцевых панелях стенда.

Аналогичные разработки

В настоящее время существует множество аналогов разрабатываемого устройства. Как правило, практически любая фирма, разрабатывающая программно-управляемое аппаратное обеспечение микропроцессорных систем, выпускает помимо основной продукции так называемые стартовые наборы по разработке более сложных систем на ее основе. Однако такие наборы являются узкоспециализированными и имеют достаточно высокую начальную стоимость – от 100 у.е. и выше. Так, например, учебная плата, рекламируемая и производимая фирмой ALTERA, поддерживающая в отличие от проекта несколько разновидностей ПЛИС, тем не менее, проигрывает ему ввиду своей высокой стоимости (порядка 700 у.е.), отсутствия встроенного микроконтроллерного управления, отсутствия требуемого набора функциональных интерфейсов.

Рис. 2

Другими известными аналогами являются учебно-лабораторные стенды SDK-1.1 и SDK 3.0, учебно-лабораторный комплекс A-DEKT совместной разработки фирмы ООО «ЛМТ» (г. Санкт-Петербург) и кафедры вычислительной техники Санкт-Петербургского государственного института точной механики и оптики (технического университета).

Так, согласно фирменному рекламному проспекту, стенд SDK-1.1 построен на базе MCS-51-совместимого микроконтроллера и имеет символьный ЖКИ, клавиатуру, последовательный порт для подключения к ПК. Оснащен 12-разрядными АЦП и ЦАП, дискретными портами ввода/вывода.

Стенд SDK 3.0 построен на базе 16-разрядного коммуникационного микропроцессора  $F^2MC-16LX(Fujitsu)$  с ориентацией на аппаратно-программную поддержку двух-канального CAN-интерфейса, совместимого со спецификацией 2.0.

Учебно-лабораторный комплекс A-DEKT предназначен для освоения методов и средств проектирования систем на базе программируемой логики семейства ACEX фирмы ALTERA (емкость устанавливаемого под заказ кристалла до 100 000 логических вентилей, поддержка значительных объемов памяти — до 16 Мбайт, интерфейсы ввода/вывода).

Дополнительно поставляются различные модули сопряжения с датчиками, релейного управления с гальванической развязкой и ряд других модулей, стоимость самой минимальной конфигурации которых -30 у.е.

Несомненно, проекты в совокупности перекрывают поставленные перед разработчиками стенда задачи. Однако общая суммарная стоимость указанных разработок составляет от 420–450 у.е. и выше. При этом в эту сумму не входит стоимость (от 90 у.е.) программатора, производимого и поставляемого фирмой ООО «ЛМТ». Кроме того, остается под вопросом возможность совместного использования стендов, тип устанавливаемой ПЛИС в базисной конфигурации. Вызывает также сомнение применимость стендов в массовом учебном процессе из-за их бескорпусного исполнения ввиду низкой квалификации пользователей.

В заключение, следует отметить, что разработанный проект стенда предполагается реализовать в аппаратуре с последующим использованием его средств в качестве практического базиса для проведения лабораторных работ схемотехнического цикла учебного процесса кафедры, а также для проведения разного рода практических разработок и исследований в следующих областях:

- обработка сигналов (например, программно-аппаратное моделирование цифровых фильтров; прием, оцифровка, упаковка, распаковка и воспроизведение речи; организация взаимодействия с внешним процессором цифровой обработки сигналов и программное управление им);

- разработка средствами САПР цифровых схем разной сложности и реализация проектов в ПЛИС;

- разработка узлов вычислителей разных типов в базисе ПЛИС с учетом функциональных возможностей встроенных AVR-микроконтроллера, средств индикации, клавиатуры и прочей периферии;

- схемотехническое построение программно-управляемых интерфейсов с поддержкой таких процессов промежуточной обработки транзитной информации, как кодирование/декодирование, фильтрация кадров сообщений, распаковка/упаковка данных;

- построение сетей микроконтроллеров на базе нескольких стендов и т.п.

Все выше сказанное указывает на возможность использования спроектированного стенда как один из вариантов обеспечения экспериментально-практической базой студентов специальности 2201 в рамках курсового и дипломного проектирования, а также в рамках магистерской подготовки.

Реконфигурируемость аппаратно-программных ресурсов стенда благодаря наличию FPGA-модуля и многократная программируемость микроконтроллерного ядра, наличие аппаратных драйверов электрического сопряжения стенда с широким набором стандартных современных интерфейсов, наличие встроенного модуля цифровой обработки и воспроизведения речи, расширяемого комплекта дополнительных модулей (интерфейсный CAN-модуль, модуль цифровой обработки сигналов, а в перспективе, и Ethernet-модуль) и сравнительно низкая стоимость начальной конфигурации (от 250 у.е.) выгодно отличают выполненную разработку от существующих аналогов.

### БИБЛИОГРАФИЧЕСКИЙ СПИСОК

- 1. Стешенко В. Б. ПЛИС фирмы «ALTERA»: элементная база, система проектирования и языки описания аппаратуры. М.: Издательский дом «Додэка-XXI», 2002. 576 с.

- 2. *Антонов А. П.* Язык описания цифровых устройств AlteraHDL. Практический курс. М.: ИП "РадиоСофт", 2001. 224 с.

- Стешенко В. Б. ПЛИС фирмы «ALTERA»: проектирование устройств обработки сигналов. ДОДЭКА, 2002. 128 с.

- 4.  $\mathit{Ah}\ \Pi$ . Сопряжение ПК с внешними устройствами.: Пер. с англ. М.: ДМК Пресс , 2001. 320 с.

- 5. Система команд 8-разрядных RISK микроконтроллеров семейств AVR. КТЦ-МК. 111 с.

- 6. 8-bit AVR Microcontroller ATMega 128 with 128K Bytes In-System Programmable Flash. ATMEL Corporation. 123 p.

- 7. AVRStudio User Guide. ATMEL Corporation. 15 p.

#### С.А. Загайчук, Е.О.Ткачук

## МЕТОДОЛОГИЧЕСКИЙ ПОДХОД СИНТЕЗА СИСТЕМ АДАПТИВНОГО УПРАВЛЕНИЯ

В данной работе предлагаются методологические основы синтеза адаптивных систем управления, которые в состоянии были бы принимать решения высокого уровня сложности, т.е. обучаться новым действиям, изменять формы поведения при изменении условий. Основанные на принципе автоматизации выбора оптимальных решений из множества формируемых моделей, обеспечивают свойство самоорганизации за счет различных эвристических алгоритмов, реализующихся на современной вычислительной технике. Такие системы позволяют осуществлять автоматизированный сбор, хранение, логическую обработку информации, принятие решения в неопределенных нестационарных условиях, а также отображение "советов" лицам, принимающим решения.

Дадим краткое описание основных принципов функционирования отдельных блоков и системы.

ОУ – объект управления. Блок расчета эталонных решений и моделей (БРЭ).

Блок хранения эталонных моделей (БХЭМ) представляет собой компьютер, в памяти которого хранится наиболее характерный для функционирования объекта (системы) набор значений параметров. Блок сравнения реальных ситуаций и моделей блока эталонных моделей (БС) сравнивает текущие реальные ситуации, создавшиеся на объекте (в системе), с эталонными моделями по некоторому критерию  $\kappa_i$ = $MP(X\ni_i,Xp)$ , в котором i — номер эталонной модели, MP—мера рассогласования i-й эталонной ситуации и реальной. Вид меры рассогласования зависит от конкретной задачи. Вычисления по всем i - эталонам ведутся одновременно. Выходом блока (БС) является набор  $\kappa_i$ , по которому в блоке принятия решений (БПР) будет произведен выбор оптимальной эталонной модели. Если рассогласование допустимо по условиям нормального функционирования исследуемого процесса, что определяется в блоке оценки степени рассогласования (БОР),