URL: http://cs.donntu.ru/~zinchenk/art/FPGA_HDL.rar

FPGA– И HDL–ТЕХНОЛОГИИ И ПРОЕКТИРОВАНИЕ ДИАГНОСТИЧЕСКОГО ОБЕСПЕЧЕНИЯ НА ИХ ОСНОВЕ

Зинченко Ю., Тарасенко А., Маркитантов В., Прокопченко В., Мирошников А., Рытов А.

Донецкий национальный технический университет (ДонНТУ)

Последнее десятилетие ХХ века и начало ХХI характеризуются стремительным развитием FPGA– и HDL–технологий проектирования вычислительной техники (ВТ), основанных на использовании БИС с перестраиваемой архитектурой типа FPGA и CPLD [1-7] и языков программирования аппаратуры, таких как VHDL и VERILOG [8-12]. Развиваются также подходы и технологии диагностирования ВТ. Значительным событием в этой области была разработка стандарта IEEE 1149.01 «BOUNDARY SCAN» на контролепригодное проектирование дискретных устройств (ДУ) на основе БИС, в том числе FPGA и CPLD, разработанного объединенной группой по тестам – JTAG [13-14]. Благодаря новым технологиям появилась уникальная возможность создания больших проектов непосредственно на АРМ на базе персонального компьютера, что особенно важно для Украины, имеющей, с одной стороны, гигантский парк морально и физически устаревшей техники, и, с другой стороны, испытывающей известные проблемы в радиоэлектронной промышленности. В этой связи возникают актуальные задачи проведения научных исследований и подготовки инженеров по новым hardware–технологиям.

Мировые производители ПЛИС (XILINX, ALTERA, АTМЕЛ, АСТЕЛ и др.) и компании, занимающиеся разработкой САПР на их основе (ALDEC, SYNOPSYS и др.) проводят активную компанию по распространению своей продукции в СНГ и, в частности, на Украине, уделяя значительное внимание сфере образования. Фирма ALDEC при координации НТУУ–КПИ внедряет свои программные разработки в ВУЗах Украины, в том числе и в ДонГТУ [27].

В данной работе анализируется современное состояние FPGA- и HDL-технологий. Освещается опыт внедрения описанных технологий на кафедре ЭВМ ДонГТУ в учебный процесс и научные исследования [15,16].

Как одна из областей применения новых технологий предлагается разработка диагностического обеспечения ДУ, чему в работе уделяется особое внимание. Рассматривается методология решения диагностических задач, разработанная на кафедре ЭВМ ДонГТУ [17-19], позволяющая решать разнородные задачи детерминированного и случайного (псевдослучайного) тестирования ДУ единым подходом, основанным на использовании специально разработанной диагностической модели (Т-модель). Рассматривается структура экспериментальной подсистемы генерации и анализа тестов на базе САПР ACTIVE-HDL фирмы ALDEC Inc, США [10].

Особенности HDL- и FPGA-технологий

В настоящее время среди широкого круга критериев классификации hardware-технологий определяющими являются

![]() способ представления

(ввода, описания) проекта и

способ представления

(ввода, описания) проекта и

![]() способ выполнения

(изготовления) проекта.

способ выполнения

(изготовления) проекта.

По способу представления различают схематический и языковый способы. Первый основан на вводе проекта в виде схемы, второй - на представлении проекта на специальном языке описания (программирования) аппаратуры – HDL (Hardware Description Language), среди которых в последнее время наибольшую популярность получили VHDL и VERILOG [8-12]. Сравнительный анализ этих способов, приведенный в таблице 1, показывает неоспоримое преимущество языкового способа практически по всем параметрам, что особенно ярко проявляется для больших проектов.

Таблица 1 – Сравнительный анализ способов ввода проекта

|

Параметры |

Cхематический способ |

HDL-способ |

|

|

графическая |

текстовая и графическая |

|

|

ручной |

автоматический |

|

|

высокая |

не зависит |

|

|

медленная |

быстрая |

|

|

небольшой |

неограниченный |

|

проектирования |

Высокая |

не зависит |

По способу выполнения ВУ различают следующие основные способы:

![]() ASIC

(Applications Specific Integrated Circuit) -- проектирование ВУ на

основе

ASIC

(Applications Specific Integrated Circuit) -- проектирование ВУ на

основе

специализированных БИС;

![]() FPGA

(Field Programmable Gate Array) - проектирование ВУ на основе БИС с

FPGA

(Field Programmable Gate Array) - проектирование ВУ на основе БИС с

программируемой (перестраиваемой) структурой.

На рис. 1 схематично показаны структуры специализированной и программируемой (FPGA) БИС:

|

(a) (б)

Рисунок 1 – БИС, выполненные по ASIC- (а) и FPGA- технологиям (б)

(с разрешения ALDEC Inc.)

Процесс проектирования на основе совместного использования HDL-, ASIC- и FPGA-технологий показан на рис. 2. В таблице 2 дается сравнительная характеристика указанных способов.

Таблица 2 – Сравнительный анализ ASIC- FPGA-технологий

|

Параметр (характеристика) |

ASIC |

FPGA |

|

|

От 100 000$ |

Производство не требуется |

|

|

до 40 млн. вентилей |

свыше 4 млн. вентилей |

|

|

Требуется |

не требуется – программируется за секунды |

|

|

для больших партий |

для малых партий |

|

|

UNIX |

WINDOWS, LINUX на PС |

Рисунок 2 – Процесс проектирования БИС на базе ASIC- и FPGA-технологий

(с разрешения ALDEC Inc.)

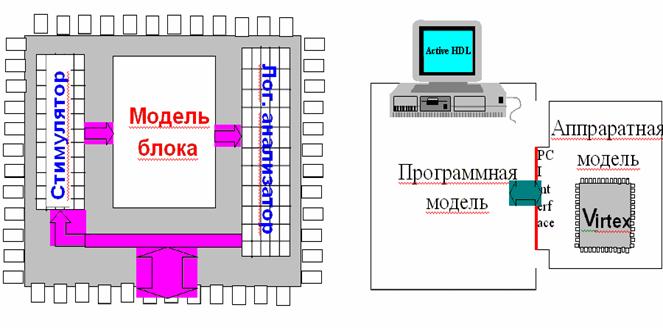

Еще одним важным отличительным свойством FPGA-технологии по сравнению с ASIC, кроме тех, что приведены в таблице 2, является возможность решения различных задач путем аппаратного моделирования решаемой задачи на специально разработанном для этой задачи сопроцессоре. C экономической точки зрения это рационально только на FPGA, обеспечивающих возможность многократного перепрограммирования сопроцессора. Такой способ аппаратного моделирования получил название HES-технологии [20] (рис.3).

( а ) ( б )

Рисунок 3 – HES – технология аппаратного моделирования задач (а)

и ее реализация в САПР ACTIVE-HDL на базе FPGA типа Virtex (б)

(с разрешения ALDEC Inc.)

Таким образом, сравнительный анализ основных технологий проектирования ВУ позволяет сделать выбор в пользу сочетания HDL- и FPGA-технологий. Используемые совместно они характеризуются следующими положительными особенностями [1-5, 20]:

![]() Сочетание схемного, автоматного

и языкового способов ввода проекта.

Сочетание схемного, автоматного

и языкового способов ввода проекта.

![]() Моделирование и отладка (TESTBENCH)

на всех этапах проектирования.

Моделирование и отладка (TESTBENCH)

на всех этапах проектирования.

![]() Поддержка IEEE-стандартов

на VHDL (1076-87/93) и VERILOG(1364-95).

Поддержка IEEE-стандартов

на VHDL (1076-87/93) и VERILOG(1364-95).

![]() Автоматический синтез FPGA–

и CPLD–устройств.

Автоматический синтез FPGA–

и CPLD–устройств.

![]() In System Programmable –

автоматическое реконфигурирование и периферийное сканирование по архитектуре BOUNDARY-SCAN

(IEEE std 1149.1); неограниченное число циклов переконфигурирований.

In System Programmable –

автоматическое реконфигурирование и периферийное сканирование по архитектуре BOUNDARY-SCAN

(IEEE std 1149.1); неограниченное число циклов переконфигурирований.

![]() Возможность построения сложной

вычислительной системы (ВС) на одном кристалле.

Возможность построения сложной

вычислительной системы (ВС) на одном кристалле.

![]() Проектирование и изготовление ВС

на персональном компьютере.

Проектирование и изготовление ВС

на персональном компьютере.

![]() Параметры

FPGA:

Параметры

FPGA:

![]() объем – до 4 млн.

вентилей;

объем – до 4 млн.

вентилей;

![]() системная частота – до 250

МГц;

системная частота – до 250

МГц;

![]() технологические нормы – до 0,18

мкм на 6 уровнях металла;

технологические нормы – до 0,18

мкм на 6 уровнях металла;

![]() задержка сигнала – 0.5 нс/вентиль;

задержка сигнала – 0.5 нс/вентиль;

![]() время выполнения арифметических

операций (в т.ч. операций умножения) – до 6 нс;

время выполнения арифметических

операций (в т.ч. операций умножения) – до 6 нс;

![]() число поддерживаемых стандартов

ввода/вывода (SelectIO) – до 16;

число поддерживаемых стандартов

ввода/вывода (SelectIO) – до 16;

![]() стоимость – 0,05 цент/вентиль.

стоимость – 0,05 цент/вентиль.

Литература

1. Программируемые логические ИМС на К-МОП структурах и их применение /П.П. Мальцев, Н.И. Гарбузов, А.П. и др. – М.: Энергоатомиздат, 1998.– 160 с.

2. The Programmable Logic Data Book // San Jose, California, US: XILINX (www.xilinx.com).

3. Программируемые логические интегральные схемы фирмы XILINX. Spartan-II. Каталог продукции. // М.; ЗАО “Scan” 2000г. 63с.

4. Программируемые логические интегральные схемы фирмы XILINX. Серия FAST FLASH CPLD. // М.; ЗАО “Scan” 2000г 80с.

5. Программируемые логические интегральные схемы фирмы XILINX. Серия VIRTEX. // М.; ЗАО “Scan” 2000г 47с.

6. Логические ядра и инструментальные модели на ПЛИС XILINX. Каталог продукции. // М.; ЗАО “Scan” 2000г 55с.

7. Стешенко ПЛИС фирмы ALTERA : проектирование устройств обработки // М. ДОДЭКА 2000г. - 126с.

8. Peter J.Ashenden. The designer’s Guide to VHDL / San Francisco California, US 1995г. 688c.

9. Bhasker J. A VHDL Synthesis Primer. Second Edition. // Star Galaxy Publishing, PA 18103 1996г. 296 с.

10. ACTIVE-HDL Серия. Книги 1–4. США, Невада: ALDEC, Май 1999 (www.aldec.com.ua).

11. Бибило П.Н. Основы языка VHDL. - Минск: Ин-т техн. кибернетики НАН Беларуси, 1999.- 202с.

12. VHDL - язык описания аппаратных средств: Учеб. пособие / А.С. Яицков; Под. ред. акад. B.C. Бурцева, акад. Б.С. Митина. М. : Изд-во МАТИ-РГТУ "ЛАТМЭС", 1998- 119с.

13. Test access Port and Boundary-Scan Architecture //IEEE Standart 1149.1 – 1990 (Includes IEEE Standart 1149.1a – 1993).

14. Abramovici M. Digital System Testing & Design. – IEEE, 1998. – 570 p.

15. Зинченко Ю., Дяченко О., Маркитантов В. и др.. Новые hardware-технологии в ДонГТУ / Материалы междунар. научн.-техн. конф. «Новые информационные технологии в САПР и АСУ». – Киев. –2001.- Киев: Украинский дом экономических и научн.-техн. знаний. – 2001. С 12 – 19.

16. Zinchenko Y. E. computer-aided design and hardware description languages / Сборник трудов Донецкого государственного технического университета. Серия: Проблемы моделирования и автоматизации проектирования динамических систем, выпуск 10. – Донецк: ДонГТУ, 1999.- С. 210-216.

17. Зинченко Ю.Е. Т-модель дискретного устройства и решение диагностических задач на ее основе // Вестник ТРТУ – ДонГТУ. Материалы II Международного семинара «Практика и перспективы институционного партнерства». Донецк, ДонГТУ, 2001, N 1. С 36 - 47.

18. Зинченко Ю.Е., Жилин К.Е., Козинец А.М., Алексеев П.С. Глазков Д.Е. Моделирование диагностических задач в научных исследованиях и учебном процессе/ Международная научно-методическая конф., 1999г., Днепродзержинск: ДГТУ. С 165-166.

19. Зинченко Ю.Е., Жилин К.Е., Алексеев П.С., Глазков Д.Е.. Диагностирование дискретных устройств на основе имитационного моделирования// Сборник научных трудов ХТУРЭ: ХТУРЭ.- 1999г., С 251-253.

20. www.aldec.com

21. Берглунд А.П. Проверка кристаллов, плат и системы в целом методом сквозного сдвигового регистра // Электроника, 1979 – № 1. –С. 35–39.

22. Уильямс Т.У., Паркер К.И. Проектирование контролепригодных устройств //ТИИЭР, 1983. – Т. 71. - № 1. - С. 122 - 139.

23. Williams T.W., Parker K.P. Design for testability //IEEE Trans. Comput., 1982 - №1.– p.2-14.

24. Ярмолик В.Н. Контроль и диагностика цифровых узлов ЭВМ. - Мн.: Наука и техника. 1988, - 240 с.

25. Барашко А.С., Скобцов Ю.А. и др. Моделирование и тестирование дискретных устройств. - Киев: Наук. думка, 1992.- 288с.

26. Тарасенко А.Н. Методы оценки и показатели тестируемости дискретных устройств (обзор) // Зарубежная радиоэлектроника, 1989, № 7. – C. 24-29.

27. www.aldec.com.ua