|

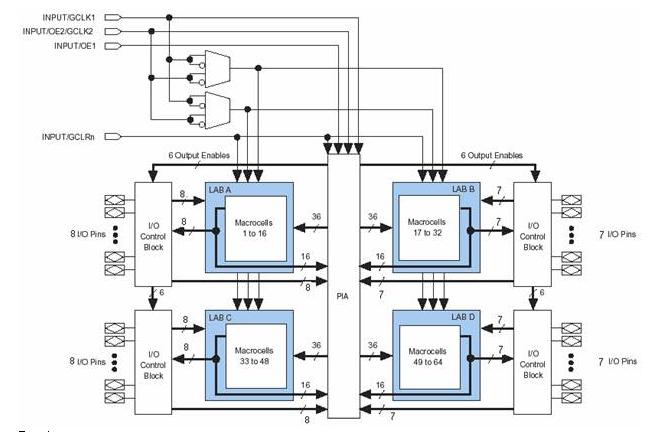

ОСВАИВАЕМ ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ МАТРИЦЫ ФИРМЫ ALTERA. Для большинства радиолюбителей конструкторов занимающихся собственными разработками давно известны и освоены цифровые микросхемы. Многие достаточно давно проектируют свои конструкции на микроконтроллерах так как это в значительной степени уменьшает габариты и улучшает функциональность устройств. Вот только беда в том, что не всё можно построить на основе контроллера. Быстродействующие устройства требующие мгновенной реакции на изменяющиеся входные сигналы построить на микроконтроллере не удастся так как в нём организована поэтапная (конвейерная) обработка команд в результате которых принимается решение о выдаче того или иного сигнала. Поэтому наряду с микроконтроллерами приходится использовать обычную логику, иногда с приличным количеством корпусов. Следствием этого является большое число внешних соединений, сложность конструкции и большие габариты печатных плат, большая длина соединительных проводников, сложность построения устройств с высокой тактовой частотой, низкая надёжность. Решением данной проблемы является использование программируемых логических интегральных схем (ПЛИС), которые представляют собой совокупность некоторого числа функциональных базовых элементов, не имеющих жестких электрических соединений между собой, что позволяет задавать практически произвольную конфигурацию с целью создания той или иной электронной схемы. На первом этапе ПЛИС представляли собой микросхемы с пережигаемыми перемычками такие как К556РТ4-РТ5 и др. на них можно было создать некоторые функции но запихнуть небольшую схему со счётчиками и триггерами было не возможно. Этапы проектирования устройств на основе простой логики плохо автоматизированы и в случае ошибки необходимо дорабатывать плату вводить дополнительные элементы. Изучение программного Пакета MAX+plus II BASELINE и ПЛИС фирмы Altera, позволит не только упростить схему но и не наступать на множество подводных камней. Данное программное обеспечение можно использовать и при проектировании схем на 155серии и её аналогах. Для программирования (создания соединений) в PLD (а также и CPLD) используются технологии EPROM, EEPROM и FLASH. Для радиолюбителей наибольший интерес представляют микросхемы FLASH так как они позволяют перепрограммировать кристалл порядка 100 раз и после снятия питающего напряжения сохраняют структуру установленную в результате программирования. В данной статье будут рассмотрены вопросы поэтапной разработки схем на основе ПЛИС фирмы Altera - EPM3064А как наиболее дешёвой. Она размещена в 44 выводном корпусе типа PLCC. Микросхема имеет смешанное питание и мультивольтовый интерфейс ввода/вывода (I/O). Напряжение питания логического ядра 3,3 вольта элементов ввода/вывода – 5; 3,3; и 2,5 вольта. Максимальная тактовая частота 227,3мГц в зависимости от модификации. Установкой битов конфигурации возможно управлять крутизной фронтов (Slew Rate) входных/выходных сигналов. Имеется также реализация выходов с открытым стоком установкой бита (Open Drain). Имеется возможность установить режим энергосбережения который уменьшает более чем на 50% потребляемую мощность. Имеется также возможность установить бит секретности (security bit) который не позволит скопировать внутреннюю конфигурацию микросхемы. Данная микросхема имеет 4 блока логических матриц и 64 макроячейки. Программируемые триггеры макроячеек имеют индивидуальные входы синхронизации (clock), разрешения синхронизации (clock enable), обнуления (clear), и предустановки (preset). Каждая макроячейка может рассматриваться как программируемая матрица И и фиксированная матрица ИЛИ. На выходе матрицы ИЛИ включен регистр с конфигурируемой схемой управления. Схема управления регистром обеспечивает независимо программируемые сигналы синхронизации, разрешения синхронизации, обнуления, и предустановки. В данную микросхему по мнению автора можно запихнуть 10-15 корпусов 155 серии (в продаже имеются микросхемы EPM3256 с 16 блоками логических матриц и 158 выводами). Архитектура EPM3064A включает следующие элементы: Логические блоки (LABs). Макроячейки (Macrocells). Логические расширители, разделяемый (Shareable) и параллельный (Parallel). Программируемая матрица соединений (PIA). Блоки управления вводом/выводом (I/O control blocks). Микросхема имеет четыре специализированных входа (dedicated pin) которые могут использоваться как входы общего назначения или входы высокоскоростных глобальных управляющих сигналов (синхронизации –clock, обнуления clear и двух сигналов разрешения выхода - enable), для каждой макроячейки и контакта ввода вывода. Блок схема изображена на рис1.

Основу архитектуры EPM3064A составляют логические блоки, состоящие из 16 макроячеек. Логические блоки соединяются вместе при помощи программируемой матрицы соединений (PIA). К каждому логическому блоку подводятся следующие сигналы: 36 сигналов от PIA, используемых в качестве логических входов. Глобальные управляющие сигналы. Непосредственные цепи от входных буферов к регистрам, обеспечивающие высокое быстродействие. Подробнее о функциональном составе и принципе работы микросхемы можно почитать в [2].

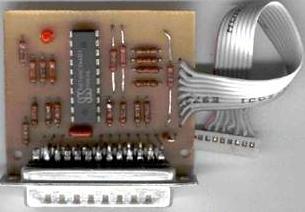

Для программирования микросхемы необходимо изготовить специальный загрузочный кабель ByteBlasterMV Рис2. Он позволяет быстро и эффективно изменять конфигурацию ПЛИС как в стадии тестирования проекта, так и во время эксплуатации. Перепрограммирование может быть выполнено непосредственно в системе. Пока идет программирование, выводы микросхемы переводятся в третье состояние, для избежания конфликта с системой. Сопротивление внутренних “подтягивающих” резисторов 50 кОм.

|

|