Войтов Геннадий Владимирович

Факультет вычислительной техники и информатики

Специальность: Компьютерные системы и сети

Факультет вычислительной техники и информатики

Специальность: Компьютерные системы и сети

| Быстродействие | MMACS Доля респондентов, % |

| < 100 | 19,3 |

| 100–600 | 24,3 |

| 600–1000 | 11,5 |

| 1000–6000 | 21,6 |

| 6000–10000 | 9,2 |

| > 10000 | 14,2 |

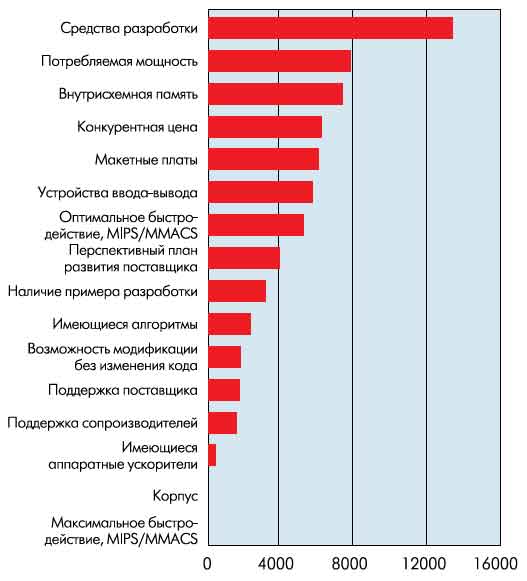

Рис.1. Критерии выбора процессора обработки сигнала

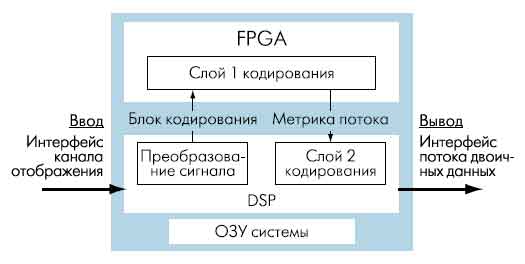

Но при этом приходится принимать немало компромиссных решений, касающихся интерфейсов устройств ввода-вывода данных (устройств В/В), межпроцессорной связи, конфигурации памяти, интерфейса хоста, управления, программно-аппаратных средств FPGA. Все эти решения должны быть тщательно продуманы и поддержаны типовым программным обеспечением [5]. Интерфейс. Для реконфигурации устройств В/В во многих современных представленных на рынке промышленных платах вычислительных систем уже имеются FPGA вычислительные элементы. Размещение таких элементов вблизи устройств ввода/вывода данных позволяет поддерживать любые стандарты передачи данных, в том числе и такие отличающиеся друг от друга стандарты, как PCI, PCI Express, USB, GigE, Serial RapidIO. Это особенно выгодно при использовании плат новых форматов – VITA 41, VITA 46 и АМС, которые поддерживают быстродействующие последовательно-параллельные и параллельно-последовательные преобразователи (SerDes), способные работать с несколькими различными протоколами. Межпроцессорная связь. Помимо выбранного типа вычислительных элементов (DSP или FPGA) на производительность системы влияет качество связи между ними. Очевидно, оно должно быть достаточно высоким. Кроме того, связь должна быть детерминированной и устанавливаться с малой задержкой. Менее очевиден тот факт, что скорость передачи данных в среднем должна быть выше, чем полоса пропускания устройств В/В платы. Главная задача гибридной архитектуры заключается в том, чтобы нужный тип вычислительного элемента, размещенный в нужном месте системы, использовался в нужное время. Для ее выполнения данные, как правило, необходимо передавать между различными элементами и зачастую не один раз (рис.2).

Рис.2. Пример межпроцессорной связи

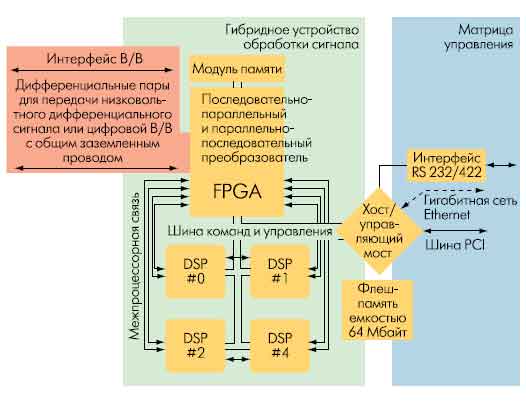

Данные обычно вводятся в систему на плате через интерфейс устройства В/В матрицы FPGA, которая выполняет их предварительную обработку. Иногда, как в случае преобразователя с понижением частоты или выполнения алгоритма сжатия импульсов, предварительная обработка приводит к снижению скорости передачи данных. Однако общие алгоритмы предварительной обработки, включая алгоритмы реализации фильтров, дешифраторов, БПФ, существенно не влияют на скорость передачи данных, а иногда приводят к ее увеличению. Поэтому, когда при передаче данных элементу DSP с целью дополнительной обработки, а также возврата их FPGA для окончательной обработки и вывода требуется минимальная пропускная способность, скорость межпроцессорной связи должна быть равна скорости передачи данных устройств В/В. Правда, в более общем случае, когда ресурсы FPGA обеспечивают совместную с DSP обработку данных или когда вычислительные элементы построены на нескольких FPGA и/или DSP, скорость межпроцессорной связи может многократно превышать скорость передачи данных устройств В/В. Конфигурация памяти. Не все ЦОС-устройства нуждаются в памяти большого объема. Но в случае наличия такой памяти ее тип, конфигурация и даже местоположение зависят от требований конкретного применения. Совместное использование модульной памяти большого объема и FPGA позволяет формировать ее различные типы и конфигурации путем изменения модуля и репрограммирования вентильной матрицы. Например, 64-разрядную шину данных можно использовать для поддержки одного банка памяти с длиной слова 64 бит или можно реконфигурировать для поддержки двух независимых банков памяти с длиной слова каждого 32 бит. При этом банки памяти могут быть разных типов. Интерфейс хоста и управление. Наиболее приемлемый способ реализации интерфейса хоста промышленных плат с гибридным ЦОС-устройством – соединить стандартные интерфейсы и отдельные шины команд и управления каждого FPGA и DSP вычислительного элемента с помощью моста. Поскольку при этом линии связи будут перпендикулярны линиям передачи данных, интерфейс хоста часто называют матрицей управления (в отличие от матрицы данных). Наличие независимой матрицы управления позволяет хосту выполнять непосредственную выборку данных и управление любыми ресурсами, не влияя на пропускную способность шин данных. Шина команд и управления обеспечивает хосту непосредственный доступ к модулю памяти. Она может также служить дополнительным средством межпроцессорной связи. Общий вид промышленной платы с гибридным ЦОС-устройством и решением рассмотренных проблем представлен на рис.3.

Рис.3. Гибридная архитектура процессора обработки сигнала связи

Программно-аппаратные средства FPGA. При больших возможностях FPGA, программирование матрицы может быть обескураживающим. Если необходимо обеспечить высокое быстродействие FPGA ЦОС-устройства, расположенного на промышленной плате с фиксированными положениями выводов и внешними интерфейсами, задача еще больше усложняется. Чтобы облегчить ее решение, для интерфейсов платы должны быть предусмотрены IP-модули (в том числе устройств В/В, памяти, межпроцессорной связи, шины команд и управления). В идеале структура FPGA должна поддерживать программируемую связь между IP-модулями наряду с документально утвержденными их интерфейсами, позволяющими пользователю применять модули обработки сигнала, которые могут быть введены в потоки данных. В этом случае потоки данных, показанные на рис.2, легко реализовать путем перевода требуемых блоков предварительной/совместной/пост-обработки сигналов (на рисунке они показаны желтым цветом) в конфигурируемые программой потоки данных. В ходе процесса обработки шины команд и управления могут конфигурировать требуемые для данного применения потоки данных между интерфейсами В/В, IP-модулями, DSP и другими ресурсами платы. Программное обеспечение. Чем сложнее аппаратные средства, тем больше потребность в ПО низкого уровня для поддержки интерфейса хоста, отладки системы, команд и управления временем исполнения программы. Для гибридного устройства, которое сложнее однотипного, унификация программных средств особенно важна. Отладка может потребовать специальных ресурсов для реализации различных технических решений, но конфигурации, управление и данные всех вычислительных элементов должны быть сведены в единую библиотеку интерфейса драйвера хоста. Если рассмотренные выше программно-аппаратные средства вентильной матрицы реализованы, для задания потока данных и управления им необходимы программные средства. Кроме того, для выполнения операций Рис.2. Пример межпроцессорной связи передачи данных, прерываний, координации и синхронизации следует обеспечить программную поддержку взаимодействия DSP-элементов с FPGA. Эту задачу можно решить с помощью кода, библиотек, интерфейса обмена сообщениями или ОС [5]. СодержаниеРис.4. Сравнение возможностей кодеков на DSP с FPGA-сопроцессором и на обычном DSP с учетом стандартов кодирования, типов операций, числа каналов и разрешения

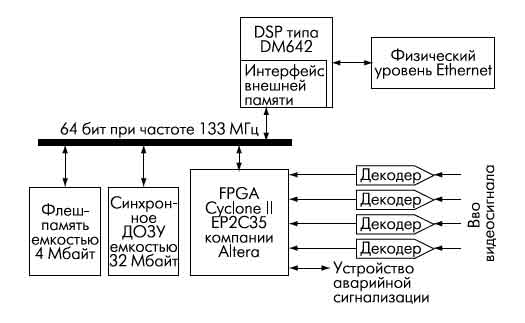

Рис.5. Применение FPGA в качестве сопроцессора в четырехканальной системе видеонаблюдения Raven-D

Для оптимизации быстродействующих цифровых систем видеонаблюдения компания Mango DSP разработала четырехканальную систему видеонаблюдения Raven-D на основе недорогой FPGA Cyclone II фирмы Altera и DSP DM642 фирмы Texas Instruments (рис.5). DSP работает на тактовой частоте до 1 ГГц. Число его интерфейсов В/В, команд/тактовых сигналов и умножителей ограничено, длина слов фиксирована. К тому же, для связи с другими DSP используются PCI шины с относительно небольшим быстродействием. Микросхема FPGA может работать с большим числом команд/тактовых сигналов и словами переменной длины, содержит на два порядка больше умножителей, чем DSP. Так, в FPGA типа Cyclone II до 150 18?18 умножителей/накапливающих сумматоров, работающих на частоте до 250 МГц каждый, и около 70 тыс. стандартных логических элементов. FPGA, как и DSP, имеет доступ к различным современным типам ДОЗУ. Межпроцессорную связь обеспечивают шины LVDS с быстродействием 1 Гбит/с или шины SerDes с быстродействием более 1 Гбит/с. Недостатки FPGA ЦОС-процессора – длительное время разработки и значительно меньшие значения тактовой частоты в сравнении с DSP. Таким образом, DSP и FPGA дополняют друг друга. DSP с высоким быстродействием выполняет новые и сложные алгоритмы и от двух до четырех вычислений одновременно, а FPGA – одновременно векторные и матричные математические операции. Кроме того, микросхема FPGA удобна для установления связи между многочисленными процессорными узлами, для сбора данных и распределения их между устройствами цифровой обработки сигнала, а также для перестройки дополнительных вычислений в одном выходном потоке. В системе видеонаблюдения FPGA может использоваться в качестве сопроцессора для предварительной обработки видеосигналов (стабилизации, фильтрации и обнаружения перемещений), а также для выполнения функции сжатия видеоизображения [8]. DSP в сочетании с FPGA успешно работает и в кодере JPEG2000 компании BroadMotion (рис.6). Применение дополнительной недорогой микросхемы FPGA Cyclone II фирмы Altera или Spartan 3 фирмы Xilinx позволило расширить

Рис.6. Применение FPGA в качестве сопроцессора в кодере JPEG2000 компании BroadMotion

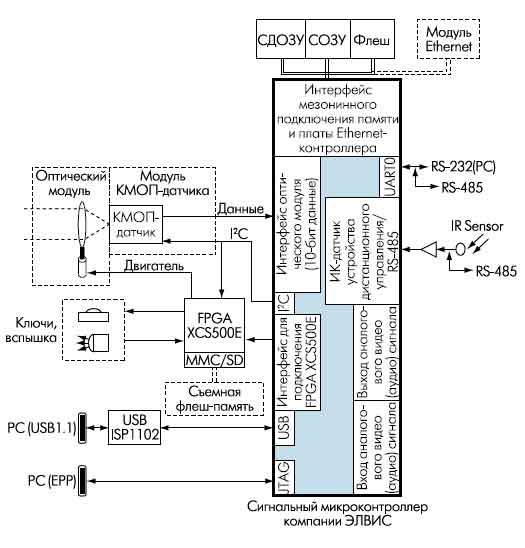

функциональные возможности кодера и улучшить качество изображения при соблюдении требований к обеспечению достаточно низкой стоимости. При обработке полноцветного видеоизображения с разрешением 720?480 пикселов кодек фирмы BroadMotion кодирует более 50 кадров в секунду при производительности 25 Мбайт/с. Применение такого сопроцессора позволяет более чем на порядок улучшить эффективность кодера в сравнении с устройством только на DSP [9]. Хорошие результаты могут быть получены и при построении системы на основе трех типов ЦОС-устройств. Пример совместного использования УП/DSP/FPGA – плата контроллера IP-камеры на базе трехъядерного сигнального микроконтроллера MCam02, разработанного компанией Элвис в рамках платформы "Мультикор" (рис.7). Плата, помимо контроллера, содержит недорогую микросхему FPGA типа Spartan 3 фирмы Xilinx (для организации интерфейса средства управления объективом с переменным фокусным расстоянием, интерфейса съемной флеш-памяти, интерфейса I2C для ввода-вывода высококачественного аудиосигнала, дополнительного интерфейса для кнопок и вспышки). В результате эффективность микроконтроллера при выполнении операций обработки и передачи видеосигнала повышается [10]. Содержание

Рис.7. Структурная схема платы контроллера IP-камеры (MCam02-IP)

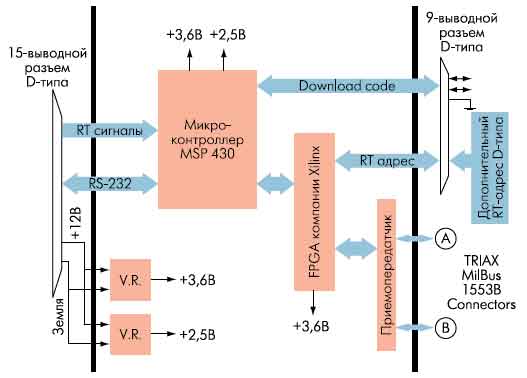

После демодуляции сигнала FPGA динамическую обработку в реальном времени может выполнять DSP. В передающем канале процесс повторяется в обратном порядке. Для работы модемов в SDR-системах и поддержки операций модуляции, демодуляции, передискретизации с повышением и понижением частоты, а также коррекции ошибок нужно совмещать DSP и быстродействующие FPGA. В зависимости от типа алгоритмов модема беспроводного устройства система контроля ошибок при передаче данных или прямой коррекции ошибок, может быть реализована с помощью или DSP, или логических вентилей. Например, алгоритмы кодирования и декодирования Рида-Соломона, наряду с кодированием в сверхточных и турбокодах, проще и лучше выполнять сигнальным процессором в силу лучшего соотношения показателя стоимость–мощность. Однако при более сложной техникие декодирования алгоритмов для коррекции ошибок в сверхточных или турбокодах целесообразно применять логические вентили, встроенные в процессор или FPGA. В этом отношении применение FPGA в SDR-системах в качестве сопроцессора имеет множество плюсов, поскольку его гибкость позволяет поддерживать несколько протоколов. Управление доступом к среде передачи данных, предусматривающее кодирование и декодирование пакетов двухразрядных данных, передачу их интерфейсу сети и от него, а также управление потоками и конфликтами в канале, требует высокоэффективной операционной системы реального времени и предполагает выполнение большого числа операций. Лучшими ЦОС-устройствами для выполнения функций управления доступом к среде передачи считаются УП. Таким образом, для реализации многоканальных многопротокольных SDR систем необходимо сочетать УП, DSP и FPGA [11]. Сочетание сигнального процессора и FPGA обеспечивает очень гибкое системное решение при работе в военных стандартах AFDX, ARINC и MIL-STD-853. Анализ и обработку данных выполняет процессор, в то время как ЦОС на FPGA обеспечивает их ввод/вывод. Большинству FPGA для хранения данных конфигурации прибора требуется внешняя энергонезависимая память. После включения питания эти данные загружаются в FPGA. Часто такая загрузка выполняется последовательно и занимает сотни миллисекунд. Сократить время загрузки могут микроконтроллеры, программируемые данными флеш-памяти через интерфейс стандарта RS-232. Благодаря этому плату можно модернизировать с помощью новой версии ПО без извлечения какой-либо части установленной аппаратуры. К другим достоинствам этого метода относится возможность программирования любой модификации прибора, загрузки конфигурации FPGA в параллельном режиме через процессорную шину, благодаря чему эта операция занимает значительно меньше времени, чем при последовательной загрузке. В итоге уменьшается число компонентов системы, увеличивается время наработки на отказ, уменьшаются физические размеры и значительно снижается стоимость платы.

Рис.8. Объединение микроконтроллера и FPGA с различными системными интерфейсами

На рис.8 показан пример сочетания микроконтроллера и FPGA, включая различные системные интерфейсы платы. В конструкции использован RISC-микроконтроллер MSP430 компании Texas Instruments с чрезвычайно малой потребляемой мощностью: ток в рабочем режиме не превышает 10 мА, в неактивном режиме – ~1 мкА. Микроконтроллер содержит два асинхронных последовательных порта, восемь 12-разрядных АЦП, несколько общих устройств В/В, ШИМ и таймеры. Содержание