Войтов Геннадій Володимирович

Факультет: Обчислювальної техніки інформатики

Спеціальність: Комп'ютерні системи та мережі

Факультет: Обчислювальної техніки інформатики

Спеціальність: Комп'ютерні системи та мережі

Сьогодні технологія цифрової обробки сигналу (ЦГЗ) стала невід'ємною частиною повсякденного життя. ЦГЗ-пристрої застосовуються в найрізноманітніших системах - від мобільних телефонів, комп'ютерних модемів, цифрових телевізорів, МР3-і DVD-плеєрів до систем голосового трафіку по IP-мережам, медичної апаратури, навігаторів автомобілів. В даний час можна виділити три основних класу ЦГЗ-пристроїв - універсальні процесори (УП), сигнальні процесори, або процесори цифрової обробки сигналу (DSP), і пристрої цифрової обробки сигналу на основі програмувальних користувачем вентільних матриць (FPGA). Останні - один з різновидів спеціалізованих мікросхем (ASIC). Наприкінці 1980-х - початку 1990-х років DSP - мікропроцесори, спеціально розроблені для цифрової обробки сигналів, за своїми характеристикам істотно перевершували традиційні УП. Але останнім часом різниця між цими двома класами процесорів практично зникає, і сьогодні багато хто УП виконують серйозні задачі цифрової обробки сигналу. Все частіше перевагу перед спеціалізованими ASIC-мікросхемами віддається перспективним ЦГЗ-пристроїв на основі FPGA з гнучкою архітектурою, високим рівнем параллелизма роботи та досить високою продуктивністю, особливо при розробці систем, випускаються малими або середніми серіями. Зміст

Кожен тип ЦГЗ-пристроїв можна розбити на процесори молодших та старших моделей. Проаналізуємо з цієї точки зору представлені на сучасному ринку ЦГЗ-пристрої.

| Швидкодія | MMACS Доля респондентов, % |

| < 100 | 19,3 |

| 100–600 | 24,3 |

| 600–1000 | 11,5 |

| 1000–6000 | 21,6 |

| 6000–10000 | 9,2 |

| > 10000 | 14,2 |

Якщо потрібно продуктивність понад 1000 ММАСS, доцільно застосовувати гібридні пристрою на основі DSP / FPGA. Така "гібридна архітектура", в якій на одній платі розміщені FPGA і DSP обчислювальні елементи, як правило, використовується і при реалізації вбудованих процесорів цифрової обробки сигналу.

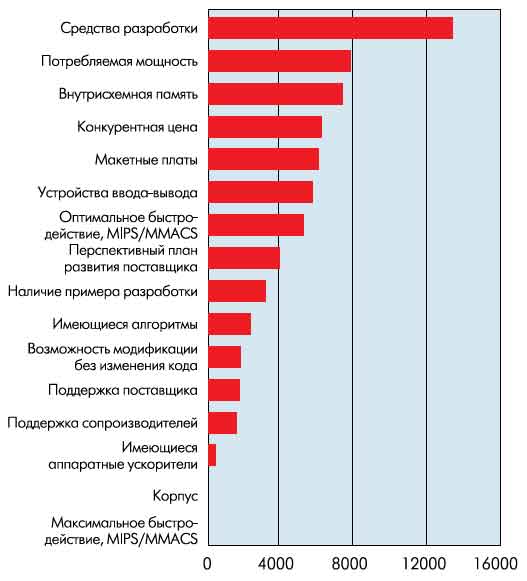

Рис.1. Критерії вибору процесора обробки сигналу

Але при цьому доводиться приймати чимало компромісних рішень, що стосуються інтерфейсів пристроїв введення-виведення даних (пристроїв В / В), межпроцессорной зв'язку, конфігурації пам'яті, інтерфейсу хоста, управління, програмно-апаратних засобів FPGA. Всі ці рішення повинні бути ретельно продумані і підтримані типовим програмним забезпеченням [5].

Інтерфейс. Для реконфигурации пристроїв В / В у багатьох сучасних представлених на ринку промислових платах обчислювальних систем уже є FPGA обчислювальні елементи. Розміщення таких елементів поблизу пристроїв введення / виводу даних дозволяє підтримувати будь-які стандарти передачі даних, у тому числі і такі відрізняються один від одного стандарти, як PCI, PCI Express, USB, GigE, Serial RapidIO. Це особливо вигідно при використанні плат нових форматів - VITA 41, VITA 46 і АМС, які підтримують швидкодіючі послідовно-паралельні і паралельно-послідовні перетворювачі (SerDes), здатні працювати з кількома різними протоколами.

Межпроцессорная зв'язок. Крім вибраного типу обчислювальних елементів (DSP або FPGA) на продуктивність системи впливає якість зв'язку між ними. Очевидно, вона повинна бути досить високим. Крім того, зв'язок повинна бути детермінований і встановлюватися з малою затримкою. Менш очевидний той факт, що швидкість передачі даних в середньому повинна бути вище, ніж смуга пропускання пристроїв В / В плати. Головна задача гібридної архітектури полягає в тому, щоб потрібний тип обчислювального елемента, розміщений в потрібному місці системи, використовувався в потрібний час. Для її виконання дані, як правило, необхідно передавати між різними елементами і найчастіше не один раз (рис.2).

Рис.2. Приклад межпроцессорной зв'язку

Дані зазвичай вводяться в систему на платі через інтерфейс пристрою В / В матриці FPGA, яка виконує їх попередню обробку. Іноді, як у випадку перетворювача з пониженням частоти або виконання алгоритму стиснення імпульсів, попередня обробка призводить до зниження швидкості передачі даних. Однак загальні алгоритми попередньої обробки, включаючи алгоритми реалізації фільтрів, дешифратор, БПФ, істотно не впливають на швидкість передачі даних, а іноді призводять до її збільшення. Тому, коли при передачі даних елементу DSP з метою додаткової обробки, а також повернення їх FPGA для остаточної обробки і виводу потрібна мінімальна пропускна здатність, швидкість межпроцессорной зв'язку повинна бути рівна швидкості передачі даних пристроїв В / В. Щоправда, у більш загальному випадку, коли ресурси FPGA забезпечують спільну з DSP обробку даних або коли обчислювальні елементи побудовані на декількох FPGA та / або DSP, швидкість межпроцессорной зв'язку може багаторазово перевищувати швидкість передачі даних пристроїв В / В.

Конфігурація пам'яті. Не всі ЦГЗ-пристрої потребують пам'яті великого об'єму. Але у випадку наявності такої пам'яті її тип, конфігурація і навіть місце розташування залежать від вимог конкретного застосування. Спільне використання модульної пам'яті великого об'єму і FPGA дозволяє формувати її різні типи та конфігурації шляхом зміни модуля і репрограммірованія вентільной матриці. Наприклад, 64-розрядну шину даних можна використовувати для підтримки одного банку пам'яті з довжиною слова 64 біт або можна реконфігуріровать для підтримки двох незалежних банків пам'яті з довжиною слова кожного 32 біт. При цьому банки пам'яті можуть бути різних типів.

Інтерфейс хоста та управління. Найбільш прийнятний спосіб реалізації інтерфейсу хоста промислових плат з гібридним ЦГЗ-пристроєм - поєднати стандартні інтерфейси та окремі шини команд та управління кожного FPGA і DSP обчислювального елемента за допомогою моста. Оскільки при цьому лінії зв'язку будуть перпендикулярні лініях передачі даних, інтерфейс хоста часто називають матрицею управління (на відміну від матриці даних). Наявність незалежної матриці керування дозволяє хосту виконувати безпосередню вибірку даних і управління будь-якими ресурсами, не впливаючи на пропускну здатність шин даних. Шина команд і керування забезпечує хосту безпосередній доступ до модуля пам'яті. Вона може також служити додатковим засобом межпроцессорной зв'язку. Загальний вигляд промислової плати з гібридним ЦГЗ-пристроєм і рішенням розглянутих проблем представлений на рис.3.

Рис.3. Гібридна архітектура процесора обробки сигналу зв'язку

Програмно-апаратні засоби FPGA. При великих можливостях FPGA, програмування матриці може бути обескуражівающім. Якщо необхідно забезпечити високу швидкодію FPGA ЦГЗ-пристрої, розташованого на промисловій платі з фіксованими положеннями висновків і зовнішніми інтерфейсами, завдання ще більше ускладнюється. Для того, щоб полегшити її рішення, для інтерфейсів плати повинні бути передбачені IP-модулі (у тому числі пристроїв В / В, пам'яті, межпроцессорной зв'язку, шини команд і управління). В ідеалі структура FPGA повинна підтримувати програмовану зв'язок між IP-модулями поряд з документально затверджених їх інтерфейсами, що дозволяють користувачеві застосовувати модулі обробки сигналу, які можуть бути введені в потоки даних. У цьому випадку потоки даних, які ви бачите на мал.2, легко реалізувати шляхом переказу необхідних блоків попередньою / спільної / пост-обробки сигналів (на малюнку вони показані жовтим кольором) у що конфiгуруються програмою потоки даних. В ході процесу обробки шини команд та управління можуть конфігурувати необхідні для даного застосування потоки даних між інтерфейсами В / В, IP-модулями, DSP та іншими ресурсами плати.

Програмне забезпечення. Чим складніше апаратні засоби, тим більша потреба в ПЗ низького рівня для підтримки інтерфейсу хоста, налагодження системи, команд та управління часом виконання програми. Для гібридного пристрою, який складніше однотипного, уніфікація програмних засобів особливо важлива. Отладка може вимагати спеціальних ресурсів для реалізації різних технічних рішень, але конфігурації, управління та дані всіх обчислювальних елементів повинні бути зведені в єдину бібліотеку інтерфейсу драйвера хоста. Якщо розглянуті вище програмно-апаратні засоби вентільной матриці реалізовані, для завдання потоку даних і керування їм необхідні програмні засоби. Крім того, для виконання операцій Рис.2. Приклад межпроцессорной зв'язку передачі даних, переривань, координації і синхронізації слід забезпечити програмну підтримку взаємодії DSP-елементів з FPGA. Цю задачу можна вирішити за допомогою коду, бібліотек, інтерфейсу обміну повідомленнями або ОС [5].

Рис.4. Порівняння можливостей кодеків на DSP з FPGA-сопроцессором і на звичайному DSP з урахуванням стандартів кодування, типів операцій, числа каналів та дозволи

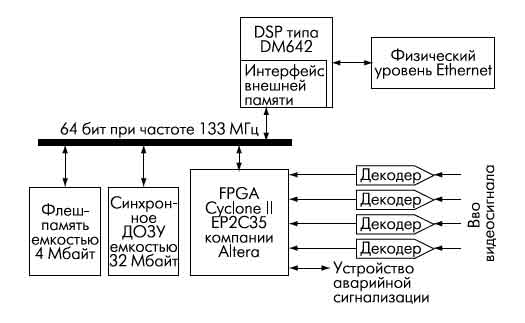

Рис.5. Застосування FPGA як сопроцессора в чотирьохканальний системі відеоспостереження Raven-D

Для оптимізації швидкодіючих цифрових систем відеоспостереження компанія Mango DSP розробила чотирьохканальний систему відеоспостереження Raven-D на основі недорогий FPGA Cyclone II фірми Altera і DSP DM642 фірми Texas Instruments (рис.5). DSP працює на тактовій частоті до 1 ГГц. Число його інтерфейсів В / В, команд / тактовим сигналів і помножувач обмежена, довжина слів фіксована. До того ж, для зв'язку з іншими DSP використовуються PCI шини з відносно невеликим швидкодією. Мікросхема FPGA може працювати з великою кількістю команд / тактовим сигналів та словами змінної довжини, містить на два порядки більше помножувач, ніж DSP. Так, у FPGA типу Cyclone II до 150 18? 18 помножувач / накопичуються суматори, що працюють на частоті до 250 МГц кожен, і близько 70 тис. стандартних логічних елементів. FPGA, як і DSP, має доступ до різних сучасним типам дозу. Межпроцессорную зв'язок забезпечують шини LVDS з швидкодією 1 Гбіт / с або шини SerDes з швидкодією понад 1 Гбіт / с. Недоліки FPGA ЦГЗ-процесора - тривалий час розробки і значно менші значення тактової частоти в порівнянні з DSP.

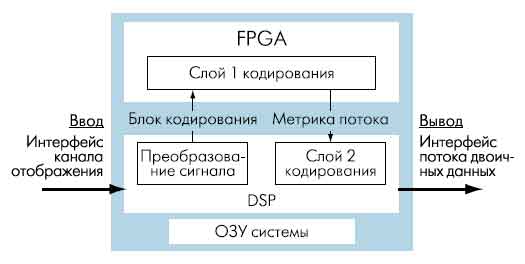

Рис.6. Застосування FPGA як сопроцессора в кодери JPEG2000 компанії BroadMotion

функціональні можливості кодери і поліпшити якість зображення при дотриманні вимог до забезпечення достатньо низькою вартістю. При обробці повнокольорового відеозображення з роздільною здатністю 720? 480 пікселів кодек фірми BroadMotion кодує більш 50 кадрів в секунду при продуктивності 25 Мбайт / с. Застосування такого сопроцессора дозволяє більш ніж на порядок поліпшити ефективність кодери в порівнянні з пристроєм лише на DSP [9].

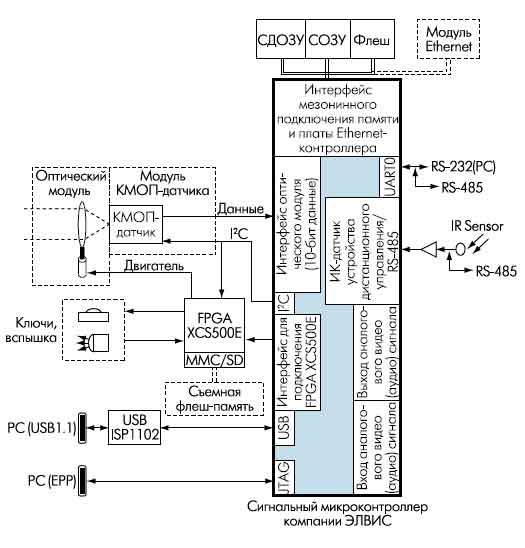

Гарні результати можуть бути отримані і при побудові системи на основі трьох типів ЦГЗ-пристроїв. Приклад спільного використання УП / DSP / FPGA - плата контролера IP-камери на базі трех'ядерного сигнального мікроконтролера MCam02, розробленого компанією Елвіс в рамках платформи "Мультікор" (рис.7). Плата, крім контролера, містить недорогу мікросхему FPGA типу Spartan 3 фірми Xilinx (для організації інтерфейсу засоби керування об'єктивом зі змінним фокусною відстанню, інтерфейсу знімній флеш-пам'яті, інтерфейсу I2C для вводу-виводу високоякісного аудіосигналу, додаткового інтерфейсу для кнопок і спалаху). В результаті ефективність мікроконтролера при виконанні операцій обробки та передачі відеосигналу підвищується [10].

Щоб досягти балансу вартості, потужності, швидкодії, гнучкості та надійності розробники при побудові архітектури програмувальних радіоустройств (SDR), у тому числі військового призначення, також використовують комбінацію процесорних елементів. SDR-системи працюють з сигналами різної форми хвилі, і для їх цифрового перетворення з пониженням частоти необхідна гнучка логіка програмованої вентільной матриці.

Рис.7. Структурна схема плати контролера IP-камери (MCam02-IP)

Після демодуляціі сигналу FPGA динамічну обробку в реальному часі може виконувати DSP. У переданому каналі процес повторюється у зворотному порядку. Для роботи модемів у SDR-системах та підтримки операцій модуляції, демодуляціі, передіскретізаціі з підвищенням і зниженням частоти, а також корекції помилок потрібно поєднувати DSP і швидкодіючі FPGA. В залежності від типу алгоритмів модему бездротового пристрою система контролю помилок при передачі даних або прямої корекції помилок, може бути реалізована за допомогою або DSP, або логічних вентилів. Наприклад, алгоритми кодування та декодування Ріда-Соломона, поряд з кодуванням в сверхточних і турбокодах, простіше і краще виконувати сигнальним процесором в силу кращого співвідношення показника ціна-потужність. Однак при більш складної техніки декодування алгоритмів для корекції помилок у сверхточних або турбокодах доцільно застосовувати логічні вентилі, вбудовані в процесор або FPGA. В цьому відношенні застосування FPGA в SDR-системах як сопроцессора має багато плюсів, оскільки його гнучкість дозволяє підтримувати декілька протоколів.

Управління доступом до середовища передачі даних, що передбачає кодування та декодування пакетів двухразрядних даних, передачу їх інтерфейсу мережі і від нього, а також управління потоками і конфліктами в каналі, вимагає високоефективної операційної системи реального часу і передбачає виконання великого числа операцій. Кращими ЦГЗ-пристроями для виконання функцій управління доступом до середовища передачі вважаються УП. Таким чином, для реалізації багатоканальних многопротокольних SDR систем необхідно поєднувати УП, DSP і FPGA [11].

Поєднання сигнального процесора і FPGA забезпечує дуже гнучке системне рішення при роботі у військових стандартах AFDX, ARINC і MIL-STD-853. Аналіз та обробку даних виконує процесор, у той час як ЦГЗ на FPGA забезпечує їх введення / виведення. Більшості FPGA для зберігання даних конфігурації приладу потрібна зовнішня енергонезалежна пам'ять. Після включення живлення ці дані завантажуються в FPGA. Часто така завантаження виконується послідовно і займає сотні мілісекунд. Скоротити час завантаження можуть мікроконтролери, програмувальні даними флеш-пам'яті через інтерфейс стандарту RS-232. Завдяки цьому плату можна модернізувати за допомогою нової версії ПЗ без вилучення будь-якої частини встановленої апаратури. До інших достоїнств цього методу відноситься можливість програмування будь-якої модифікації приладу, завантаження конфігурації FPGA в паралельному режимі через процесорну шину, завдяки чому ця операція займає значно менше часу, ніж при послідовної завантаження. В результаті зменшується кількість компонентів системи, збільшується час напрацювання на відмову, зменшуються фізичні розміри і значно знижується вартість плати.

Рис.8. Об'єднання мікроконтролера і FPGA з різними системними інтерфейсами

На рис.8 показаний приклад поєднання мікроконтролера і FPGA, включаючи різні системні інтерфейси плати. В конструкції використаний RISC-мікроконтроллер MSP430 компанії Texas Instruments з надзвичайно малою споживаною потужністю: струм в робочому режимі не перевищує 10 мА, в неактивному режимі - ~ 1 мкА. Мікроконтроллер містить дві асинхронних послідовних порту, вісім 12-розрядних АЦП, кілька загальних пристроїв В / В, шим і таймери.