Cборник материалов пятой всеукраинской научнотехнической конференции студентов, аспирантов и молодых ученых "Комп'ютерний моніторінг та інформаційні технології (КМІТ - 2009)". Донецк, ДонНТУ - 2009. - с. 193-195

Разработка композиционного микропрограммного устройства управления с общей памятью.

Зеленёва И.Я. Кучеренко С.А.

Донецкий национальный технический университетОдним из методов реализации устройства управления цифровой системы является использование модели композиционного микропрограммного устройства управления (КМУУ) [1, 2]. Эти устройства идеально подходят для проектирования с использованием современных СБИС типа FPGA, где имеются средства для реализации произвольной логики и встроенные блоки памяти. В то же время при массовом производстве изделий электронной промышленности по-прежнему широко используются заказные схемы типа ASIC (application-specific integrated circuits). В этом случае для реализации схем устройств управления используются заказные матрицы, основанные на идее распределённой логики. В настоящее время в литературе практически отсутствуют методы, ориентированные на этот базис. В настоящей статье рассматривается метод синтеза КМУУ с общей памятью на заказных матрицах, и анализируются пути уменьшения площади кристалла, занимаемой его логической схемой.

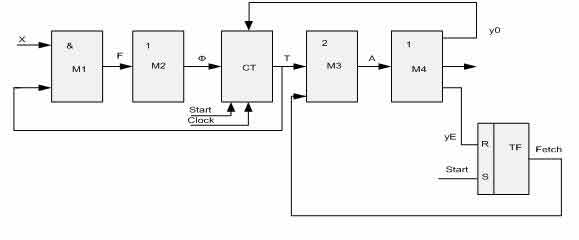

Целью исследования является реализация логической схемы устройства управления на заказных СБИС при интерпретации линейного алгоритма управления.Задачей исследования является разработка синтеза КМУУ с общей памятью, позволяющего уменьшить стоимость логической схемы при реализации заданного алгоритма управления представленного в виде граф-схемы алгоритма (ГСА). При реализации схемы КМУУ U1 на заказных матрицах, предлагаемой в данной работе, схема СС представляется в виде конъюктивной матрицы М1 и дизъюктивной матрицы М2. Управляющая память СМ представляется в виде конъюктивной матрицы М3 и дизъюктивной матрицы М4. (рис.1.)

Рис.1. Матричная реализация КМУУ с общей памятью.

В этой схеме матрица М1 реализует систему термов F={F1,…,FH}, соответствующих строкам таблицы переходов КМУУ. Матрица М2 реализует систему, элементы которой определяют функции возбуждения D-триггера, поступающие на информационные входы СТ. Матрица М3 формирует термы Amпринадлежат множеству A, соответствующие адресам микрокоманд. Матрица М4 формирует функции y0, y₣ и ynпринадлежащие множеству Y. В настоящей работе предлагается метод матричной реализации КМУУ U1:

1. Формирование множества ОЛЦ. Этот этап выполняется по известной методике [1, 2].2. Естественная адресация микрокоманд. Этот этап сводится к последовательной нумерации компонент α=α1*α2*…*αG. Нумерация начинается с нуля, а RА - разрядные двоичные эквиваленты номеров операторных вершин являются адресами соответствующих микрокоманд [1, 2]3. Формирование системы формул перехода. Эта система формируется для выходов ОЛЦ αġ принадлежит множеству C1, где αġ не принадлежит множеству C1, если её выход связан с конечной вершиной ГСА.4. Формирование таблицы переходов КМУУ.5. Формирование содержимого управляемой памяти.6. Реализация схем КМУУ: соединение всех этих матриц и счетчика СТ дает схему КМУУ U1 (cложность каждой из матриц определяется ее площадью в условных единицах).Предложенный метод матричной реализации КМУУ с общей памятью позволяет получить схему, функционально соответствующую тривиальной реализации микропрограммного автомата. Для оптимизации этой схемы можно использовать, как известные методы замены логических условий и кодирования наборов микроопераций, так и адаптировать методы оптимизации КМУУ, ориентированные на FPGA [3, 4].

Литература.

- Баркалов А.А. Микропрограммное устройство управления как композиция автоматов с программируемой и жёсткой логикой. Автоматика и вычислительная техника, 1983, №4.-с.36-41.

- Barkalov A.A., Titarenko L.A. Synthesis of operational and control automate.- Donets’с: Untech, 2005.-25pp.

- Maxfield C. The Design Warriors’s Guide for FPGA.-Amsterdam: Elseveir, 2004.-541 p.

- Smith M. Application – Specific Integrated Circuits. - Boston: Addison - Wesley, 1997.-836 pp.