Глава 16. Цифровой анализ худшей временной ситуации.Перевод с английского: Лещенко С.А.PSpice User's Guide, Product Version 10.0 |

Цифровой расчет времени худшей ситуации

Изготовители электронных компонентов в общем специфицируют параметры компонетов(например, распространение задержек в случае логических устройств) как отказоустойчивость. Они выражены операционный диапазон, либо как распространение вокруг типичной операционной точки. Проектировщик имеет некоторое указание по отклонению времени срабатывания компонента от номинального.

Цифровой анализ худшей ситуации в сравнении с аналоговым анализом худшей ситуации

Цифровое моделирование худшей временной ситуации различно от аналогового анализа худшей ситуации по нескольким причинам. Аналоговый анализ худшей ситуации осуществляется как анализ чувствительности для каждого параметра, который имеет отказоустойчивость, завершенную проектируемым моделированием худшей ситуации с каждым параметром, установленным к его минимальному или максимальному значению. Этот вид анализа основной с любым типом вариации, вызванным любым типом параметра отказоустойчивости, который может изучаться. Но время потребление отдельного моделирования требуется для каждого параметра. Это не всегда приводит истинным результатам худшей ситуации, с момента, когда алгоритм предполагает, что чувствительность монотонна над областью допустимых значений.

Пример временной неоднозначности

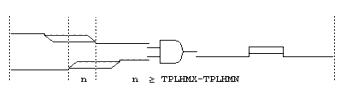

PSpice A/D использует пять состояний сигнала {0,1,R,F,X}, где R и F представляют подъем и спад переходов, соответственно. Любые переходы R или F могут считаться как области неоднозначности. Хотя начальное и конечное состояния известны (пример: R 0 -> 1 переход), точное время перехода не известно, кроме того, что это происходит где-нибудь в пределах области неоднозначности. Область неоднозначности - интервал времени между самым ранним и самым поздним временем перехода, который может произойти.

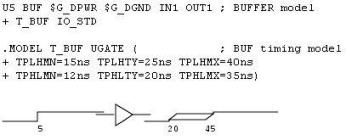

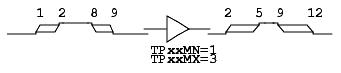

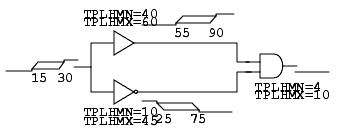

Мгновенный переход 0-1 в 5нс в этом примере соответствует результату на выходе. Согласно спецификации задержки в модели расчета времени выход формируется в MIN на 15нс позже и MAX на 40нс позже. Область неоднозначности для выхода соответствует диапазону с 20 до 45нс (от значений TPLHMN и TPLHMX). Подобные вычисления для перехода 1-0 на входе, используя значения TPHLMN и TPHLMX. Распространение временной неоднозначностиТак как сигналы распространяются по схеме, неоднозначности содействует каждый примитивный элемент, имеющий ненулевую MIN/MAX задержку распространения. Рассмотрим следующий пример, который содержит значения задержки предыдущей модели BUF.

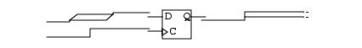

Накопление неоднозначности может иметь неблагоприятные эффекты на свойства схемы. В следующем примере рассматривается неоднозначность на вводе данных к триггеру.

Моделирующее устройство должно предсказать X на выходе, потому что не известно с любой уверенностью, когда данные на входе фактически сделали 0-1 переход. Если кумулятивное наличие неоднозначности в сигнале данных было меньше, то 1 на выходе будет установлена верно. Рисунок 16-4 иллюстрирует случай однозначных изменений данных(установлено перед тем, как синхросигнал сможет выполнить переключение) с неоднозначным синхронизирующим сигналом. Выход Q изменится, но время его перехода неизвестно, так как синхросигнал неоднозначен.

Определение степени риска

Степенью риска называется термин, применимый для ситуаций, когжа ответ устройства не может быть правильно предсказан из-за неопределенности времени прихода сигналов на его входах.

Состояние выхода не изменится(и не должно), так как входы однозначно заданы и время переходов известно. Риск конвергенции

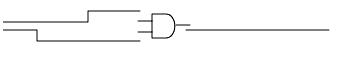

В случаях, когда есть неоднозначность, связанная с переходами сигналов 0-R-1 и 1-F-0, время переходов которых совпадает, не известно, какой из переходов случится первым.

Этот выход (0-R-0) следует рассматривать в качестве возможного одиночного импульса, не дольше, чем продолжительность уровня R. Примечание: Другие виды примитивов, таких как триггеры, может привести к X вместо R-0 или F-1 в ответ на риск конвергенции. Фактический выход устройства может или не может меняться в зависимости от времени перехода на входах. Критический риск

Важно отметить, что спрогнозированный сбой может распространяться по цепи и может привести к неправильной работе. Если сбой от степени риска запирает внутренний элемент (например, триггер или память), или если он приводит к неправильному состоянию, то это называется критическим риском, поскольку это определенно вызывает неправильную работу.

До тех пор, пока сбой будет происходить задолго до переднего фронта синхросигнала, он не будет вызывать проблемы. Риск накопления неоднозначностиВ наихудшем случае простого распространения сигнала по цепи приведет к накоплению неоднозначности по пути между точками синхронизации. Накопление неоднозначности показано на рис 16-8.

Подъем и спад переходов на входе имеет 1нс неоднозначность. Задержка характеристики буферного элемента показывает, что дополнительные 2нс неоднозначности добавляются к каждой стороне, пока они распространяются через элемент. В результате продолжительность стабильного состояния в «1» уменьшилась за счет накопления неоднозначности. Рисунок 16-9 показывает эффект дополнительной накапливающей неоднозначности.

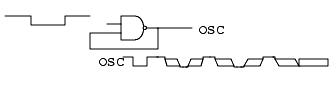

Результат X прогнозируется здесь, потому что неоднозначность переднего фронта распространяется через устройство, увеличилось до точки, где она будет перекрывать неоднозначность на спаде по заднему фронту. В частности, подъем на переднем фронте должен происходить между 3нс и 12нс, но, последующий спад заднего фронта со входа прогнозирует, что выход начинает падать на 10нс. Такая ситуация называется риском накопления неоднозначности. Еще одной причиной риска накопления неоднозначности предполагает схемы с асинхронной обратной связью. Моделирование таких схем при наихудших ситуациях по времени дает слишком пессимистический результат из-за неограниченного накопления неоднозначности в отношении обратной связи. Простой пример этого эффекта показан на рисунке 16-10.

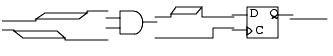

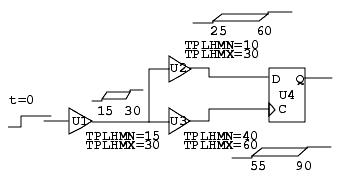

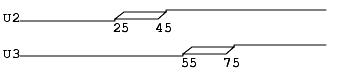

Из-за накопления неоднозначности в петле выходной сигнал в конечном итоге станет X, потому что неоднозначность роста и спада перекроют значения 0-1. Если этот сигнал будет синхронизирован для другой схемы, то эффекты фазового сдвига могут быть проигнорированы. Риск реконвергенцииPSpice A / D распознает ситуации, когда сигналы имеют общую реконвергенцию на входах одного устройства. На рисунке 16-11, относительное соотношение времени между двумя путями (U2, U3) имеет важное значение.

Учитывая задержку указанных значений невозможно для синхросигнала измениться до ввода данных, поскольку задержка MAX пути U2 меньше, чем задержка MIN пути U3. Иными словами, совпадение этих двух регионов неоднозначности не может на самом деле произойти. PSpice A / D распознает такую ситуацию и не производит слишком пессимистический результат запирания состояния X на Q-выводе U4. Эти факторы из 15 нс общей неоднозначности объясняются на U1 с U2 и U3 сигналов (см. рис 16-12).

Результат на рисунке 16-12 не представляет, что фактически распространяется на U2 и U3, но расчет для определения того, что U2 должен быть стабильным в момент прихода U3 может измениться. Вот почему уровень X не должно быть установлен. В случае, если учет общей неоднозначности не устраняет защелку X, то ситуация называется риском реконвергенции. Это аналогично риску конвергенции с неоднозначностью сигнала, имеющего общее происхождение. Для использования цифрового наихудшего моделирования эффективно, необходимо найти области на схеме, где временные интервалы переключения сигналов наиболее критичны и использовать ограничения проверок, где это уместно. Эти устройства выявления конкретных временных нарушений, принимая во внимание фактические неоднозначности сигнала (в результате элементов MIN / MAX характеристики задержки). Наиболее распространенные вопросы, вызывающие интерес, включают в себя:

Сигнал неоднозначности, который сходится (или расходится) по проводной сети или шинам с нескольких драйверов, также могут приводить к рискам по аналогии с поведением логических вентилей. В таких случаях, PSpice A / D управляет любой общей неоднозначностью до сообщивших о наличии опасных условий.

Подавление сбоя в связи с инерционной задержкой

Распространение сигнала через цифровые примитивы выполняется моделирующим субъектом при условии ограничений, таких как примитив функции, значения задержек параметра и частоты использованного стимула. Эти ограничения применяются как в рамках нормального, хорошо работающего стимула, и стимула, который представляет степень риска.

Однако, когда продолжительность конфликтующих входов стимула меньше инерционной задержки устройства, в результате X автоматически подавляет симулятор потому, что это слишком пессимистически (рис. 16.14).

При анализе случаев реконвергенции разветвления (там, где общая неоднозначность распознается), вполне возможно, что противоречивые сигнал неоднозначности может по-прежнему перекрывать на входе примитива, даже после управления по общности. В таких случаях, когда количество перекрытий меньше, чем инерционные задержки устройства, предсказания сбоев также подавляются симулятором (рис. 16-15).

В этом случае на выходе все еще 15нс общая неоднозначность, по-прежнему в 5нс перекрытия конфликтующих состояний. Сбой подавлен, однако, поскольку 5нс меньше TPLHMX-TPLHMN (расчетное значение инерционной задержкой элемента AND, 6нс). Copyright © 2003, Cadence Design Systems, Inc. All rights reserved. |