ДонНТУ | Портал магистров ДонНТУ | RU | UA | EN

Масякін Євген Анатолійович

Масякін Євген Анатолійович

Факультет комп'ютерних наук і технологій (КНТ)

Кафедра комп'ютерної інженерії (КІ)

Спеціальність «Комп'ютерні системи та мережі» (КС)

«Розробка та дослідження методів і структур апаратного генерування аналогових тестів на базі FPGA»

Науковий керівник: к.т.н., доцент кафедри КІ Зінченко Юрій Євгенович

Автобіографія | Реферат

Розробка та дослідження методів і структур апаратного генерування аналогових тестів на базі FPGA

Актуальність і обгрунтування вибору теми

Сучасний світ важко уявити без електроніки. Кожен день, годину, хвилину створюються нові пристрої, прилади, системи, які роблять життя людини більш комфортним, безпечним, дозволяють йому відкривати нові горизонти наукових знань. Сідаючи за кермо сучасного автомобіля, людина взаємодіє з десятками і сотнями електронних систем, різного рівня складності: від найпростіших датчиків рівня мастила до автоматизованих систем паркування автомобіля. Цифроаналогова техніка, як правило, грає роль посередника між навколишнім середовищем і цифровими системами. Винятком є військово-промисловий комплекс, де широко використовуються подібні пристрої з огляду на їх високу надійность і довговічность порівняно з виключно цифровими системами. У свою чергу повсюдне використання техніки диктує все більш і більш жорсткі вимоги до її надійності, тестованості, що викликає необхідність розробки нових структур і методів синтезу і генерації, в тому числі і аналогових, тестів. [1]

Цілі і завдання дослідження

Метою роботи є розробка та дослідження високоефективних структур і методів апаратного генерування аналогових тестів з використанням сучасних можливостей FPGA-технологій в області цифрової обробки сигналів.

Завдання, які вирішуються в ході виконання даної роботи:

- аналіз існуючих систем генерування аналогових тестів;

- розробка методу і структури генерації аналогових тестів на базі ЦОС і ПЛІС;

- розробка програмно-апаратних засобів на базі ПЛІС;

- проведення експерементальних досліджень.

Очікувана наукова новизна

Можлива наукова новизна полягає в розробці методів і структур генерування аналогових тестів на базі ЦОС, які дадуть більш ефективне рішення цієї проблем при реалізації з використанням ПЛІС. Планується, що подібна структура дозволить забезпечити високу ефективність, компактність, а також низьку вартість пристроїв, що генерують аналогові тестові послідовності.

Огляд існуючих розробок

Головним інструментом інженера - діагноста на сьогоднішній день є автоматизована система діагностики (АСД). Їх провідними виробниками стали такі компанії як Teradyne, Agilent, World Test Systems, DMT та інші. Проте, переважна більшість подібних систем призначені для тестування цифрових пристроїв, і не дозволяють в повній мірі автоматизувати процес побудови тесту для аналогово-цифрових схем. У свою чергу побудова функціональних аналогових тестів потребує високої продуктивності, швидкості генератора аналогової тестової послідовності, що послужило основою для вибору саме FPGA-технології для реалізації даної роботи.

Рівні подання аналогово-цифрових схем при генерування тестів

Аналогову схему можна представити наступними рівнями абстракції.

За способом представлення АЦ-пристрої розглядають:

- Структурний рівень - представлення АЦ-пристрої сукупністю компонент і зв'язків між ними;

- Поведінковий або функціональний рівень - представлення АЦ-пристрою вхід-вихідною залежністю: системою диференціальних рівнянь, графом, алгоритмом, тощо.

За ступенем деталізації розрізняють:

- транзисторний рівень - структурно схема представляється за допомогою списку компонентів і списку з'єднань між ними, які доповнюються детальними моделями компонентів. Поведінкове уявлення схеми на цьому рівні описується системою нелінійних диференціальних рівнянь в приватних похідних;

- структурно-функціональний рівень - структурним поданням схеми на цьому рівні є сигнальний орієнтований граф (СОГ), який графічно відображає ідеалізовану систему рівнянь. У свою чергу поведінкове подання на цьому рівні описується передатною функцією схеми.

Перевагами функціонального рівня абстракції є зручність моделювання, обчислювальна ефективність і відсутність необхідності моделювати несправності всередині компонентів схеми. У той же час структурний рівень абстракції дозволяє ефективно моделювати реальні дефекти аналогових компонент.

Виділяють структурні та функціональні аналогові тести. Основна різниця між ними полягає в походженні несправностей та процедурі моделювання. Функціональне тестування часто припускає, що несправні компоненти і при цьому генерується список несправностей, який включає катастрофічні, і параметричні несправності.Структурний тестування використовує статистику виробничих дефектів. [2]

Аналогові схеми мають складні залежності між вхідними і вихідними сигналами. Багато аналогових схем є нелінійними системами (наприклад, МОП-транзистор, що використовується як підсилювач). Значення параметрів схеми змінюються в широких межах навіть в справних схемах. Детерміновані моделі не є ефективними для аналогових схем, тому сигнали визначаються номінальними значеннями разом з прийнятними діапазонами їх змін, які визначаються шляхом моделювання процесу вимірювання похибок і коливання процесу виробництва ІС. Статистичний розподіл аналогових несправностей зазвичай не відомий із достатньою точністю, щоб безпомилково передбачити покриття несправностей тестової послідовністю. Деякі звіти свідчать про те, що аналогові схеми з катастрофічними несправностями не виявляються стандартними виробничими тестами. [2]

Використання DSP-процесорів в сучасних автоматизованих системах діагностики

В даний час практично всі аналогові схеми тестуються з використанням автоматизованих систем діагностики (АСД), побудованих на базі DSP. Дані АСД замість використання реальних аналогових вимірювальних інструментів, виконують їх емуляцію на основі швидкого перетворення Фур'є (ШПФ) і дискретного перетворення Фур'є (ДПФ), для того щоб зменшити помилку вимірювання і усунути небажаний час встановлення сигналу при тестуванні.

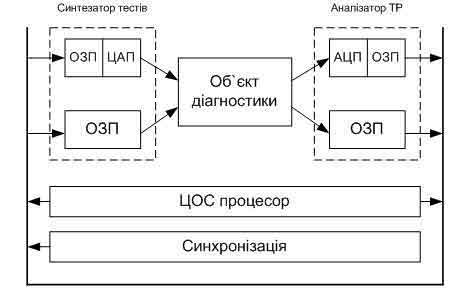

На рисунку 1 представлена традиційна аналогова АСД. Варто звернути увагу, що вона не має засобів синхронізації між блоками генерації тесту і аналізу реакцій. [2]

На рисунку 2 представлена АСД на базі DSP, яка має відповідну синхронизацію, и складаються із АЦП, ЦАП, пам`яті для збереження тестів і реакцій, DSP, що керується програмно. [2]

DSP може емулювати широкий набір вимірювальних інструментів. Інструментами тепер є підпрограми, які обробляють вектора чисельних значень.Вектор може являти собою набір вибірок сигналу, частотний спектр, тощо. Спеціаліст з тестування створює набір векторів у вигляді тестових сигналів. Синтезатор сигналів подає ці вектора на ЦАП, вихід якого з'єднаний з відновлюючим фільтром для отримання безперервного сигналу з обмеженою смугою пропущення. [2]

Отриманий сигнал подається на пристрій, що випробовується, з якого знімаються реакції. аналогових сигналів виконує оцифровування знятих реакцій з використанням високошвидкісного АЦП і зберігає вибірки в ОЗУ. Якщо у якості випробуваного пристрою виступає аналогово-цифрова схема, сигнали з виходів цифрової частини записуються у вхідну пам'ять, а тести для цифрової частини подаються на об'єкт діагностики (ОД) з вихідної пам'яті. [2]

На рисунку 3 зображений процес синтезу аналогового сигналу, а на рисунку 4 - процес оцифровування.

Переваги АСД на базі DSP-ядер

- Точність. АСД на базі DSP практично завжди володіють великою точністю, ніж аналогові інструменти, так як помилка в наборі вибірок сигналу значно менше після цифрової обробки, чим помилка індивідуальної вибірки. Наведення, шум і відхилення сигналів значно скорочуються в DSP тестерах, так як аналоговий сигнал оцифровується на самій ранній стадії. Старіння компонентів тестера і температурні ефекти викликають значно менше проблем, так як цифрові компоненти краще зберігають свої характеристики, ніж аналогові.

- Швидкість. DSP тестер може отримати набір вибірок від ОД за один період вибірки, а далі використовуючи ДПФ і БПФ виконати над ним різні вимірювання шляхом емуляції інструментів. Для виконання кратних вимірювань DSP тестер значно ефективніший, ніж аналоговий, якому треба виконувати кратні вимірювання. Також в DSP тестері відсутні тимчасові витрати на встановлення сигналу у фільтрі, які присутні в аналоговому тестері.

- Простота використання. Так як тестер цифровий, то легко повторювати тестування, виконувати настройку і зберігати виконані настройки.

- Більше вимірювальної інформації. DSP тестер надає додаткову інформацію разом з вимірюваним параметром, наприклад, піковий детектор повідомляє не тільки про значення піку, але і про розташування піку в часі.

- Розмір і потужність. АСД загального призначення на базі DSP менше, дешевше і вимагає меншої потужності, ніж відповідна аналогова АСД. [2]

Недоліки АСД на базі DSP

- Вони дороги, хоча ціна знижується завдяки використанню СБІС. Розрядність, необхідна для досягнення прийнятної точності, і вимоги по смузі пропускання роблять DSP дорогими.

- Коли необхідно виконувати тільки одне вимірювання, чисто аналогові тестери дешевше. DSP володіють перевагою тільки при необхідності багатьох вимірювань.

- Гнучкість інструментарію є проблемою для недосвідченого оператора, так як необхідно знати теорію їх використання.

- Спеціаліст з тестування повинен знати фізичні і математичні принципи, які лежать за кожним тестом і джерелом помилок. [2]

Переваги використання ПЛІС для реалізації DSP-орієнтованих пристроїв

При розробці систем цифрової обробки сигналів традиційним є підхід, при якому використовуються DSP-процесори загального призначення, а необхідні специфічні алгоритми обробки реалізуються програмно (в основному на мові С). Проте останнім часом все частіше можна спостерігати застосування апаратних методів, заснованих на використанні програмованих логічних інтегральних схем (ПЛІС) з FPGA-архітектурою як препроцесора та співпроцесорів. Такий підхід дозволяє отримати суттєвий приріст продуктивності, знизити вартість і споживану потужність системи. Проте його повсюдному поширенню перешкоджає те, що розробники DSP-систем не завжди мають досвід проектування на базі FPGA. Архітектура FPGA володіє великою гнучкістю, на її базі можна реалізовувати розпаралелювання операцій, що дозволяє істотно підвищити продуктивність всієї DSP-системи. [7]

Найбільш типові приклади такого використання FPGA - реалізація швидкого перетворення Фур'є, цифрового перетворення з пониженням частоти, блоків прямого виправлення помилок. Мікросхеми сімейств FPGA Virtex-4 і Virtex-5 фірми Xilinx включають до 512 паралельних помножувачем, що працюють на частоті понад 500 МГц. При побудові DSP-системи операції, що вимагають високошвидкісної обробки даних у паралельному режимі, реалізуються на базі FPGA, а операції високошвидкісної послідовної обробки - за допомогою DSP-процесорів. Такий розподіл ресурсів системи дозволяє досягти оптимального співвідношення ціна-якість і знизити енергоспоживання.

Додаткові можливості для розпаралелювання операцій обробки сигналу, оптимального розподілу функцій у системі з співпроцесорів на базі FPGA забезпечує наявність вбудованих в FPGA процесорів. Мікропроцесорне ядро MicroBlaze (soft processor, за термінологією Xilinx) передбачає можливість реалізації його на ПЛІС різних серій і часто виявляється зручним для організації управління системою. Більш продуктивний процесор PowerPC реалізований на кристалі у вигляді окремого апаратного блоку. Гнучкість архітектури ПЛІС FPGA дозволяє організувати прискорення і розпаралелювання операцій різними способами. Наприклад, блок на основі FPGA може бути безпосередньо включений у тракт обробки даних DSP-системи. Інший можливий варіант - реалізація апаратного прискорювача на базі одного із вбудованих процесорів. Розподіл функцій DSP-системи за наявними апаратними ресурсами, при якому для системи в цілому забезпечується оптимальне співвідношення ціна/якість. [10]

Поточні і плановані результати:

На даний момент були отримані наступні результати:

- виконаний огляд існуючих методів генерування аналогових тестів;

- в якості елементної бази для реалізації програмно-апаратного комплексу генератора аналогових тестових впливів був обрана відлагоджувальна FPGA-плата Xilinx Spartan 3AN;

- проведені дослідження та розроблено експериментальний пристрій генерування аналогових тестів.

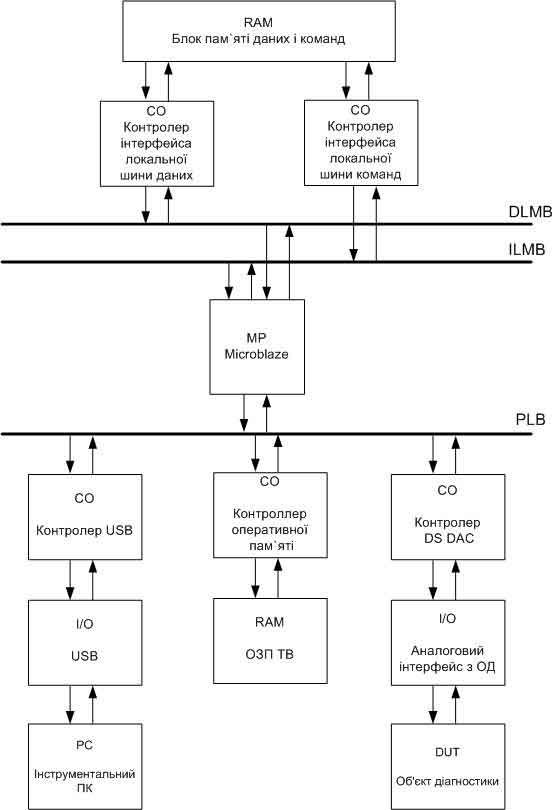

- МП Microblaze — soft-процесорне RISC ядро, розроблене компанією Xilinx для використання в FPGA. MicroBlaze реалізується за допомогою стандартної логіки і блоків пам'яті ПЛІС. У розробленій структурі даний елемент виконує роль арбітра.

- Шина PLB — основна шина введення-виведення. Забезпечує взаємодію між процесорним ядром і периферійними пристроями.

- iLMB, dLMB — локальна шина даних і локальна шина команд використовується для доступу до внутрішньої пам'яті BRAM. Використання даних шин дозволяє знизити навантаження на інші шини.

- Інтерфейс USB обраний через його поширеності, мініатюрності та доступності. Практично всі сучасні персональні комп'ютери, які випускаються зараз, оснащені цим інтерфейсом.

- Контролер оперативної пам'яті-призначений для організації роботи з зовнішньої RAM.

- Зовнішня RAM-пам'ять використовується для зберігання тестових векторів і тестових реакцій.

- PC-і клієнтська програма встановлена на нім служить для завдання параметрів діагностики і відображення результатів.

Апробація

Проміжні результати роботи доповідалися на V ювілейній міжнародній науково-технічній конференції студентів, аспірантів і молодих вчених «Інформатика та комп'ютерні технології» 24-26 листопада 2009

Висновки

Таким чином, існуючі системи автоматичного генерування аналогових тестів не завжди є ефективними, а повноцінних автоматизованих систем діагностики для аналогово-цифрових плат ще не створено, тому завдання розробки методів автоматичного генерування аналогових тестів є актуальним.

Надалі будуть розроблені методи і структура на базі ЦОС, яка дасть більш ефективне рішення проблеми генерування аналогових тестів на ПЛІС.

Важливе зауваження

При написанні даного реферату магістерська робота ще не завершена. Остаточне завершення: грудень 2010 Повний текст роботи та матеріали по темі можуть бути отримані у автора або його керівника після зазначеної дати.Перелік використаної літератури:

- Давыдов П.С. Техническая диагностика радиоэлектронных устройств и систем / Давыдов П.С. // М.: Радио и связь, 1988. — 256 с.

- Agrawal V.D Essentials of electronic testing for digital, memory and mixed-signal VLSI circuits / Agrawal V.D, Bushnell M. L. // Boston: Kluwer Academic Publishers, — 2000, 650 p

- Bapiraju Vinnakota. Analog and mixed-signal test / Bapiraju Vinnakota // Prentice Hall PTR, 1998. — 261p.

- Prithviraj Kabisatpathy Fault Diagnosis of Analog Integrated Circuits / Prithviraj Kabisatpathy, Alok Barua, Satyabroto Sinha // Springer, 2005.

- A. Birolini, Quality Reliability of Technical Systems / A. Birolini // Springer-Verlag, Berlin, 1994.

- F.J. Langley, Printed Circuits Handbook / F.J. Langley // McGraw-Hill Publishing Company, Inc., New York, pp.21.1-21.26

- Перекрест А.А. Преимущества использования сопроцессоров на базе ПЛИС FPGA в системах цифровой обработки сигналов [Электронный ресурс] — Режим доступа: http://www.electronics.ru/issue/2006/6/18

- J. Galiay. Physical versus logical fault models MOS LSI circuits: Impact on their testability / J. Galiay //, IEEE Transactions on Computers, Vol. C-29, pp. 527-531, June 1980.

- Рувинова Э. Внутрисхемный контроль жив и будет жить // Рувинова Э./ Электроника: Наука, Технология, Бизнес, № 5 - 2001г.

- Ридико Л. DDS: прямой цифровой синтез частоты [Электронный ресурс] — Режим доступа: http://ru3ga.qrz.ru/UZLY/dds.htm