Розробка мультипроцесорної системи у Platform Studio

Vasanth Asokan

автор перекладу: Рудченко І.В.

Джерело : http://www.xilinx.com/support/documentation/white_papers/wp262.pdf

Введення

Вимоги до обчислювальної потужності зростають у швидкому темпі та архітектори систем знаходять вихід у багатопроцесорних обчислювальних комплексах вирішуючи проблему зростаючої складності уніпроцесорних систем. З приходом FPGA висока логічна щільність та продуктивність зробилися реальними. The Xilinx Platform Studio (XPS) та

Embedded Development Kit (EDK) - це всеосяжне вирішення для дизайну вбудованих програмованих систем. Інструменти Platform Studio та IP роблять легким дизайн потужних CMP систем. Вони впроводжують гнучкість для створення унікально збудованих, індивідуальних рішень на логіці FPGA, які матимуть найкраще співвідношення потужності обчислювальних ресурсів та їх вартості.

Дизайн

Топологія моделі, яку потрібно використовувати на мікропроцесорній системі, диктується та обмежена різноманітними вимогами фінальної програми. Обмеження можуть бути висунуті програмними або апаратними вимогами. Використовуючи великий простір дизайну FPGA логіки, інструменти та IP, забезпечує необхідну гнучкість системного дизайнеру.

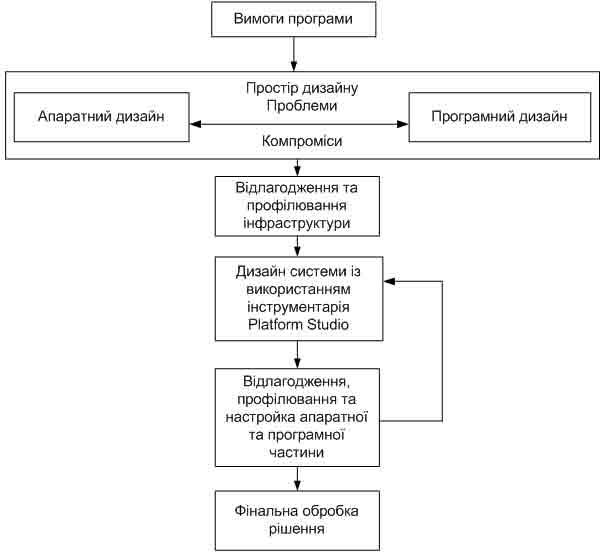

Схематичний дизайн приведено на рис.1. Дизайнер враховує вимоги програмного додатку, вживає різні обмеження та робить дизайн рішення з деякою програмною та апаратною архітектурою. Після чого він створює прототип та завантажує його на FPGA використовуючи інструменти Platform Studio. Після цих дій виконується кваліфікація та удосконалення рішення, через численні ітерації та верифікацію. Компроміси та переробка дизайну застосовуються на першому етапі. Могутність FPGA та інструментів Platform Studio роблять цей процес доволі швидким. Розробка оригинального дизайну вимагає кілька годин, але створення вимог займає кілька хвилин - для усієї апаратної частини, згенерованої для реконфігуруємої платформи. Додавання, або усування процесора з платформи є таким легким, як натиснення кількох клавіш на графічному інтерфейсі. Могутнє моделювання, відлагодження, архітектура профілювання, пропоновані Platform Studio допомогають досліджувати простір дизайну.

|

Рисунок 1 - Схематичний дизайн

Передумова

Вбудований інструментарій Xilinx для розробки (EDK) - це інтегроване програмне вирішення для дизайну вбудованих мультипроцесорних систем. Цей преконфігурований інструментарій містить у собі комплект Platform Studio також як і IP та документацію необхідну для дизайну Xilinx Platform FPGA із вбудованими PowerPC апаратними ядрами процесорів та/або MicroBlaze програмними ядрами процесорів.

Ядро процесора MicroBlaze є 32-бітним із архітектурою Harvard RISC із багатими інструкціями оптимізований для вбудованих додатків. Цей процесор є програмним ядром, що означає що він розроблений із використанням примітивів загальної логіки, ніж відокремлений блок у FPGA. Рішення MicroBlaze дає користувачу контроль над особливостями такими як: розмір кешу, інтерфейси, виконоючі одиниці такі як одиниця апаратна плаваючою комою. Можливість конфігуровання дозволяє користувачу знаходити компромісні риси для розміру для того, щоб досягнути необхідної продуктивності для кінцевого програмного додатку витрачаючи якнайменьше коштів. Особливістю MicroBlaze також є підтримка MMU, таким чином він підтримує різні RTOS імплементації.

Дизайн апаратної частини

Кількість топологій із мультипроцесорною системою у них є доволі великою. Не тільки кількість процесорів може бути різною, але й є велика кількість можливостей відносно до їх розташування та функцій. Присутність або відсутність різних елементів, таких як зовнішня пам’ять та периферія також можуть відкрити різні опції архітектури системи.

Парадігма шин, яка використовується кожною процесорною підсистемою формує ядро будь-якої архітектури системи. Уся периферія конкретного процесору підключається до первинної системної шини PLBv46. Окремо від шини PLBv46 кожний процесор має можливість підключення до локальної пам’яті на чипі BRAM через локальну пам’ять інтерфейсів локальних шин. У випадку PPC405 локальна шина пам’яті називається On-chip Memory Bus (OCM) (шина пам’яті на чипі), де у випадку the

MicroBlaze вона називається Local Memory Bus (LMB) (локальна шина пам’яті).

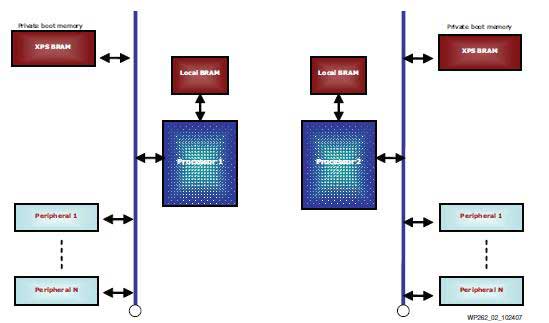

На рис. 2 зображено дуже основна, повністю незалежна двохпроцесорна системна архітектура із індивідуальною підсистемою обробки за парадігмою шин.

|

Рисунок 2 - Незалежна двохпроцесорна архітектура

Немає апаратних компонент пов’язуючих індивідуальні підсистеми, отже процесори не можуть спілкуватися під час роботи. У загальній архітектурі приведеній вище, користувач може еквівалентно підставити PPC405 або MicroBlaze на місці кожного з процесорів. Такі незалежні системи обробки є тривіальним переліком багатьох однопроцесорних систем зкомпонованих разом у одній FPGA, але можуть бути користними для розділення великого набору фунцій на процесори. На рис. 2 зображена більш загальна двохпроцесорна архітектура, де два процесори можуть зв’язуватися один з одним, координувати та виконувати конкретні функції.

|

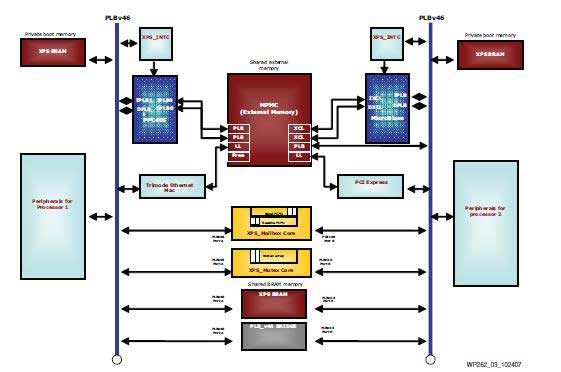

Рисунок 3 - Загальна двохпроцесорна архітектура

Ключові концепти цієї архітектури:

- архітектура є розширенням повністю незалежної оброблюючої архітектури, яке поєднує компоненти двох процесорів.

Розподілені компоненти дозволяють двом процесорам спілкуватися різними засобами.

-- цей приклад навмисно показує PPC405, як перший процесор, а MicroBlaze, як другий, щоб зобразити специфічні характеристики кожногог процесору. Проте будь який процесор може бути еквівалентно замінений іншим із мінімальною адаптацією, таким чином впроводжуючи велику гнучкість у виборі процесору.

- розподілені компоненти мулти або дво-портовані за конструкцією. Мульти-портована структура компонент дозволяє кожній PLBv46 системній шині бути незалежною від інших у рамках статичного та динамічного завантаження. Ізолюючи кожну процесорну підсистему гарантується, що системна шина не заблокується для процесору або периферії для поточної транзакції, яка виконується на іншому процесорі. Уся мультипортована периферія передає доступ на різні порти внутрішньо.

- Ключова периферія із загальним доступом - це зовнішній контроллер пам’яті MPMC. MPMC - це унікальний контроллер пам’яті, що підтримується Platform Studio, яка пропонує багато різних інтерфейсів (через порти) до тієї ж зовнішньої пам’яті. Окремо від PLBv46, MPMC типи портів включають високу продуктивність MicroBlaze Xilinx CacheLink (XCL) інтерфейсів (Інструкції XCL та Data XCL) також, як і точка-до-точки інтерфейси PowerPC405 (IPLB0/DPLB0) посилань на кеш. Ця топологія дозволяє MicroBlaze та PowerPC процесорам мати доступ до зовнішньої пам’яті із мінімальною затримкою та високу пропускну здатність у той самий час. MPMC надає до 8ми портів, таким чином дозволяючи під’єднання від трьох до чотирьох процесорів до однієї зовнішньої пам’яті.

- також можливо розподіляти BRAM пам’ять між процесорами. Розподілення пам’яті на чипі BRAM може надавати доволі швидкий варіант для передачі даних розміром у кілобайт між процесорами. У деяких випадках детерміністичний доступ до BRAM є дужє важливим. Це може бути досягнуто з’єднуючи BRAM пам’ять із інтерфейсом локальної пам’яті кожного процесору (замість інтерфейсу PLBv46 на рис. 2).

- Окремо від розподіленої пам’яті існують два інших ядра the XPS Mailbox та XPS

Mutex, які впроводжують інші прості форми комунікації.

- На рис. 3 показано міст від PLBv46 до PLBv46 під’єднуючий шину другого до шини першого. Це може запросити розподілення периферії, що не є мультипортованою за конструкцією. Наприклад, деякі системи можливо запросять розподілення UART, SPI та I2C периферії. Така ситуація вимагає під’єднання периферії до конкретної системної шини процесору та будування мосту від інших системних шин процесорів.

На рис. 3 ображена рекомендована архітектура мультипроцесорної системи, але й деякі інші варіанти доступні для створення такої системи. Наприклад, у системи, де ключовим є логічна зона та використання ресурсів - усі процесори можуть бути розташовані на одній системній шині. У той час, як це робить систему менше детермінованою та збільшує завантаження на шині під час роботи, це пропонує економію на місці, ліквідуючи нову системну шину із необхідністю багатьох портів на IP. Також можливі інші похідні архітектури, такі як мати потужний процесор на окремій системній шині та багато мало продуктивних процесорів на розподіленій системній шині.

Ієрархічні топології також можуть бути створені шляхом поєднання підсистем обробки через кілька рівнів мостів. Вичерпний список усіх таких топологій за межами цього документу.