|

Автореферат

Введение и актуальность

В настоящее время практически не существует систем, обеспечивающих подобно цифровому тестированию автоматическое построение тестов для аналоговых и аналого-цифровых (АЦ) устройств по их структурному или функциональному описанию. Существующие системы призваны лишь помогать диагносту высокой квалификации, так что тесты строятся практически вручную исходя из глубоких знаний диагноста о схемотехнике и функциях объекта диагностики (ОД). Проблема усугубляется также тем, что тесты, построенные вручную, неэффективны для промышленного тестирования АЦ-устройств на доступном тестовом оборудовании и для адаптации к этому оборудованию их приходится строить заново, опять же вручную. [2]

Традиционный подход построения тестов для АЦ-устройств базируется на функциональном тестировании на основе спецификаций ОД. При этом обычно диагност предполагает, что в процессе диагностики будет доступна разнообразная контрольно-диагностическая аппаратура (КДА). Большое число спецификаций, высокая стоимость КДА и требования высокой квалификации, предъявляемые к персоналу, а также процесс диагностирования, сопряженный с большим числом ручных операций, приводят к низкой степени автоматизации и в конечном счете к высокой дороговизне традиционного подхода. Повышение сложности современных АЦ-устройств, вызванное повышением степени интеграции АЦ-ИС и сложностью взаимодействия их аналоговых и цифровых узлов наряду с уменьшением соотношения этой сложности к общему числу выводов АЦ-ИС, существенно усугубляет эту проблему и заставляет ученых и практиков-диагностов искать новые подходы тестирования АЦ-устройств.

Таким образом, видим, что задача поиска и устранения неисправностей, аналоговых и АЦ устройств с каждым днем становится все более востребованной. Поэтому тема данной магистерской работы, направленная на разработку и исследование методов и структур аппаратного анализа аналоговых тестовых реакций на базе FPGA, как одной из задач аналогового тестирования, является актуальной.[2]

Цель и задачи магистерской работы

Целью работы является автоматизация процесса анализа тестовых реакций аналоговых устройств. Для достижения поставленной цели в работе ставятся следующие задачи:

• исследование существующих методов и систем диагностирования АЦ-устройств и анализа их тестовых реакций в частности;

• разработка методов и FPGA-структур анализа аналоговых тестовых реакций;

• разработка и исследование экспериментальной подсистемы анализа аналоговых тестовых реакций на базе FPGA.

Предполагаемая научная новизна

Предполагаемая научная новизна заключается в разработке метода и архитектуры анализатора аналоговых тестовых последовательностей на базе FPGA с целью обеспечения возможности тестирования быстродействующих АЦ-устройств. Ожидается что разработанная подсистема будет обеспечивать высокое быстродействие, компактность, гибкость и универсальность, а также низкую стоимость. [9]

Виды аналогового тестирования

Рассмотрим основные виды тестирования аналоговых схем.[1]

Каждый класс аналоговой схемы (АЦП, ЦАП, фильтр, цепь фазовой синхронизации и т. д.) имеет свой собственный набор спецификаций. Для каждого из них уже существуют приемлемые функциональные тесты для испытания опытного образца и минимизированные по длине тестовые наборы для испытаний серийной продукции. Но не существует универсальных тестов для проверки характеристик схем.

Выделяют структурные и функциональные аналоговые тесты. Основная разница между ними состоит в происхождении неисправностей и процедуре моделирования.

Функциональный тест часто предполагает, что компоненты являются неисправными и генерирует список неисправностей, используя катастрофические и параметрические неисправности. При структурном тестировании используется статистика производственных неисправностей.[1]

Тестирование аналоговых схем по назначению можно разделить на следующие три категории:

• снятие характеристик схемы для определения удовлетворяет ли она спецификации;

• диагностика для определения причины неисправности, когда схема не проходит тест;

• заводские испытания, проводимые для проверки больших объемов линейных и аналогово-цифровых схем.

В свою очередь тесты подразделяются на следующие виды[1]:

• тесты, основанные на спецификации — генерируются непосредственно из спецификации схемы, без использования моделей аналоговых неисправностей. Этот подход легко адаптируется к широкому спектру схем. Однако при использовании большого количества спецификаций тестирование становится достаточно дорогим. Тестовая последовательность может быть сокращена путем выявления зависимостей между спецификациями и отбрасыванием ненужных тестов.

• структурные тесты, построенные с использованием моделей неисправностей — применяется для выявления определенного вида моделируемых неисправностей. Это позволяет разбить набор аналоговых тестов на группы по степени покрытия неисправностей, и таким образом тестовый набор может быть ранжирован. Это дает возможность сократить длину тестовой последовательности благодаря тому, что тест, который покрывает неисправности уже обнаруженные предыдущими тестами, может быть отброшен.

Сложности при тестировании аналоговых сигналов

При тестировании и выявлении неисправностей схем возникают некоторые сложности, связанные с технологическим процессом, ошибками измерения и т.д. Ниже приведены основные из них:

1. Сложность моделирования неисправностей

Аналоговые схемы имеют сложные отношения между входными и выходными сигналами. Многие аналоговые схемы являются нелинейными системами, например, МОП-транзистор, используемый как усилитель. Значения параметров схемы отличаются друг от друга даже в хороших схемах. Использование детерминированных моделей неэффективно для аналоговых схем.[6] Таким образом, сигнал принимает номинальное значение и выделяется диапазон допустимых отклонений от номинального значения. Моделирование и измерение неточности и погрешности при проектировании интегральных схем определяется допустимым отклонением значения сигнала. Наконец, статистическое распределение аналоговых неисправностей, как правило, не известно с достаточной точностью, чтобы точно определить неисправность покрытий из тестового набора. Существует возможность того, что аналоговые схемы, содержащие катастрофические неисправности пройдут производственное тестирование.[1]

2. Ошибки моделирования

Ожидаемые значения сигнала аналоговой схемы рассчитываются на основе моделирования, точность которого ограничена точностью численных значений, используемых в алгоритме моделирования, также моделирование предполагает допущения, касающиеся точности внешних аналоговых устройств. Кроме того, процесс моделирования приводит к получению лучших результатов по установлению диапазона различных значений.[1]

3. Погрешности измерений при тестировании

Ошибки измерений при тестировании аналоговых схем возникает из-за смещения аналогового сигнала, влияния нагрузки измерительного зонда на поведение аналоговых схем, а также сопротивления зонда.[1] Кроме того, случайный шум является проблемой, поэтому аналоговые испытательные устройства ограничены в пропускной способности и точности измерений. Для аналогово-цифровых микросхем пересылка значений внутренних аналоговых сигналов к выходным портам может изменить сигнал и работу схемы в целом. Емкостные связи между высокочастотными цифровыми сигналами и аналоговыми сигналами вызывают дополнительные помехи аналоговой схемы. Аналоговое тестирование должно создавать разницу на аналоговом выходе между исправными и неисправными устройствами, которая лежит за пределами погрешности тестового прибора и автоматического испытательного оборудования.[6]

4. Проблемы доступа при моделировании

Моделируемая схема представляет собой набор сложных и недоступных внутренних компонент, что ограничивает использование обычного аналогового автоматического испытательного оборудования.

5. Погрешности производственного процесса

Различные параметры устройств в больших объемах производства интегральных схем подчиняются статистическим законам распределения. Эта разновидность процесса может в значительной степени влиять на значения параметров компонент.[1] Существуют способы аналогового моделирование и конфигурирования схем, чтобы свести к минимуму влияние температуры и градиента диффузии на компоновку схем. Наличие параметрических погрешностей влияет на изменение стоимости компонент. Однако литература по аналоговому тестированию также описывает изменение выходных параметров, например изменение коэффициента усиления усилителя. Оба вида правильны, а смысл будет понятен из контекста. Для аналоговых устройств множественные параметрические неисправности (с участием нескольких незначительных изменений компонент) тем больше, чем больше величина одной неисправности или критической неисправности.

6. Информационный поток

Сложно тестировать схему путем индивидуального тестирования ее подсхем. Рассмотрим случай аналоговой схемы с двумя каскадами С1 и С2, каждый из которых имеет один вход и один выход, и передаточные функции по напряжению Н1 и Н2. С1 и С2 могут работать неправильно когда тестируются индивидуально из-за несовершенства производственного процесса, который искажает их передаточные функции. Однако, когда каскады соединяются вместе может случиться так, что искажение в Н1 компенсируется искажением в Н2, которое в некотором смысле может быть инверсией искажения Н1. Следовательно комбинация каскадов С1 и С2 фактически работает правильно. И наоборот, по отдельности правильные аналоговые подсхемы при соединении формируют неправильную схему.[1]

Содержание

Функциональное тестирование с использованием DSP

В настоящее время практически все аналоговые схемы тестируются с использованием автоматизированных систем контроля (АСК) построенных на базе DSP. Данные АСК вместо использования реальных аналоговых измерительных инструментов, выполняют их эмуляцию на основе быстрого преобразования Фурье (БПФ) и дискретного преобразования Фурье (ДПФ), для того чтобы уменьшить ошибку измерения и устранить нежелательное время установления сигнала при тестировании.[1]

На рисунке 1 представлена традиционная аналоговая АСК. Стоит обратить внимание, что она не имеет средств синхронизации между блоками генерации воздействий и анализа реакций. На рисунке 2 представлена АСК на базе DSP, которая имеет соответствующую синхронизацию и состоит из АЦП, ЦАП, памяти для хранения воздействий и реакций, DSP, который управляется программно. DSP может эмулировать широкий набор измерительных инструментов. Инструментами теперь являются подпрограммы, которые обрабатывают вектора численных значений. Вектор может представлять собой набор выборок сигнала, частотный спектр и т.д. Специалист по тестированию создает набор векторов в виде тестовых сигналов. Синтезатор сигналов подает эти вектора на ЦАП, выход которого соединен с восстанавливающим фильтром для получения непрерывного сигнала с ограниченной полосой пропускания. Полученный сигнал подается на испытываемое устройство, с которого снимаются реакции. Дискретизатор аналоговых сигналов выполняет оцифровку снятых реакций с использованием высокоскоростного АЦП и сохраняет выборки в ОЗУ. Когда в качестве испытываемого устройства выступает аналогово-цифровая схема, сигналы с выходов цифровой части записываются во входную память, а тесты для цифровой части подаются на объект диагностики (ОД) из выходной памяти.[1]

На рисунке 3 изображен процесс синтеза аналогового сигнала, а на рисунке 4 процесс оцифровки.

Рисунок 1 — Традиционная аналоговая АСК [1]

Рисунок 2 — Аналоговая АСК на базе DSP [1]

Рисунок 3 — Синтез аналогового сигнала [1]

Рисунок 4 — Оцифровка аналогового сигнала [1]

Преимущества АСК на базе DSP

• Точность. АСК на базе DSP практически всегда обладают большей точностью, чем аналоговые инструменты, так как ошибка в наборе выборок сигнала значительно меньше после цифровой обработки, чем ошибка индивидуальной выборки. Наводки, шум и отклонения сигналов значительно сокращаются в DSP-тестерах, так как аналоговый сигнал оцифровывается на самой ранней стадии. Старение компонентов тестера и температурные эффекты вызывают значительно меньше проблем, так как цифровые компоненты лучше сохраняют свои характеристики, чем аналоговые. [1]

• Скорость. DSP тестер может получить набор выборок от ОД за один период выборки, а далее используя ДПФ и БПФ выполнить над ним различные измерения путем эмуляции инструментов. Для выполнения множественных измерений DSP-тестер значительно более эффективен, чем аналоговый, в котором надо выполнять множественные измерения. Также в DSP-тестере отсутствуют временные расходы на установление сигнала в фильтре, которые присутствуют в аналоговом тестере.

[1]

• Простота использования. Так как тестер цифровой, то легко повторять тестирование, выполнять настройку и сохранять выполненные настройки.

• Больше измерительной информации. DSP тестер предоставляет дополнительную информацию вместе с измеряемым параметром, например, пиковый детектор сообщает не только о значении пика, но и про расположение пика во времени.

• Размер и мощность. АСК общего назначения на базе DSP меньше, дешевле и требует меньшей мощности, чем соответствующая аналоговая АСК.

Недостатки АСК на базе DSP

• они дороги, хотя цена снижается благодаря использованию СБИС. Разрядность, необходимая для достижения приемлемой точности, и требования по полосе пропускания делают DSP дорогими;

• когда необходимо выполнять только одно измерение, чисто аналоговые тестеры дешевле. DSP обладают преимуществом только при множественных измерениях;

• гибкость инструментария является проблемой для неопытного оператора, так как необходимо знать теорию их использования;

• специалист по тестированию должен знать физические и математические принципы, которые лежат за каждым тестом и источником ошибок. [1]

Реализация алгоритмов DSP с помощью ПЛИС

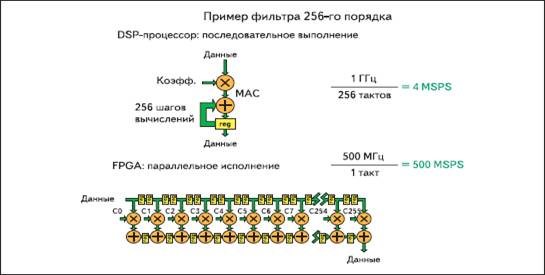

Практически с момента своего появления FPGA позиционировались как устройства, превосходящие сигнальные процессоры по соотношению производительность/цена. В то же время известно, что программируемые микросхемы не могут конкурировать с ASIC (специализированная для решения конкретной задачи интегральная схема (ИС)) по цене и тактовой частоте.[3] На рисунке 3 проиллюстрированы различия между сигнальным процессором и FPGA при выполнении операции цифровой фильтрации.

Рисунок 3 – Выполнение цифровой фильтрации в сигнальном процессоре и FPGA [3]

На этом рисунке видно, что, хотя сигнальный процессор, созданный по сопоставимой технологии, в среднем обладает более высокой тактовой частотой, единственный поток исполнения команд обуславливает резкое уменьшение общего числа операций (если под «операцией» понимать всю последовательность умножений и сложений, требующуюся для реализации всего фильтра или иного алгоритма). В то же время FPGA вполне могут обеспечить однотактное исполнение всех операций, используя параллельный расчет. Этому способствует, очевидно, наличие большого числа блоков DSP, выполняющих умножение с накоплением. Нетрудно заметить, что для эффективного использования этого преимущества следует ориентироваться на алгоритмы и методы, подразумевающие распараллеливание операций — фильтры высоких порядков, быстрое преобразование Фурье, вейвлет-анализ и т. п. [3]

Кроме того, важным преимуществом FPGA является их способность обеспечивать не просто высокую скорость обработки, но еще и непрерывную обработку на стабильной скорости.

Процессорное ядро может выполнять организацию интерфейса, настройку, мониторинг, загрузку коэффициентов и прочие операции, реализовывать которые аппаратно чересчур сложно. При этом единственное процессорное ядро может обеспечивать управление несколькими сотнями DSP-блоков ПЛИС, которые постоянно выполняют обработку входящего потока даже без участия процессора. [3]

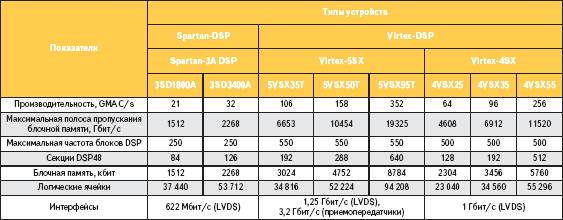

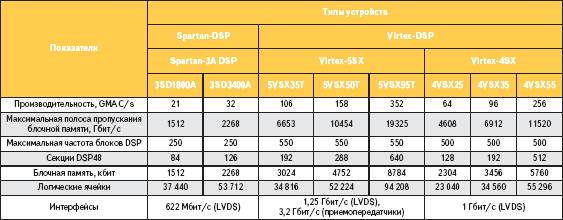

Таблица 1. Технические характеристики устройств FPGA Xilinx, ориентированных на цифровую обработку сигналов [3]

Результаты работы (на момент написания автореферата)

На момент написания автореферата были получены следующие результаты:

• Выполнен обзор существующих методов тестирования;

• на основе технических характеристик и по соотношению цена\качество была выбрана элементная база для реализации анализатора аналоговых тестовых реакций;

• проведены исследования и разработано экспериментальное устройство выборки аналоговых тестовых реакций с помощью отладочного FPGA комплекса. В настоящее время проводятся исследования по повышению быстродействия устройства выборки.

Выводы

На основе вышеизложенного материала можно сделать вывод, что:

• разработка и исследование методов и структур аппаратного анализа аналоговых тестовых реакций является крайне актуальной;

• сформулированные задачи позволят достигнуть поставленной цели;

• на основе выполненного обзора существующих разновидностей тестирования аналоговых и АЦ-устройств для исследования было выбрано тестирование с использованием DSP;

• для построения тестов и анализа полученных тестовых реакций в данной работе был выбран оптимальный класс катастрофических и параметрических неисправностей;

• в качестве аппаратной реализации был выбран отладочный FPGA комплекс Spartan-3E.

Список использованой литературы

1. Agrawal V.D. Essentials of electronic testing for digital, memory and mixed-signal VLSI circuits / V.D. Agrawal, M. L. Bushnell // Boston: Kluwer Academic Publishers, — 2000, 650p.

2. Bapiraju Vinnakota. Analog and mixed-signal test / Bapiraju Vinnakota // Prentice Hall PTR, 1998. — 261p.

3. Тарасов И. Возможности FPGA фирмы Xilinx в задачах цифровой обработки сигналов [Электронный ресурс] Режим доступа: http://www.kit-e.ru/articles/plis/2007_5_68.php

4. Тарасов И. Сравнительный анализ архитектуры основных семейств ПЛИС FPGA фирмы Xilinx [Электронный ресурс] Режим доступа: http://www.kit-e.ru/articles/plis/2005_6_96.php

5. Давыдов П.С. Техническая диагностика радиоэлектронных устройств и систем / П.С. Давыдов // М.: Радио и связь, 1988. — 256 с.

6. Зинченко Ю.Е. Проблемы зондового поиска неисправностей и пути их решения / Ю.Е. Зинченко, А.М. Козинец, К.Н. Жилин // Сборник трудов Донецкого государственного технического университета. Серия: Информатика, кибернетика и вычислительная техника, выпуск 6. — Донецк: ДонГТУ, 1999.— С. 212—217.

7. Zinchenko Yuri E. Computer-aided design and hardware description languages / Yuri E. Zinchenko // Сборник трудов Донецкого государственного технического университета. Серия: Проблемы моделирования и автоматизации проектирования динамических систем, выпуск 10. — Донецк: ДонГТУ, 1999.— С. 210—216.

8. Суворова Е.А. Проектирование цифровых систем на VHDL / Е.А. Суворова, Ю.Е. Шейнин // СПб.: БХВ-Петербург, 2003. — 576 с.

9. Зинченко Ю.Е. Синтез оптимальных структур асинхронных сигнатурных анализаторов / Ю.Е. Зинченко // Сборник трудов Донецкого государственного технического университета. Серия: Информатика, кибернетика и вычислительная техника, выпуск 6. - Донецк: ДонГТУ, 1999.— С. 186—191.

10. Поляков А.К. Языки VHDL и VERILOG в проектировании цифровой аппаратуры / А.К. Поляков // М.: СОЛОН-Пресс, 2003. — 320с.

|