Библиотека

АРХИТЕКТУРА И ПРОГРАММНОЕ ОБЕСПЕЧЕНИЕ ГРАФИЧЕСКОЙ СИСТЕМЫ НА БАЗЕ ПРОГРАММИРУЕМОЙ ЛОГИЧЕСКОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ VIRTEX-II PRO

Разработаны архитектура и программное обеспечение графической системы в интегрированной среде авто-матизации проектирования электроники Xilinx ISE Design Suite

Ключевые слова: архитектура; программное обеспечение; графическая система; проектирование; PowerPC; встроенный процессор.

Современный этап развития программного обеспечения вычислительной техники характеризуется широким применением программно-аппаратных комплексов, которые строятся по принципу «система на кристалле»(System-on-Chip). В первую очередь эта тенденция проявляется в программируемых логических интегральных схемах (ПЛИС) с архитектурой FPGA [1-5]. При таком подходе кристалл ПЛИС рассматривается как сво-бодный конфигурируемый логический ресурс, на базе которого реализуются все необхо-димые устройства вычислительной системы. Ведущими мировыми производителями ПЛИС являются фирмы Xilinx и Altera, которые предоставляют и программное обеспече-ние для разработки проектов, а также для последующего конфигурирования кристаллов [6;7].

Графические системы состоят из различных уровней аппаратного и программного обеспечения, необходимого для того, чтобы вычислительная система отображала графи-ческую информацию на LCD. Как правило, графическая система состоит из графического процессора (GPU), выполняющего математические операции, необходимые для формиро-вания изображения, которое сохраняется в области памяти, называемой «кадровый буфер» (frame buffer), и контроллера LCD, считывающего содержимое кадрового буфера и пере-дающего данные на вход LCD. Также необходимо программное обеспечение для управле-ния аппаратурой и предоставления интерфейса программирования приложений (API) для разработчиков прикладных программ. Современные графические контроллеры обычно выполняются на специализированных микросхемах (ASIC) - главным образом из-за высо-ких требований к производительности, особенно в трехмерных приложениях.

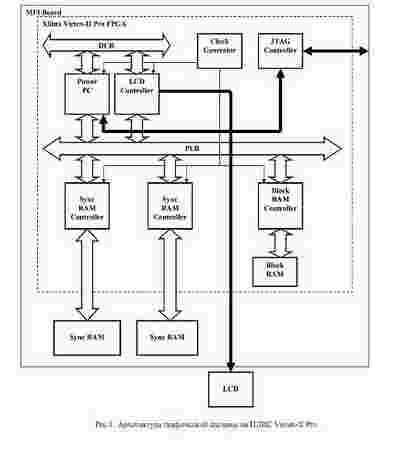

Связи между компонентами графической системы выполнены на основе шинной архитектуры PLB и DCR, а их адреса и прерывания установлены с помощью программы Xilinx Platform Studio. С помощью программы Xilinx Platform Studio SDK разработаны приложения для демонстрации функционирования графической системы, которые используют функции прорисовки пикселей, линий, прямоугольников, окружностей и отображения символьной информации.

Особенностью ПЛИС Virtex-II Pro является то, что она имеет интегрированный процессорный блок PowerPC 405, который состоит из ядра фирмы IBM PowerPC 405-D5 RISC, контроллера OCM, схемы синхронизации и интерфейса с ПЛИС Virtex-II Pro. Встроенное процессорное ядро позволяет работать на частоте до 300 Mhz с малой потребляемой мощностью. Специально разработанный интерфейс объединяет процессор с компонентами ПЛИС.

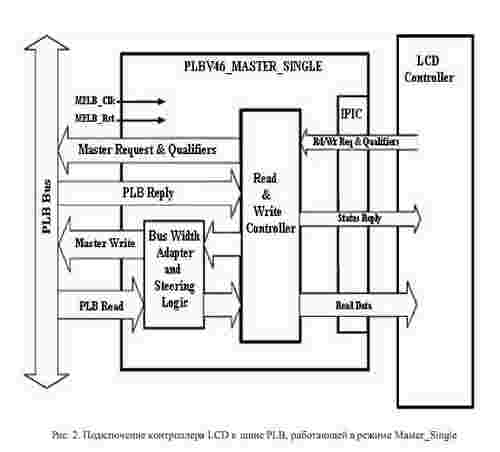

В разработанном проекте графической системы программа находится в памяти Block RAM. Процессор исполняет коды программы и модифицирует содержимое видеобуфера. Шина PLB представляет собой разделяемую шину, работающую по принципу «мастер-подчиненный» (Master-Slave). PLB имеет адресную шину, двунаправленную шину данных и шину управления. В среде Xilinx Platform Studio контроллер LCD подключается к шине PLB через интерфейс IPIC, включающий в себя шины Rd/Wr Req & Qualifiers, Status Reply и Read Data. Основные задачи IPIС – декодирование адреса и генерирование сигнала выбора устройства. Большинство сигналов шины PLB просто транслируются через IPIС. Принцип подключения контроллера LCD через IPIС показан на рис.2.

Разработанный контроллер LCD имеет три порта, с помощью которых он подключается к шинам IPIC Rd/Wr Req & Qualifiers, Status Reply и Read Data. Шина Rd/Wr Req & Qualifiers включает в себя адресную шину и сигнал запроса на чтение данных. Шина Status Reply используется для передачи статусных сигналов, которые указывают, что адрес распознан и на шине достоверные данные. Шина Read Data используется для передачи данных на контроллер LCD. Данные передаются за один цикл шины одним 32-битным блоком.

Шина DCR, аналогично PLB, работает по принципу «мастер-подчиненный» (MasterSlave) и используется для исключения конфигурационных регистров контроллера LCD из адресного пространства шины PLB, что повышает пропускную способность шины PLB.

Контроллер LCD состоит из модуля управления LCD, модуля прямого доступа к памяти и модуля генерирования прерывания. Алгоритмы работы модулей контроллера LCD реализованы с использованием языка описания аппаратуры Verilog [8].

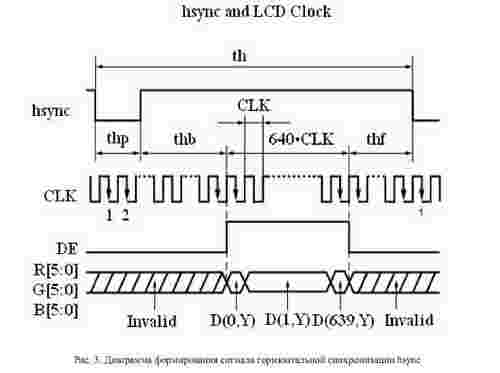

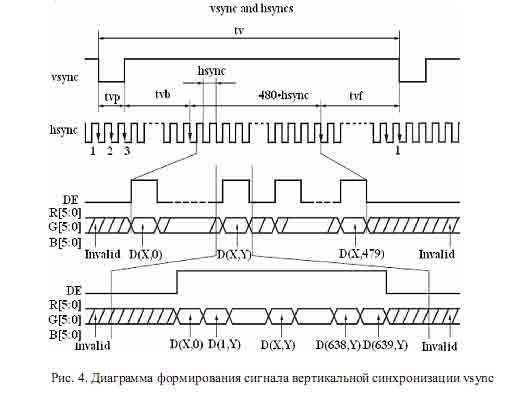

Модуль управления LCD генерирует сигнал горизонтальной синхронизации hsync, сигнал вертикальной синхронизации vsync, сигнал разрешения DE и сигналы R[5:0], G[5:0], B[5:0], несущие данные соответственно о красной, зеленой и синей составляющих пикселя. Сигналы горизонтальной (hsync) и вертикальной (vsync) синхронизации обеспечивают регенерацию изображения на экране монитора 60 раз в секунду.

На рис.3 представлена диаграмма формирования сигнала горизонтальной синхронизации hsync, а на рис.4 – диаграмма формирования сигнала вертикальной синхронизации vsync. Из рис.3 следует, что сигнал hsync имеет интервалы thp, thb, DE и thf, длительность которых составляет соответственно 96, 48, 640 и 16 тактовых импульсов CLK. Поэтому длительность интервала hsync равна длительности 800 тактовых импульсов CLK. Сигнал вертикальной синхронизации vsync состоит из интервалов tvp, tvb, DE и tvf, длительность которых составляет соответственно 2, 31, 480, 12 импульсов hsync. Таким образом, длина интервала vsync равна 525 hsync и при частоте тактового сигнала, которая для данного LCD с разрешением 640x480 равна 25Mhz, составляет 16 мс. На рис.3, 4 представлен сигнал DE, который управляет передачей данных о пикселях LCD, и имеет длительность активного интервала, равную 640 тактовым импульсам CLK. Длительность пассивного интервала составляет 160 тактовых импульсов CLK во время горизонтальной развертки и 45 импульсов hsync во время вертикальной синхронизации.

Модуль прямого доступа к памяти состоит из спроектированных элементов: счетчика адреса, управляющего автомата и интерфейса с шиной PLB. Асинхронное FIFO (First Input First Output) связывает между собой модуль прямого доступа к памяти и контроллер LCD, работающие соответственно на частотах 100 и 25 Mhz. Кроме этого, FIFO буферизует данные о пикселях, чтобы обеспечить их непрерывное считывание в LCD, а также преобразует данные из 32-битного формата в 8-битный. Так как для хранения данных о цвете каждого пикселя используется палитра, то данные с выхода FIFO, прежде чем попасть на вход LCD, декодируются. Декодирование осуществляется с помощью таблицы цветов (CLUT). Вход разрешения чтения из FIFO управляется сигналом разрешения DE модуля синхронизации LCD. Вход разрешения записи, вход заполнения и вход данных FIFO представляют собой выходы управляющего автомата, который непрерывно и циклически обеспечивает поток данных из видеобуфера для регенерации изображения на LCD. Модуль асинхронного FIFO был сгенерирован в программе CoreGenerator [6], настроен и инициализирован в ISE Project Navigator.

Связь модуля прямого доступа к памяти с шиной PLB реализована на базе управляющего автомата, который обеспечивает протокол шины PLB и непрерывно, циклически считывает данные из видеоОЗУ, инкрементируя содержимое счетчика адреса. Так как контроллер LCD имеет интерфейс шины PLB, то он считывает данные из видеоОЗУ с любого адреса в пределах адресного пространства шины. Чтобы считывать данные по нужному адресу и знать объем видеобуфера, используются два регистра: регистр адреса и регистр размера буфера. Данные в регистры загружаются программно процессором через шину DCR. Доступ к регистрам DCR осуществляется посредством ассемблерных инструкций mtdcr, mfdcr, и макросов mtdcr(addr,data), mfdcr(addr), которые описаны в заголовочном файле xpseudo_asm_gcc.h среды Xilinx SDK. Управляющий автомат контроллера LCD имеет четыре состояния: ожидания, запроса на чтение, квитирования команды и завершения команды.

Модуль генерирования прерывания формирует сигнал прерывания после отображения кадра одного из двух буферов. Это необходимо для того, чтобы выполнять перестановку кадров в тот момент, когда кадр не считывается контроллером LCD. В этом случае искажения на экране монитора отсутствуют.

В разработанной графической системе процессор PowerPC 405 использует таблицу векторов прерываний [6]. При написании программ на языке С/C++ в Xilinx Platform Studio SDK инициализируется таблица прерываний с помощью функции void XExc_Init (void) и регистрируется собственный обработчик прерываний void XExc_RegisterHandler (Xuint8 ExceptionId, XExceptionHandler Handler, void *DataPtr) [5].

Разработанный контроллер памяти, имея интерфейс шины PLB, обеспечивает операции чтения и записи в микросхемы памяти CY7C1381C [9], расположенные на печатной плате, процессором PowerPC и контроллером LCD.

В программе Project Navigator создан проект графической системы, главный модуль которого включает в себя микропроцессорную систему, созданную в Xilinx Platform Studio, в виде подмодуля. Также в главном модуле реализованы порты с z-состоянием, а в файле ограничений проекта порты главного модуля назначены на соответствующие выводы микросхемы.

На этапе отладки архитектуры графической вычислительной системы, созданный проект компилируется с целью получения файла конфигурационной последовательности, который с помощью программы iMPACT загружается через интерфейс JTAG в конфигурационную статическую память ПЛИС Virtex-II Pro[5]. После загрузки конфигурационного файла, созданные в среде Xilinx Platform Studio SDK демонстрационные приложения, загружаются через интерфейс JTAG с помощью отладчика XMD в оперативную память Block RAM. Затем осуществляется сброс процессора и запуск программы на исполнение. Результат работы программы представлен на рис. 5.

В результате экспериментальных исследований разработанного проекта графической системы было установлено, что максимальная скорость построения графических примитивов ограничивается пропускной способностью контроллера памяти видеоОЗУ и разделяемой шины PLB. Это обусловлено тем, что шина PLB имеет разделяемую архитектуру, которая поддерживает сложные схемы арбитража и поэтому вносит задержки при обращении процессора к видеоОЗУ. Кроме того, процессор и контроллер LCD, являющиеся мастерами шины PLB, могут обращаться к видеоОЗУ только последовательно, что также увеличивает время построения графических примитивов.

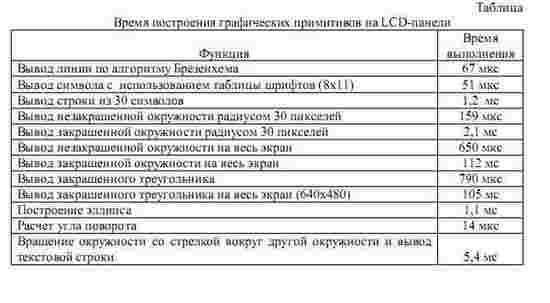

Ограничение доступа к памяти обусловлено ещё и тем, что запись и чтение данных из памяти происходит только блоками по 32 бита. При этом если для хранения данных об одном пикселе используется 32 бита, например при формате RGBA8888, этот вариант оптимально подходит. Но если для хранения данных об одном пикселе используется другой формат, например RGB565 или палитра, то для изменения значения одного пикселя необходимо выполнить два цикла обращения к памяти (чтение и запись) и использовать битовые маски и сдвиги, что приводит к замедлению работы графической системы. Время построения графических примитивов на LCD-панели представлено в таблице.

Из анализа работы архитектуры вычислительной системы следует, что для уменьшения времени построения графических примитивов необходимо дополнительно спроектировать ускоритель двухмерной графики и мультиплексируемую шину, которая позволит процессору и контроллеру LCD работать в параллельном режиме при обращении к видеоОЗУ.

Список литературы

- Грушвицкий, Р.И. Проектирование систем на микросхемах с программируемой структурой / Р.И.Грушвицкий, А.Х.Мурасаев, Е.П.Угрюмов. - 2-е изд.,перераб. и доп.-СПб.: БХВ-Петербург, 2006. - 736 с.

- Симкин, Н.В. Разработка программного обеспечения обработки потока данных, поступающих с аналого- цифрового преобразователя с временным чередованием каналов/Н.В.Симкин, В.В. Симкин // Труды факультета технической кибернетики «Практика применения научного программного обеспечения в образовании и научных исследованиях».-СПб.: СПбГПУ, 2006.-С.128-129.

- Симкин, Н.В. Разработка реконфигурируемого персонального компьютера на базе синтезируемого процессорного ядра NIOS II и LCD WINSTAR/Н.В.Симкин//Материалы 61-й студенческой научной конференции.- Брянск: БГТУ, 2006.-277 с.

- Симкин, Н.В. Разработка архитектуры и программного обеспечения видеосистемы осциллографа на базе синтезируемого процессорного ядра NIOS II/Н.В.Симкин//Труды факультета технической кибернетики «Практика применения научного программного обеспечения в образовании и научных исследованиях».- СПб: СПбГПУ, 2007.-С.118.

- Зотов, В.Ю.Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx/В.Ю.Зотов.-М.: Горячая линия-Телеком, 2006.-520 с.

- http://www.xilinx.com [Электронный ресурс]/ — Электронные данные — Режим доступа: http://www.xilinx.com, свободный

- http://www.altera.com [Электронный ресурс]/ — Электронные данные — Режим доступа: http://www.altera.com, свободный

- Verilog HDL Reference manual/IEEE 1364 standard.- 1997.

- http://www.cypress.com [Электронный ресурс]/ — Электронные данные — Режим доступа: http://www.cypress.com , свободный