Kevin A. Kwiat, Ph.D., Air Force Research Laboratory (AFRL/IFGA)

Для более чем четверти века, теперь - вечности, в ходе разработки современных компьютеров - принцип, что аппаратное и программное обеспечение логически эквивалентно, осталось неизменным [1], [2]. Этот принцип не только противостоял изменению, но и стал основанием для нового подхода к архитектуре ЭВМ: реконфигурируемые вычисления. Выбор, реализовать ли логику в аппаратных средствах или программном обеспечении, всегда был проектным решением, основанным на том, куда переместить сложность: к аппаратным средствам или программному обеспечению. Высокая скорость обычно означает интенсивную реализацию аппаратными средствами, тогда как способ уменьшить размер, вес и питание аппаратных средств заключается в том, чтобы положиться больше на реализацию программным обеспечением. 1990-ые годы показали, что различие между аппаратным и программным обеспечением, размыта статической RAM (SRAM), базирующейся на программируемой пользователем вентиляционной матрице (ППВМ, FPGA). Содержание конфигурационной памяти стало программным обеспечением, которое изменяет аппаратные средства.

Теперь реализацию алгоритмов, которые ранее, из-за их сложности, можно было рассмотреть только с использованием программного обеспечения, можно возложить на аппаратную реализацию. Такой подход возможен при переходе с программного обеспечения на аппаратные средства - SRAM-на-основе FPGA. SRAM-на-основе FPGA, которые разрешают записывать и переписывать данные конфигурационной памяти, параллельно с работой устройства, называют динамически реконфигурируемыми FPG. Возможность получения с помощью программного обеспечения аппаратных средств состоящих из отдельных логических элементов – это и есть главная цель динамически реконфигурируемых FPGA. У разработчиков появилась возможность гибко управлять динамически реконфигурируемыми FPGA, чтобы создавать реконфигурируемые компьютеры [3]. Это предложение улучшало производительность, все еще оставаясь в пределах разумных мер по объему и технической реализации. Однако, есть предположение что надежность динамически реконфигурируемых FPGA, противоположна их традиционным аналогам с фиксированными аппаратными средствами, и может не устраивать конечного пользователя?

В цифровой логике показатель сложности - логические элементы. Логические элементы - физические объекты, которые занимают пространство, используют питание и ресурсы маршрутизации микросхемы в рабочем состоянии, следовательно если количество логических элементов больше , то надежность ниже. Однако, при более детальном рассмотрении понятия виртуальных логических элементов, мы видим, что это не так. Эти логические элементы являются виртуальными так же как компьютерная виртуальная память - где оперативную память составляет больше, чем есть на самом деле. Т.е. когда страницы оперативной памяти не нужны более, они выгружаются на диск и хранятся там, пока они не понадобятся снова. Ячейки динамически реконфигурируемого FPGA реализуют логические элементы, которые соединены так, чтобы сформировать логическую функцию; все же, когда эта логическая функция больше не нужна, и ячейки снова используются другой логической функцией, где находятся логические элементы предыдущего функционального блока? Это - ключевой вопрос в понимании сложности реконфигурируемого компьютера.

Чтобы ответить на этот вопрос, можно экстраполировать от широко принятого метода [4] прогноза надежности, который вычисляет интенсивность отказов, основанную на количестве логических элементов. Можно вычислить интенсивность отказов для этих двух случаев: стандартный подход с фиксированной аппаратной логикой, где используются традиционные логические элементы, и динамически реконфигурируемый подход FPGA, в котором используются виртуальные логические элементы.

Для этих двух случаев интенсивность отказов, λ, вычисляется формулой:

| λ = (C1πT + C2πE)πQπL |

|

| где, | |

| C1 = снижение интенсивности отказов сложности | |

| πT = температурный фактор | |

| C2 = интенсивность отказов сложности пакета | |

| πE = фактор окружающей среды | |

| πQ = фактор качества | |

| πL = изучаемость | |

В предыдущих вычислениях, следующие значения являются постоянными: πT = 0.16, πE = 0.5, πQ = 3, и πL = 1. Относительно постоянного фактора изучения для обоих случаев можно использовать динамически реконфигурируемые FPGA серии AT6000 Atmel, которые компания распространяет как законченную технологию (см. http://www.atmel.com/products/FPGA/). Кроме того, некоторая ранняя работа была выполнена с разработкой инструментов CAE, которые моделировали динамически реконфигурируемые FPGA [5]. Это также внесло поправки к восхождению кривой обучения в использовании виртуальных логических элементов вместо фиксированных логических элементов .

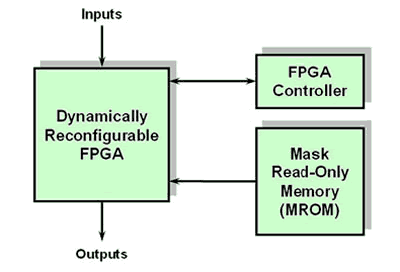

Для фиксированного аппаратного проекта C1 измеряется, подсчетом логических элементов. Внешняя SRAM на микросхемах реконфигурируемых FPGA является энергозависимой, эта память необходима для того, чтобы сохранять данные конфигурации FPGA. FPGA считается запрограммированным, когда данные конфигурации считаны из внешней памяти и загружены в память конфигурации SRAM FPGA на микросхеме. Поэтому, только когда добавлено внешнее хранение (см. рисунок 1), реализация FPGA может создавать логические элементы и следовательно можно производить подсчеты. C1 для незапрограммированного FPGA считается исключительно по количеству логических элементов. Т.е. состоит из ячеек FPGA, памяти конфигурации на микросхеме и внутренней логики программирования.

Рисунок 1. Реконфигурируемая вычислительная система

С использованием внешней памяти для сохранения конфигурации FPGA показатель C1 увеличивается . Однако, внешняя память позволяет перемещать сложность от одних логических элементов к другим. Для внешней памяти можно использовать - запрограммированный ROM (MROM). Типичная размер MROM составляет 16 мегабит в одной микросхеме. При моделировании на AT6000, трехбайтовая программная ячейка соответствует одному логическому элементу реализованному в ячейке. Увеличение количества логических элементов проекта подразумевает 3-байтовое увеличение MROM. Например, 1 Мбит MROM может использоваться, чтобы реализовать 41 600 логических вентилей. Значение C1 для MROM подобного размера - только 0.0052, в то время как значение C1 для эквивалентного числа аппаратных логических элементов 0.29 - фактор 55 кратного увеличения сложности. С 16 мегабитами MROM FPGA может реализовать приблизительно 666 666 логических вентилей.

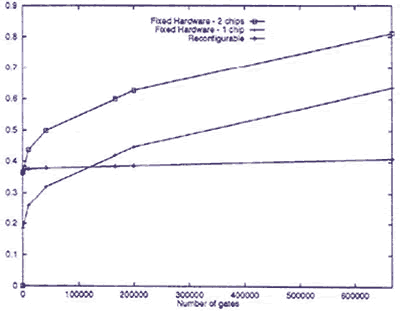

Для фиксированного аппаратного решения рассмотрим два случая. Первым является решение для одного пакета, а вторым является решение с двумя пакетами. Вычисление интенсивности отказов для реконфигурируемого подхода включает три составляющие : FPGA, контроллер и MROM. Число контактов для одного пакета FPGA составляет 224. Контроллер состоит из 1 000 логических элементов и начальное количество штырьковых выводов корпуса составляет 36. Первоначально, MROM размером 3 байта (для 1 логического элемента) соответствует 16-контактная микросхема. Рисунок 2 показывает интенсивность отказов между фиксированным аппаратным проектом и реконфигурируемым проектом.

Горизонтальная ось - число требуемых логических элементов. Для фиксированного аппаратного случая это число – такое же как при фиксированном подсчете элементов . Для FPGA это - число логических элементов, реализованных посредством динамического реконфигурирования. Первоначально, интенсивность отказов для незапрограммированного FPGA достаточно высока из-за его четкого количества логических элементов - 55 296. Однако, сложность для каждого реализованного логического элемента на FPGA в значительной мере зависит от 24-разрядного инкремента MROM. В результате интенсивность отказов для FPGA, счетчика и MROM растет только немного по сравнению с кривыми для фиксированных аппаратных решений. Сравнивая интенсивность отказов реконфигурируемых и фиксированных проектов, в случае с фиксированными логическими элементами есть большая интенсивность отказов, когда количества логических элементов превысит 130 000. При более высоком количестве логических элементов, случай с двумя пакетами, интенсивность отказов существенно больше, чем для реконфигурируемого проекта (см. рис 2).

Рисунок 2. Число логических элементов в сравнении с интенсивностью отказов

Фиксированные логические элементы пользовательской специализированной интегральной схемы (ASIC) могут реализовывать компьютерные алгоритмы непосредственно в аппаратных средствах; при этом все же большое количество фиксированных логических элементов будет необходимо. Фиксированные логические элементы могут использоваться, чтобы реализовать микропроцессор, который будет выполнять алгоритмы программного обеспечения . Однако, современные микропроцессоры по плотности легко превышают количество логических элементов , показанных на рисунке 2. Как правило, выполнение микропроцессором программного обеспечения возможно только тогда , когда микросхемы кэша и блоки управления памятью повышают и дополняют основные функции ЦП процессора.

Литература: