Подход к унификации процесса синтеза МПА Мура для FPGA

Ковалев С.А., Зеленёва И.Я., Татолов Е.Р.

Донецкий национальный технический университет

Интегральные схемы (ИС) широко используются при реализации цифровых систем различного функционального назначения [1, 2]. Известно, что цифровые ИС разделяются на стандартные и специализированные. Стандартные ИС имеют практически «жесткую» внутреннюю структуру и пользователь может влиять на характер их функционирования только программированием (если оно возможно). Специализированные ИС проектируются по конкретному заказу и требуют значительных средств и длительного периода разработки.

К классу стандартных ИС относятся программируемые логические интегральные схемы (ПЛИС), которые включают в себя программируемые логические устройства (ПЛУ) и программируемые пользователем вентильные матрицы (FPGA – Field-Programmable Gate Arrays) [1, 3].

Описанные виды стандартных и специализированных ИС широко используются при проектировании микропрограммных автоматов (МПА), которые применяются, главным образом, для создания устройств управления [3].

Практическая реализация МПА и структур их оптимизации для FPGA базируется на применении языков описания аппаратуры (HDL – Hardware Description Language) [2], а также средств синтеза и имплементации. Практически каждый производитель FPGA предоставляет соответствующую систему автоматизированного проектирования (САПР), поддерживающую подобный сквозной процесс проектирования [2].

Подход к унификации процесса синтеза МПА Мура

Современные неоптимизированные проекты цифровых устройств могут иметь значительную избыточность, что ведет к неэффективному использованию ресурсов FPGA-микросхемы [3]. Следовательно, актуальной является задача аппаратурной оптимизации, которая, в контексте FPGA, сводится к снижению процента использования тех или иных внутренних блоков: LUT-элементов (LUT – Look-Up Table), памяти, схем синхронизации.

Сущность предлагаемого процесса синтеза заключается в следующем. На первом этапе представление МПА сводится к унифицированной форме – таблице переходов. Этот шаг связан с тем, что спецификация автомата Мура может быть проведена путем использования различных форм представления: граф-схем, диаграмм состояний, ASM-диаграмм (ASM – Algorithmic State Machine) [4]. Затем, в зависимости от особенностей конкретного МПА (полностью определенный или частичный), выполняется минимизация таблицы переходов и кодирование ее состояний. Далее формируются функции следующего состояния и, при необходимости, выходные функции автомата. Этап адаптации предполагает использование приемов построения логической схемы МПА, направленных на уменьшение аппаратурных затрат целевой микросхемы [5].

Таким образом, предлагаемый процесс синтеза МПА Мура (рис. 1) включает в себя последовательное применение алгоритмических и схемных оптимизационных приемов с учетом базиса FPGA. Такой подход может быть с успехом реализован в САПР и предполагать только управленческие функции пользователя: описание МПА и выбор используемых алгоритмов и структур.

Рисунок 1 – Подход к унификации процесса синтеза МПА Мура для FPGA

Для оценки эффективности применения предлагаемого процесса синтеза к конкретному примеру, были разработаны пять Verilog-программ, реализующих заданный МПА Мура (рис. 2) различными способами:

Рисунок 2 – Диаграмма состояний заданного МПА Мура

- Реализация неминимизированного МПА Мура с помощью встроенного анализатора XST (Xilinx Synthesis Technology) [6] (эксперимент 1).

- Реализация минимизированного МПА Мура с помощью встроенного анализатора XST (эксперимент 2).

- Реализация минимизированного МПА Мура по PY-схеме [5]. Использование ПЗУ с асинхронным чтением [6] (эксперимент 3).

- Реализация минимизированного МПА Мура по PY-схеме. Использование ПЗУ с синхронным чтением [6] и дополнительного сигнала синхронизации (эксперимент 4).

- Реализация минимизированного МПА Мура по PY-схеме. Использование ПЗУ с синхронным чтением и заднего фронта основного сигнала синхронизации (эксперимент 5).

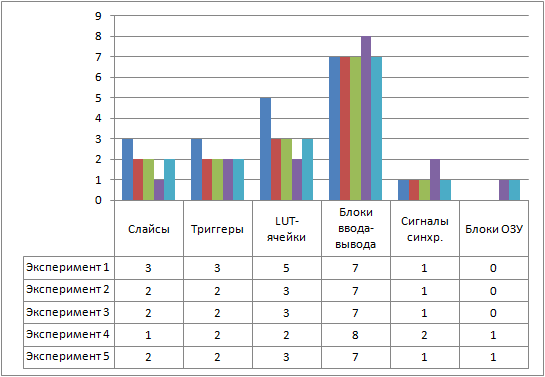

Все исследования проводились с помощью Xilinx ISE 9.2i для семейства FPGA Xilinx Spartan-3, а именно для микросхемы XC3S200. Результаты совокупных аппаратурных затрат для пяти вариантов реализации графически показаны на рис. 3.

Рисунок 3 – Результаты исследований

Если целью оптимизации являлось количество LUT-ячеек, то лучший результат синтеза был получен при использовании PY-реализации автомата Мура с синхронным ПЗУ и двумя сигналами синхронизации (эксперимент 4). По сравнению с экспериментом 1, количество слайсов уменьшилось в 3 раза, количество триггеров – в 1,5 раза, а количество LUT-ячеек – в 2,5 раза. Однако, в этом случае увеличилось общее количество выводов схемы, количество сигналов синхронизации и было задействовано одно оперативное запоминающее устройство (ОЗУ).

Выводы

Предлагаемый подход к унификации процесса синтеза автоматов Мура для FPGA направлен на уменьшение уровня аппаратурных затрат в целевой микросхеме. Такая оптимизация достигается за счет применения алгоритмических (минимизация таблицы переходов, кодирование внутренних состояний) и схемных (адаптация логической схемы МПА) методов.

Направления дальнейших исследований направлены на рассмотрение двух аспектов – научно-теоретического и экспериментального.

В рамках научно-теоретических исследований планируется осуществить: поиск множества альтернативных алгоритмов для основных этапов методики синтеза; оценку и обоснование условий целесообразности использования тех или иных вариантов основных этапов синтеза; адаптацию известных методов и структур синтеза к базису FPGA и используемым программным средствам; предложение новых или улучшение известных алгоритмов, методов, подходов.

Экспериментальные исследования предполагают: программную реализацию разработанной методики синтеза автоматов Мура для FPGA (система автоматизированного проектирования автоматов Мура – САПРАМ); разработку в рамках САПРАМ интерфейса для добавления и исследования новых алгоритмов для основных этапов синтеза; использование конкретного целевого базиса FPGA – семейства микросхем Xilinx Spartan-3.

Список литературы

- Грушвицкий Р.И., Мурсаев А.Х., Угрюмов Е.П. Проектирование систем на микросхемах программируемой логики. – СПб.: БХВ-Петербург, 2002. – 608 с.

- Максфилд К. Проектирование на ПЛИС. Курс молодого бойца. – М.: Издательский дом «Додэка-XXI», 2007. – 408 с.

- Баркалов А.А., Титаренко Л.А. Синтез микропрограммных автоматов на заказных и программируемых СБИС. – Донецк: ДонНТУ, Технопарк ДонНТУ УНИТЕХ, 2009. – 336 с.

- Nelson V., Nagle H., Carroll B., Irwin D. Digital logic circuit analysis and design. – Prentice Hall, 1995. – 842 p.

- Баркалов А.А. Синтез устройств управления на программируемых логических устройствах. – Донецк: ДонНТУ, 2002. – 262 с.

- XST User Guide (9.2i), Xilinx.