Руководство пользователя SOPC Builder

Автор: "Altera

Corporation"

Источник (англ.):

Источник

оригинальной статьи

Переводчик: Деменко

А. Г.

Автор: "Altera

Corporation"

Источник (англ.):

Источник

оригинальной статьи

Переводчик: Деменко

А. Г.

SOPC Builder представляет

собой мощный инструмент разработки систем.

SOPC Builder позволяет создать полную

систему на программируемом

чипе (SOPC) за гораздо меньший временной промежуток, чем при

использовании традиционных, ручных

методов интеграции. SOPC Builder включен

в качестве части программного обеспечения

Quartus II.

Возможно,

вы

использовали SOPC Builder для создания

систем на базе

процессора Nios ® II.

Однако, SOPC Builder - это

более чем

просто утилита для Nios II, это общего назначения инструмент для

создания систем, которые

могут содержать или не содержать процессор, и могут

включать в себя также программный

процессор, кроме собственного

процессора Nios II.

SOPC Builder автоматизирует задачи интеграции аппаратных компонентов на плату. Используя традиционные методы проектирования, необходимо вручную писать HDL модули для соединения различных частей системы. Используя SOPC Builder, необходимо указать компоненты системы в GUI Builder, и SOPC генерирует логику соединения автоматически. SOPC Builder генерирует HDL файлы, которые определяют все компоненты системы, и верхнего уровня HDL файл, который соединяет все компоненты. SOPC Builder может генерировать файлы либо на языке Verilog HDL, либо на VHDL в равной степени.

Архитектура системы SOPC Builder

SOPC Builder - модуль для разработки, который SOPC Builder распознает и может автоматически интегрировать в систему. Вы также можете определять и добавлять пользовательские компоненты, выбирать их из списка предоставляемых компонентов. SOPC Builder соединяет несколько модулей, чтобы создать верхнего уровня HDL-файл в качестве системного файла SOPC Builder. SOPC Builder производит (генерирует) фабрику системных межсоединений, которая содержит логику для управления возможностями соединения всех модулей в системе.

Модули SOPC Builder

Это

определение относится

к компонентам как определение класса модуля, например,

Nios ®

II процессор. Экземпляр параметризации - это

компонент, который был

добавлен к системе, например cpu_0.

Модули SOPC Builder являются строительными

блоками для создания

системы. SOPC Builder модули

используют Avalon ® интерфейсы,

такие как Мemory-mapped (отображение в память), потоковый

и IRQ (прерывания) для физического

соединения компонентов. Вы

можете использовать SOPC Builder для подключения

любого логического

устройства (либо на кристалле, либо вне него),

который имеет интерфейс

Avalon. Существуют различные типы интерфейсов Avalon,

они описаны в соответствующей

технической документации.

Altera и

сторонние разработчики предоставляют готовые к

использованию SOPC Builder компоненты,

такие как:

■ Микропроцессоры,

например процессор Nios II;

■ микроконтроллеры периферийных

устройств, например Scatter-Gather

DMA контроллер и таймер;

■ Последовательный

интерфейс связи, такой

как UART и последовательный

периферийный интерфейс (SPI);

■ Компоненты общего назначения,

ввода-вывода (I / O );

■ Периферийные

устройства связи, такие

как 10/100/1000 Ethernet MAC;

■ Интерфейсы устройств, которые

вне кристалла.

Вы можете

импортировать HDL модули и HDL-entity, которые

написаны с использованием Verilog

HDL или

VHDL, в SOPC Builder

как пользовательские

компоненты. Вы

можете использовать следующие

средства разработки для

интеграции пользовательской логики в

систему SOPC Builder:

1. Определение интерфейсов,

используемых для взаимодействия с пользовательским компонентом;

2. Создание

компонента логики, используя языки HDL;

3. Использование редактора

компонентов SOPC Builder для создания SOPC Builder компонента

с вашими

файлами HDL;

4. Создание

экземпляра компонента в

системе.

Как только вы создали компонент SOPC Builder, вы можете использовать его в других системах SOPC Builder, а также передавать этот компонент другим группам разработчиков.

Вы также можете использовать готовые компоненты SOPC Builder, которые были разработаны третьими сторонами. Altera поощряет наградами готовые сертификации IP-функций, которые готовы к интеграции со встроенным процессором Nios II или с фабрикой системных межсоединений через SOPC Builder. Эти ядра поддерживают Avalon-ММ-интерфейс или потоковый Avalon-интерфейс (Avalon-ST), и могут включать в себя ограничения, программные драйверы, моделирование моделей, а также эталонные конструкции, когда это применимо.

Функции SOPC Builder.

Определение и генерация системного аппаратного

обеспечения

SOPC Builder позволяет

проектировать структуру аппаратной системы. GUI

позволяет

добавлять компоненты системы,

настройки компонентов, а также указывать

подключения. После

добавления и параметризации каждого из

компонентов,

SOPC Builder генерирует фабрику

системных

межсоединений, и

выводит HDL-файлы в каталог проекта. Во

время генерации

системы, SOPC Builder создает следующие

файлы:

■ HDL-файл для верхнего

уровня и

для каждого компонента в системе SOPC Builder.

HDL-файл верхнего

уровня

называется <system_name>. v для

проектов Verilog-HDL и

<system_name>.vhd

для

конструкций VHDL;

■ Synopsis Design

Constraints file (.sdc)

для временного

анализа;

■ Block Symbol File (.bsf)

- представление верхнего уровня системы SOPC

Builder для использования в Quartus

II Block Diagram Files

(.BDF);

■ пример экземпляра

HDL-файла верхнего уровня,

<SOPC_project_name_inst>.V

или <SOPC_project_name_inst>. VHD,

который показывает, как

создан экземпляр HDL-файла верхнего уровня в вашем коде;

■ спецификации, называемые <system_name>. HTML,

что обеспечивает обзор системы, в том

числе предоставляет следующую

информацию:

■

Все внешние

подключения для системы;

■ Мemory

Мap с

указанием адреса каждого Avalon-MM Slave по

отношению к каждому Avalon-MM

Мaster, к которому он подключен;

■ Все

назначения

параметров для каждого компонента;

■ функциональные test

bench

для SOPC Builder и системы

ModelSim ® моделирования файлов

проекта;

■ файл

информации SOPC

(. Sopcinfo), описывающий все компоненты и

соединения в системе. Этот файл представляет

собой полное

описание системы, и используется нижестоящими инструментами,

такими как

инструмент цепи Nios II. В

нём также описываются параметризации каждого из

компонентов в системе,

следовательно, Вы можете разобрать его содержание,

чтобы получить его требования при разработке программного

обеспечения драйверов для компонентов SOPC Builder;

■ IP Quartus

II файл

(. QIP), который предоставляет Quartus

II всю необходимую информацию

о вашей системе SOPC

Builder. QIP-файл содержит ссылки на следующую

информацию:

■ HDL файлы,

используемые в системеBuilder SOPC;

■ TimeQuest тайминг Analyzer Synopsys Design

Constraint файл(. SDC);

■ Файлы

описания компонентов для

архивирования;

После создания системы в SOPC Builder, вы можете скомпилировать её в Quartus II, или подключить его в другую FPGA-систему.

Создание Memory

Map для разработки

программного обеспечения

Когда

система SOPC Builder включает

в себя процессор Nios

II, SOPC Builder генерирует файл

заголовка cpu.h, что обеспечивает базовый

адрес каждого Avalon-MM Slave

компонента. Кроме того,

каждый Slave-компонент

может предоставлять программные драйверы, библиотеки

и другие программные

функции для процессора. Вы можете

создать заголовочные C-файлы для вашей

системы с помощью утилиты

sopc-create-header-files.

Создание имитационной

модели и Test Bench

Вы

можете моделировать систему

после её генерирования при

помощи SOPC Builder. Во время

генерации

системы SOPC Builder создаёт

скрипты test bench и

системы моделирования ModelSim, которые облегчают

работу.

Тest bench выполняет следующие действия:

■ Подтверждает правильность

созданной в SOPC Builder системы;

■ Управляет всеми

синхросигналами и сигналами сброса;

Процесс разработки в SOPC Builder

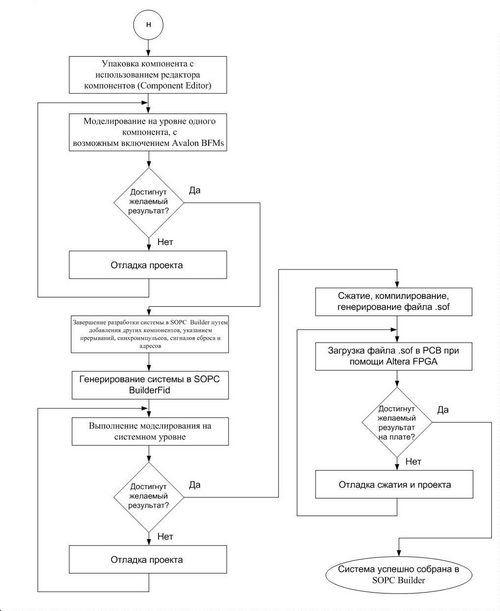

На

рисунке 1 показан

пример «восходящего»

проектирования

SOPC Builder, которое начинается с разработки

компонента. Как

эта схема показывает, типичный ход дизайна

включает

в себя следующие действия высокого уровня:

1. Упаковка компонента для SOPC Builder

с использованием редактора компонентов (Component Editor);

2. Моделирование на уровне

одной единицы (компонента), с

возможным включением Avalon BFMs для

проверки (верификации) системы;

3. Завершение разработки системы

в SOPC Builder путем

добавления других компонентов, указанием прерываний,

синхроимпульсов, сигналов

сброса и адресов;

4. Генерирование системы в

SOPC Builder;

5. Выполнение моделирования на

системном уровне;

6. Сжатие

(оптимизация) и завершение

разработки;

7. Загрузка

готовой системы в устройство Altera;

8. Испытание на

аппаратном

уровне.

В альтернативном

«нисходящем» проектировании разработку

начинают с проектирования системы

в SOPC Builder, а затем определяют и

подтверждают пользовательский

компонент SOPC Builder. Такой

подход уточняет требования к

системе ещё в начале процесса проектирования.

Рисунок 1 – Процесс разработки в SOPC Builder