Назад в библиотеку

Методология для продвинутой верификации блокового уровня

Авторы: Ashish Aggarwal, Ravindra K. Aneja, Mentor Graphics

Оригинальное название: A methodology for advanced block level verification

Перевод: Горохов И.В., студент 5-го курса ДонНТУ Компьютерные системы и сети

Источник: http://lyris.mentor-info.com/...

Содержание

Аннотация

Aggarwal A., Aneja R. Методология для продвинутой верификации блокового уровня. Эта статья описывает процесс для продвинутых методов верификации на уровне блоков. Вопросы разработки и верификации можно разделить на четыре основные категории, каждой из которых мы кратко коснемся в этой статье: RTL разработка, верификация стандартных протокольных интерфейсов, верификация end-to-end

с использованием среды, базирующейся на моделировании, эффективное управление метрикой покрытия.

Введение

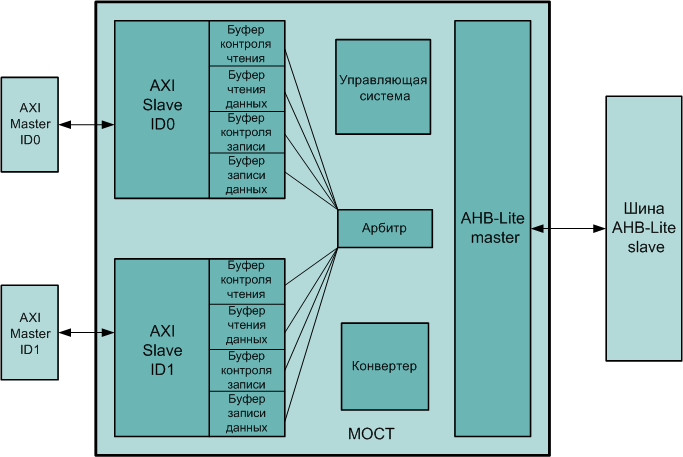

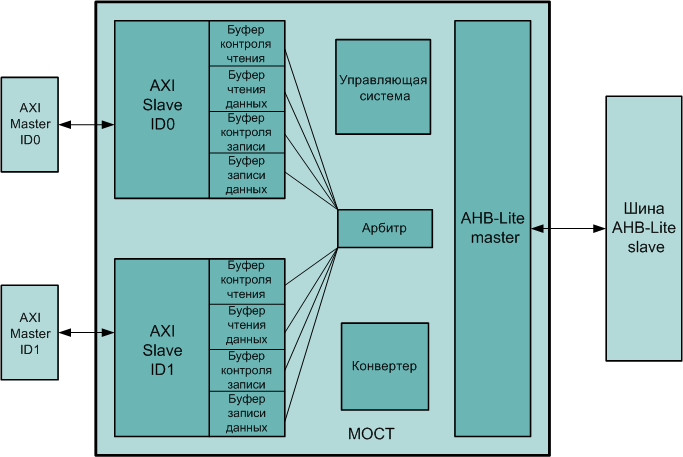

Проект, используемый в качестве примера, это мост между стандартными AMBA шинами AXI4 и AHB-lite. Модель и ход верификации показан на рис. 1.

Рисунок 1 — Модель и ход верификации

Модульные связи для этого блока показаны на рис. 2. (Обратите внимание, что реакция буферов мастеров AXI4 и декодеров моста были опущены для ясности).

Рисунок 2 — Блоковая диаграмма тестируемого проекта

Основные особенности этого моста:

- Настраиваемое межсоединение, включающее:

- Множественные мастера AXI4 и множественные ведомые устройства AHB-lite;

- Настраиваемая ширина шин адреса и данных;

- Настраиваемое количество выдаваемых адресов;

- Настраиваемая глубина различных буферов.

- Неупорядоченные мгновенные транзакции AXI4 на чтение и запись

- Узкие шинные передачи AXI4

- Отображаются все виды типов мгновенных передач AXI4

- Множественное чтение и запись AXI4 выдаваемых адресов

- Идентификаторы адресов AXI4 используются в транзакциях на чтение и запись

- Вставка циклов ожидания AHB-lite и обработка ошибочных реакций

- Циклическая схема арбитража

- Сгенерированные типы ошибок AXI4 — OKAY, SLVERR, DECERR

1 RTL разработка

Проблемы:

- Верификация того, что разрабатываемая концепция была правильно промоделирована

- Построение use-andt-hrow проверочного testbench для каждого RTL блока в заданный промежуток времени

Необходим инструмент, который может помочь:

- Интеллектуально проанализировать синтезабельный RTL код

- Автоматически сгенерировать проверки и утверждения

- Проверить эти сгенерированные утверждения

- Сообщить о нарушениях для быстрой и эффективной отладки

Некоторые из наиболее часто используемых проверок — переполнение регистров, тупиковые ветви управляющих автоматов, комбинационные зацикливания, недостижимый код. Выполнение этих проверок поможет разработчику позаботиться о проблемных вопросах на ранних стадиях RTL проектирования, таким образом, снизив вероятность того, что ошибки RTL кодирования превратятся позже в нечто большее в последующих циклах разработки и верификации.

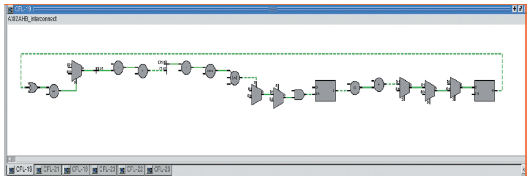

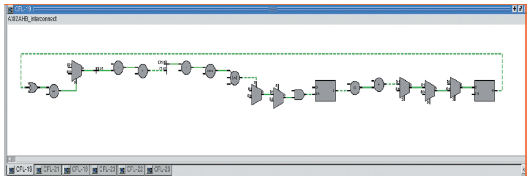

Questa AutoCheck

Questa AutoCheck анализирует синтезированный RTL и проверяет в общем ошибки кодирования RTL. Среди многих ошибок, сообщенных на ссылаемый блок, критическим было наличие комбинационной петли. Целью было моделирование триггера, срабатывающего по фронту, но RTL кодирование смоделировало защелку. Этот вид ошибки не может быть пойман симулятором. Questa AutoCheck обеспечивает удобный интерфейс отладки, как показано на рис. 3.

Рисунок 3 — Интерфейс Questa AutoCheck сообщает о комбинационной петле

2 Верификация стандартных протоколов

Проблемы:

- Верификация правил стандартного коммуникационного интерфейса и правил протокола

- Длительный характер построения testbench (который, вероятно, не сможет быть использован позже) для определенного интерфейса

- Получение достигнутых результатов верификации для способствования общему верификационному покрытию

- Исчерпывающая верификация правил протокола

Необходим инструмент, который может помочь:

- Подтвердить данный RTL код, содержащий интерфейс протокола по отношению к указанным SystemVerilog (SV) утверждениям; эти утверждения включают временные требования и последовательность квитирования для различных сигналов

- Исчерпывающе проверить пространство состояний проекта для нахождения ошибок протокола

Questa Formal

Questa Formal воздействует на синтезированные RTL и SV утверждения; которые представляют собой правила протокола для данного интерфейса (AXI и AHB для данного ссылаемого проекта). Для хорошо документированных интерфейсов как протоколы AMBA, эти свойства предоставляются как часть Questa Formal Verification IP библиотеки.

Questa Formal нашло следующие ошибки на ранней стадии в цикле проектирования:

- Мастер AHB завершал пакеты INCR16 до окончания 16 отсчетов

- HADDR и HSIZE мастеров AHB не были должным образом инициализированы в результате неупорядоченных передач

- Мастер AHB генерировал адреса, которые пересекали границу 1 Кб

3 Верификация end-to-end

с использованием среды, базирующейся на моделировании

Проблемы:

- Генерация различных тестовых стимулов для проявления различных особенностей тестируемого устройства, используя тот же testbench

- Управление большими избыточными тестами и медленное покрытие хода CRT

- Реализация генерации реактивных и автоматизированных стимулов

- Реализация легко создаваемой, модульной, многократно используемой и расширяемой testbench среды

- Обеспечение высоко конфигурируемого тестового окружения

end-to-end

проверка данных- Верификация протокола интерфейса коммуникации

- Измерение прогресса верификации

Существует много ядер верификации (VIP — Verification IP) протоколов, которые могут быть интегрированы в testbench. Такие стандартные методики как OVM/UVM обеспечивают простое подключение ядра верификации в testbench среду.

Среди важных требований к ядрам верификации следует отметить следующие:

- Автоматизация исчерпывающего потока различных входных стимулов для проявления функциональности тестируемого устройства

- Предоставление ссылаемой (эталонной) модели, которая может быть использована для верификации выходных сигналов тестируемого устройства, когда применяются одинаковые стимулы

- Предоставление проверщиков протокола

- Предоставление механизма регистрации верификации для отслеживания хода верификации

- Предоставление пользовательского интерфейса для быстрой отладки. Там должна быть автоматизация группировки данных с шинного интерфейса для той же транзакции

Questa Verification IP

Структура testbench в Questa VIP базируется на OVM/UVM, таким образом, обеспечивает простую интеграцию в любые OVM/UVM testbench.

Эти VIP оборудованы:

- Анализирующими компонентами, такими как табло и сборщики покрытия

- Мониторами и проверщиками протокола

- Функциональным тестовым планом

- Последовательностями, направленными на достижение 100% покрытия предоставляемых тестовых планов и покрывающих контейнеров

Тестовые планы и последовательности этих VIP являются иерархическими и могут быть повторно использованы для testbench уровня System-on-Chip (SoC).

Используя компоненты Questa VIP для AXI4 и AHB мы очень быстро разработали верификационный end-to-end

testbench. Среди ошибок, найденных верификацией end-to-end

были:

- Ошибки в неупорядоченных фиксированных транзакциях AXI4; это было отражено на AHB транзакции одиночных пакетов на те же неупорядоченные адреса всегда без инкрементирования адреса в следующем изменении упорядоченного адреса

- Ошибки Wrap транзакций длиной 2 в AXI4; они были дважды сопоставлены к AHB одиночными пакетами по одному и тому же адресу

Архитектура testbench показана на рис. 4.

Рисунок 4 — Архитектура верификационного testbench

Шинные транзакции или пакеты могут быть визуализированы в качестве waveform, что помогает значительно уменьшить усердия и время, необходимые для отладки.

Questa inFact

Questa inFact обеспечивает эффективный способ написания сложных последовательностей. Некоторые из уникальных особенностей Questa inFact:

- Автоматизация процесса уникальной генерации стимулов

- Ускорение верификационного покрытия проекта

- Генерация тестовых стимулов в различных форматах и поддержка для ovm_sequences и других форматов

- Бесшовная интеграция с VIP Questa для генерации сложных последовательностей

- Простой BNF синтаксис для входного файла правил для спецификации различных узлов действий и их отношений (последовательность или чередование) для протокольных последовательностей

- Повторное использование существующих testbench

Использование Quest inFact помогло ускорить моделирование в 15 раз с достижением той же суммы покрытия. Quest inFact сгенерировало 394 уникальные транзакции; CRT сгенерировало 1200 транзакций для достижения того же покрытия.

4 Эффективное управление метрикой покрытия

Проблемы:

- Управление и выделение ресурсов для реализации и проверки различных особенностей проекта

- Отслеживание изменений с момента создания проекта

- Управление повторяющимися заданиями, такими как компиляция, моделирование с помощью различных тестов и различных отборов, слияние и анализ на наличие ошибок на ферме регрессии

Требуется решение, которое отслеживает путь прогресса верификации, наряду с оптимизацией базы данных по историческому/трендовому анализу и группирует сообщения из log-файла чтобы помочь в назначении приоритетов ошибкам/проблемам.

Questa Verification Management (VM)

Questa VM обеспечивает эффективное покрытие проверки и предоставляет полный набор функций для управления метрикой покрытия. Среди таких особенностей:

- Слежение тестового плана, которое может быть импортировано в Questa VM и слито с покрытием данных для генерации базы данных отслеживания, которая, в свою очередь, может быть загружена в окно трекера Questa; из окна трекера можно запросить такие вещи как несвязанные разделы тестового плана, несвязанные функциональные группы покрытия, неответственные тесты и прочее

- Анализ тенденций, которые помогают в понимании прогресса верификации с течением времени

- Сортировочный анализ, который фильтрует сообщения из log-файла по важности, составной части, времени и подобным факторам

- Менеджер запуска верификации, который обеспечивает регресс основы для компиляции, моделирования и анализа

Для ссылаемого проекта было использовано только отслеживание тестового плана.

Выводы

На рис. 5 изображены различные этапы блокового проектирования/верификации и инструменты, доступные в платформе Questa, которые повышают продуктивность и помогают управлять всем процессом проектирования.

Рисунок 5 — Отображение потока проектирования с технологиями платформы Questa

Ссылки

- OVM Userguide, доступно на www.verificationacademy.com

- Glasser, Mark (2009) Open Verification Methodology cookbook, доступно на www.verificationacademy.com