| Разработка системы реального времени на базе комплекса VIRTEX‑5 FPGA ML501 | ||||||

| Информация | ||||||

|

||||||

| Введение | ||||||

|

Современные предприятия и организации оборудованы большим количеством различной аппаратуры, значительную часть которой занимают компьютеры или терминалы, а также серверы для хранения данных. Даже при нынешнем уровне развития технологий существует проблема внезапного выхода из строя оборудования в связи с такими факторами как перегрев, повышенный уровень влажности, запыленность. В связи с этим появляется необходимость постоянно контролировать и учитывать данные факторы. Хотя большинство типов оборудования следует проверять и обслуживать в зависимости от его технических характеристик, все же было бы лучше не допускать поломок и предотвращать их заранее. В соответствие с этим появляется необходимость поддерживать благоприятные условия для работы оборудования и механизмов предприятия. Для этого следует использовать датчики различных видов и снимать с них показания через определенный равный промежуток времени. Показания датчиков будут поступать во входной интерфейс устройства считывания и контроля данных. Такие устройства считывания и контроля следует распределить по всему предприятию так, чтобы выход из строя одного из них не привел к критической ситуации. Преобразованная информация с устройств контроля будет поступать на коммутатор или маршрутизатор, а далее на терминал пользователя. В данном случае пользователь терминала не может повлиять на процесс работы любого из устройств контроля. Он просто следит за правильностью работы и своевременным принятием решений устройствами. Устройство контроля в свою очередь при получении каких-либо данных от датчиков принимает решение о том, задействовать или не задействовать на данном этапе работы исполнительный механизм, регулирующий работу в данной зоне. В случае необходимости исполнительный механизм приводит условия работы оборудования к допустимым. Такой порядок работы системы объясняется тем, что в действительности на предприятиях и организациях за всем может следить только один человек, например, охранник или смотритель, который может не иметь знаний в области датчиков, компьютеров и того множества оборудования, которое используется в процессе производства, а также не иметь времени на то, чтобы включать и выключать сотни исполнительных механизмов. |

||||||

| Общие принципы проектируемой СРВ | ||||||

|

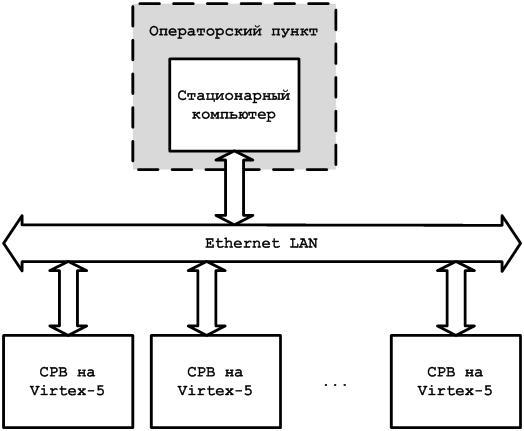

Структурная схема проектируемой системы изображена на рисунке 1. В общем случае всю систему можно разбить на три части:

Основой данного проекта является комплекс FPGA Virtex‑5 ML501, который позволяет считать данные с датчиков в порт и передать сигнал о начале работы исполнительному механизму. Данный комплекс позволяет задать довольно большую частоту дискретизации опроса, что значительно расширяет круг возможностей и видов используемых датчиков. На базе Virtex‑5 строятся системы высокой производительности, что важно при проектировании систем реального времени. Отладочная плата содержит все необходимые интерфейсы и устройства для реализации данного проекта, а именно порт RS‑232 и Ethernet 10/100 PHY. В качестве датчиков будут использованы датчики температуры DS18B20 или подобные, например, LM235, LM335, подключенные через схему согласования к порту RS-232 комплекса Virtex‑5. DS18B20 является цифровым датчиком с диапазоном от -55 до +125 градусов, точностью в полградуса и довольно высоким разрешением (от 9 до 12 бит), который передает данные посредством однопроводного последовательного интерфейса. К каждому FPGA комплексу может быть подключено несколько датчиков, в том числе и различных видов. После ввода и анализа информации об объекте, СРВ управляет исполнительным механизмом, в роли которого выступает простейший шаговый двигатель. При наличии нескольких зон с контролируемыми параметрами среды используются несколько комплексов Virtex‑5. Каждый из них подключаются к локальной сети Ethernet. Для этого им предварительно задаются собственные MAC‑ и IP‑адреса и IP‑адрес компьютера оператора.  Рисунок 1 — Структурная схема системы реального времени на базе комплекса Virtex‑5 |

||||||

| Системы управления и контроля | ||||||

|

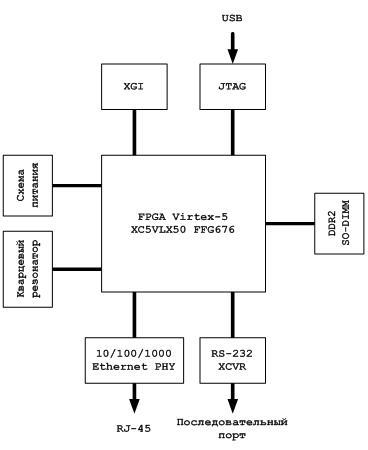

Рассмотрим перечень устройств, необходимых, наряду с самим кристаллом FPGA, для реализации предложенной системы. Структура системы реального времени на базе FPGA Virtex‑5 представлена на рисунке 2.  Рисунок 2 — Структура системы управления и контроля на базе Virtex‑5 Основным устройством в данной структуре является кристалл FPGA Virtex‑5 XC5VLX50 FFG676. Представленная система реального времени должна выполнять контроль температуры, поэтому для обеспечения полной функциональности в структуру включены следующие дополнительные схемы и интерфейсы:

Схема электропитания предназначена для генерации необходимых уровней напряжения и подачи его на схемы, входящие в данную структуру. Кварцевый резонатор является источником синхросигналов, обеспечивающих согласованное взаимодействие FPGA и дополнительных схем данной структуры. Дополнительная память DDR2 SO‑DIMM необходима, так как блока памяти, встроенного в кристалл (32Кб), недостаточно для реализации всей функциональности проектируемой схемы. Устройство 10/100/1000 Tri‑Speed Ethernet PHY занимается передачей пакетов в операторский пункт. Для подключения используется интерфейс RJ‑45. Последовательный порт RS‑232 необходим для приема и передачи последовательных данных с датчика температуры с дискретностью, определенной требованиями системы. Интерфейс XGI предназначен для соединения с исполнительным механизмом — шаговым двигателем, управляющим системой охлаждения. Порт JTAG предназначен для конфигурирования, программирования и отладки FPGA. Через интерфейс JTAG данная система подключается к USB-порту компьютера с целью ее прошивки и тестирования. |

||||||

| Ядро FPGA Virtex-5 | ||||||

|

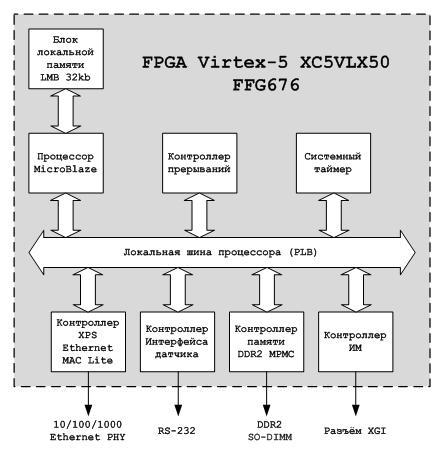

Далее выполним более подробное рассмотрение структуры самого кристалла FPGA Virtex‑5, представленной на рисунке 3.  Рисунок 3 — Общая структура Virtex‑5 Центральным устройством в данной структуре является процессор MicroBlaze. Это программный 32‑битных процессор RISC архитектуры. Он экономно потребляет место на кристалле. При его конфигурировании можно выбирать только ту функциональность, которая необходима для реализации поставленной задачи. Процессор программируется на языке С. Преимуществом данного выбора является также размещение микропроцессора на одном кристалле с другими устройствами, реализуемыми в FPGA, что ускоряет их совместную работу. Кристалл снабжен блоком локальной памяти объемом 32Кб. Данный блок используется для хранения конфигурационной информации о процессоре, но для полноценной работы системы его недостаточно. Для подключения локальной памяти используется специализированная шина LMB (Local Memory Bus). По причине того, что процессор не может управлять всеми необходимыми устройствами самостоятельно, в систему включены:

Последние два контроллера отличаются от остальных тем, что не предоставлены в качестве уже готовых IP‑ядер, а разрабатываются отдельно. Т.е. их функциональное наполнение полностью зависит от разработчика и при необходимости может быть с легкостью дополнено или изменено. Подключение процессора ко всем контроллерам и внутренним устройствам выполняется посредством шины PLB. Это 128‑битная шина, предназначенная для коммутации произвольного количества устройств, каждое из которых может выступать как Master или Slave. Шина поддерживает возможность арбитража между Master устройствами, работает в 32-х, 64-х и 128-и разрядном режимах, поддерживает работу в режиме разделения шины и в режиме точка-точка. В представленной системе единственным Master-устройством будет являться процессор MicroBlaze. Для передачи данных по шине необходимо каждому устройству задать свой диапазон адресов. Схема системы реального времени на основе FPGA Virtex‑5 имеет преимущества перед аналогичными по функциональности схемами с использованием персональных компьютеров, так как стоимость представленного комплекса устройств будет значительно снижена. Схема является гибкой и легко расширяемой в случае необходимости добавления дополнительной функциональности. Достаточно лишь добавить соответствующее IP‑ядро для работы с новым устройством. Система не привязана жестко к конкретному датчику или исполнительному механизму. В случае необходимости замены одного из них на другую модель, достаточно лишь изменить IP‑ядро контроллера интерфейса датчика или исполнительного механизма. Остальная же часть системы останется незатронутой. |

||||||

| Выводы | ||||||

|

Предлагаемая система реального времени позволяет автоматизировать процесс управления температурным режимом компьютерных систем в масштабах здания или предприятия, централизовать наблюдение за процессом на одном операторском ПК и в случае обнаружения критических ситуаций быстро локализовать точку неисправности для оперативного принятия мер. |

||||||

| Литература | ||||||

|

[1] ML501 Evaluation Platform User Guide(v1.4) August 24, 2009 [2] Сайт производителя FPGA, компании Xilinx. Электронный ресурс. — Режим доступа: http://xilinx.com [3] PLBV46 Interface Simplifications (v1.0) October 11, 2007 [4] MicroBlaze Processor Reference Guide Embedded Development Kit 13.3 |