| Диагностика и обнаружение неисправностей в аналоговых интегральных схемах с использованием искусственных нейронных сетей на основе схемы псевдослучайного тестирования | ||||||||

| Информация | ||||||||

|

||||||||

| Аннотация | ||||||||

|

В данной статье рассматривается свойство белого шума, заключающееся в том, что его автокорреляция является дельта-функцией Дирака. Предложенная схема тестирования использует псевдослучайный шум в качестве входных стимулов, обеспечивая хорошее распознавание импульсных ответов тестируемой цепи (предположительно стабильно работающей). Методология основана на использовании моделируемого эталона, реализованного при помощи опережающих нейронных сетей с целью обнаружения неисправностей и диагностики аналоговых интегральных схем. Данная методика может рассматриваться в качестве встроенного самотестирования наряду с контролепригодным проектированием, значительно повышающими тестовое покрытие неисправностей и может быть реализована как в оперативном (подключенном) режиме, так и автономно в зависимости от нужд приложения и издержек микросхем. Главное преимущество данной методики заключается в использовании универсальных входных стимулов (белого шума), что позволяет упростить процесс генерации тестов. При этом исправные и ошибочные сигнатуры для проверки качества на высоком уровне формируются значительно легче, а стоимость тестирования снижается. |

||||||||

| 1. Введение | ||||||||

|

В связи с растущей сложностью и сокращением размеров устройств, свойства интегральных схем (ИС) становятся все более чувствительными к заложенным на стадии производства отклонениям параметров. Следовательно тестирование становится одним из главных стоимостных факторов на протяжении всей стадии производственных затрат. Целью тестирования является устранение тестовых неточностей и сокращение количества работоспособных устройств, идентифицированных как негодные тестовой программой. Методики контролепригодного проектирования (КПП) и встроенного самоконтроля (ВСК) аналоговых и аналогово-цифровых схем уже привлекли определенный интерес и должны помочь сократить трудности, связанные с тестированием. Существует очевидная необходимость снижения стоимости тестирования систем на кристалле с помощью ВСК, а также совершенствования тестового покрытия и обеспечения контролепригодного проектирования. В большинстве случаев ВСК основан на оптимизации КПП на различных уровнях. Многие авторы [1,2] уже обсуждали аналоговые решения с использованием методики КПП в своих работах. Другие интересные техники, такие как способность распознавания образов искусственными нейронными сетями (ИНС) с целью диагностики неисправностей [3,4], мониторинг токов утечки с целью тестирования аналоговых и аналого-цифровых устройств путем контроля источника питания, тоже являются привлекательными направлениями в данной области. Методика ВСК, предложенная в источниках [8,9], касается в основном оперативного тестирования. Однако, в связи с предельно допустимыми размерами микросхем, эти техники подходят только для высококлассных приложений. В источнике [10] Сламани обсуждает технику автономного ВСК. Мы отталкиваемся от использования псевдослучайного генератора шума как генератора тестовых шаблонов с целью диагностики аналоговых ИС и моделируемого контрольного устройства с целью обнаружения неисправностей [11]. Контрольное устройство в данном случае реализовано в качестве многоуровневой опережающей ИНС, обученной при помощи алгоритма обратного распространения ошибок (ОРО). |

||||||||

| 2. Стратегия тестирования | ||||||||

|

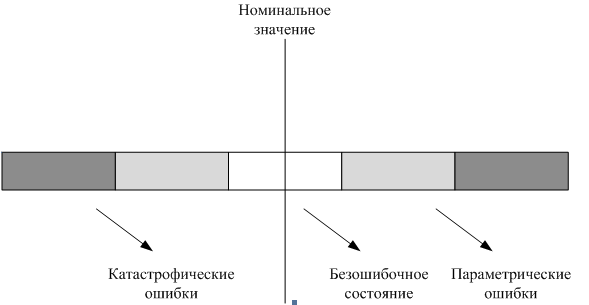

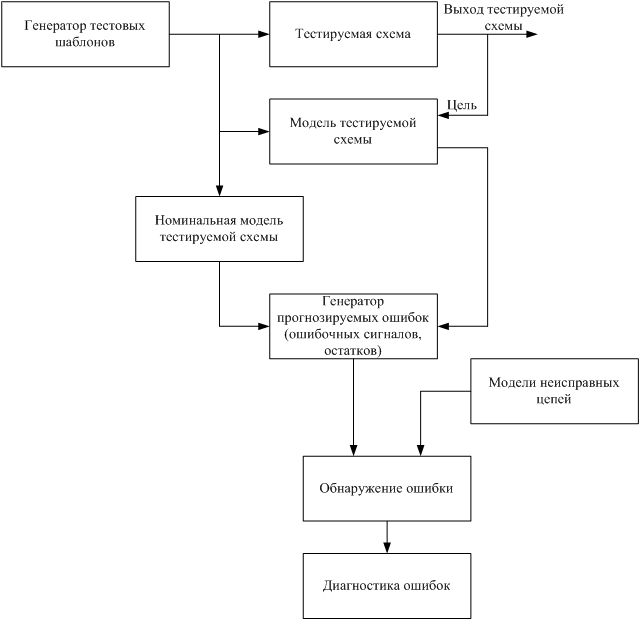

Неисправности аналоговых ИС могут быть как катастрофическими, так и параметрическими. В большинстве случаев причиной первых является физический дефект, который изменяет топологию чипа (короткое замыкание), а причина вторых вызвана колебаниями параметров устройства. В общем случае чип, подверженный катастрофическим неисправностям, является полностью неработоспособным и, следовательно, такие неисправности легко обнаружить. С другой стороны чип, подверженный параметрическим ошибкам, будет по-прежнему функциональным, но производительность будет снижена. Существует зона приемлемого поведения вблизи номинального значения. За пределами этого региона производительность не соответствует техническим требованиям, однако не вызывает полного отказа цепи. Наконец существуют ошибки, приводящие к выходу схемы из строя. Следовательно, таксономия аналоговых неисправностей может быть представлена, как показано на рисунке 1. Поэтому необходимо выбирать подмножество неисправностей, которое наиболее полно соответствует списку вероятных причин отказа.  Рисунок 1 — Таксономия аналоговых неисправностей В данной статье мы предлагаем технику тестирования неисправностей на основе модели, которая требует простого измерения выходных значений. Главный подход данного диагностического метода заключается в сравнении тестируемой цепи с математической моделью цепи, не содержащей ошибок, реализованной с использованием обычной многоуровневой ИНС, обученной методом ОРО. Предложенная стратегия основана на возбуждении тестируемой при помощи псевдослучайного шума (ПСШ) аналоговой ИС с последующим измерением кратковременных ответных сигналов на ее выходных ножках. Предполагается, что тестируемая схема будет выходить за пределы линейного режима работы, для которого она тестируется, что побуждает использовать широкий спектр шума с постоянными величинами на всем диапазоне частот. Другое преимущество ПСШ в том, что это позволит производить диагностику через главные входы и выходы тестируемой схемы, что позволит снизить количество дополнительной схемотехники, необходимой при введении управляющих и эталонных участков при КПП схемы. Рисунок 2 отображает предложенную систему диагностики неисправностей аналоговых ИС, использующих моделируемое обнаружение ошибок схемы и их изолирование [12,13].  Рисунок 2 — Отображение предлагаемой стратегии тестирования Процедура предложенной диагностики неисправностей аналоговых ИС с использованием моделирования может жестко быть разделена на следующие три стадии:

Первая стадия включает определение различных классов неисправностей. Тестируемая схема симулируется с использованием псевдослучайного шума, который используется в качестве тестовых стимулов для каждого выбранного класса ошибок. Выходной ответ тестируемой схемы формирует сигнатуры для данного класса ошибок. Для генерации прогнозных ошибок требуется три типа моделей: номинальная, фактическая (действительная) и модель с тестируемым неисправным участком. Для реального представления важно промоделировать все эффекты, которые могут так или иначе повлиять на обнаружение неисправностей. Все модели создаются с использованием обычных многоуровневых ИНС, состоящих из входного уровня, одного или двух скрытых уровней и одного выходного уровня. Модели ИНС обучаются с помощью алгоритма ОРО с целью вывода ответов тестируемого устройства при различных условиях возникновения неисправностей, включая безошибочный вариант. Модель ИНС без ошибок обеспечивает допустимое отклонение параметров компонент и представляет собой номинальную. Разница между выходами номинальной и действительной моделью тестируемой схемы генерирует необходимые прогнозные ошибки. Когда неисправности нет, две модели (номинальная и действительная) демонстрируют близкое поведение, что в итоге формирует незначительно малые остатки. В условиях возникновения неисправностей система генерирует прогнозные ошибки, показывая, как сильно действительная схема отличается от схемы без ошибок. Любая ошибка в цепи, катастрофическая или параметрическая, изменяет сигнатуру прогнозной ошибки. Эти остаточные сигнатуры неисправностей, известные как ошибочные сигнатуры, симулируются и сохраняются в памяти модели для дальнейшего использования. Обнаружение и изолирование ошибок включает моделирование действительной тестируемой схемы, генерацию прогнозируемых ошибок и сравнение их с различными ошибочными сигнатурами, которые хранятся в памяти модели. В зависимости от особенностей приложения, количество особых ошибочных сигнатур, хранящихся в модели, может варьироваться от нуля до сотен. Предположения относительно общих ошибочных сигнатур дают преимущество быстрого, предопределенного ответа для таких неисправностей. Это объясняет надежность методологии. |

||||||||

| 3. Результаты тестирования | ||||||||

|

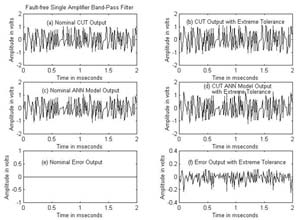

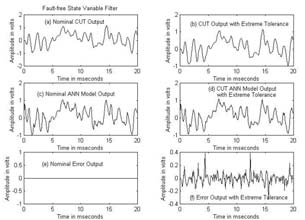

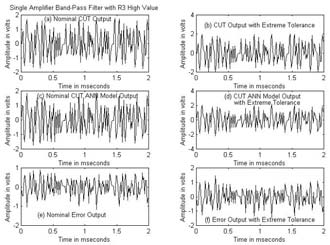

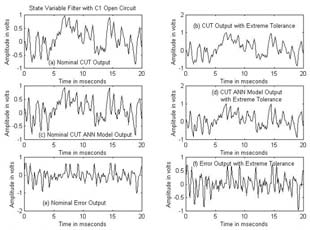

В попытке объяснить предложенную тестовую методику в качестве примеров мы выбрали операционный усилитель (ОУ) Fairchild ?A741, универсальный усилительный полосовой фильтр [3], операционный КМОП усилитель и аналоговый перестраиваемый фильтр из каталога стандартных аналоговых и аналого-цифровых схем IEEE [14]. Операционные усилители широко используются в качестве блоков построения для многих аналоговых проектов и, поэтому, тестируемость заслуживает тщательного исследования. 3.1 Автономные усилители Операционный усилитель используется в форме повторителя напряжения. Всем параметрам назначена статистическая погрешность в ±5%. Количество классов неисправностей зависит от желаемого уровня диагностики. Тестирование типа «годен-негоден» требует всего лишь двух классов: исправного и неисправного. Для полноценной компонентной диагностики требуется большее количество классов неисправностей. Однако не все ошибки должны быть сымитированы. Учитывая это, необходимо исследовать катастрофические неисправности, такие как короткое замыкание и обрыв цепи, параметрические неисправности операционного усилителя ?A741, такие как прямое и обратное ?, емкость перехода, ток насыщения, прямое напряжение, прямое и обратное время распространения и другие, а также операционного МОП усилителя, такие как длина канала, ширина канала, ток насыщения, пороговое напряжение, толщина слоя окислителя и другие. Номинальные значения BJT PSpice параметров ОУ ?A741 были взяты из [15], а усилителя КМОП – с домашней страницы перечня аналого-цифровых схем IEEE http://faculty.washington.edu /manisoma/madtest/benchmarks/. Оба ОУ были промоделированы как повторители напряжения с использованием методов PSpice и Monte-Carlo при различных условиях при наличии и отсутствии ошибок с использованием ПСШ в качестве входных стимулов. С целью получить сигнатуры для тестируемого устройства при отсутствии неисправности были промоделированы компоненты с отклонениями параметров внутри области допустимых значений. Приобретенные в процессе имитации данные были нормализованы и переправлены в среду MATLAB для использования в моделях ИНС и генерации ошибочных сигнатур с использованием инструментов для работы с нейронными сетями. Небольшая многоуровневая ИНС была использована для моделирования классов, как с наличием неисправностей, так и при их отсутствии. Модель ИНС, сгенерированная для работоспособного ОУ, была назначена в качестве номинальной модели тестируемой схемы. Различие между выходами данной номинальной модели, подвергнутой воздействию ПСШ, и выходными значениями любой другой модели ИНС, подвергнутой такому же влиянию, дает ошибочный сигнал, который является прогнозным. Эти ошибочные сигналы или прогнозные сигналы сохраняются в качестве ошибочных сигнатур в памяти модели. 3.2 Внедренные усилители С целью протестировать достоверность предложенной методики для внедренных ОУ были выбраны два варианта, использующие усилитель ?A741. Первый – усилительный полосовой фильтр [3], второй – аналоговый перестраиваемый фильтр [14]. Цепи были промоделированы с использованием методик PSpice и Monte-Carloв условиях отсутствия и наличия неисправностей с использованием ПСШ в качестве входных стимулов. Как было замечено ранее, работоспособные компоненты были промоделированы с отклонениями параметров внутри области допустимых значений с целью получить сигнатуры работоспособного устройства. Выходной ответ полосового и перестраиваемого фильтров показаны на рисунках 3 и 4 соответственно.  Рисунок 3 — Выходной ответ, ответ модели ИНС и выходы работоспособного полосового фильтра  Рисунок 4 — Выходной ответ, ответ модели ИНС и выходы работоспособного перестраиваемого аналогового фильтра При получении данных до симуляции многоуровневая ИНС, обученная методом ОРО, использовалась для моделирования как неработоспособных, так и безошибочных цепей при помощи инструментов для работы с нейронными сетями. Сеть содержит входной уровень, содержащий 1 нейрон с пороговой сигма-функцией, 2 скрытых уровня с 15-ю нейронами каждая с сигмоидальной пороговой функцией и выходной уровень из одного нейрона с линейной пороговой функцией. На полученные модели воздействует ПСШ, значения выходов сравнивается с номинальной работоспособной моделью при аналогичных входных сигналах с целью получить ошибочные сигнатуры. Все эти полученные сигнатуры сохраняются в памяти для последующего соотношения при фактическом тестировании схем. После получения ошибочных сигнатур при известных условиях возникновения неисправностей и сохранения их в памяти модели диагностическая система готова к использованию. Рисунки 3 и 4 также показывают выходы номинальной и работоспособной моделей ИНС, а также номинальные и максимальные значения безошибочных сигнатур полосового и перестраиваемого фильтра соответственно. При обнаружении ошибки во время диагностики устройства ошибочная сигнатура тестируемой схемы сравнивается с отдельными ошибочными сигнатурами, хранящимися в памяти модели с целью классификации неисправности. Примеры выходных ответов, выходов модели ИНС, номинальные и максимальные значения ошибочных сигнатур полосового и аналогового перестраиваемого фильтров изображены на рисунках 5 и 6 соответственно. Полученный авторами результат на стадии моделирования является многообещающим.  Рисунок 3 — Выходной ответ, ответ модели ИНС и выходы неисправного полосового фильтра с повышенным сопротивлением R3  Рисунок 4 — Выходной ответ, ответ модели ИНС и выходы неисправного перестраиваемого аналогового фильтра с разомкнутым конденсатором C1 |

||||||||

| 4. Заключение | ||||||||

|

В данной статье была представлена упрощенная техника диагностики неисправностей аналоговых ИС. В связи с тем, что псевдослучайное тестирование обеспечивает естественный широкополосный тестовый сигнал, проблема генерации тестов полностью устранена и это может быть использовано как универсальное стимулирование при тестировании аналоговых ИС, по крайней мере для тех, которые поддаются небольшому управлению сигналами в хотя бы тестовых условиях. Эффективность предложенной стратегии тестирования зависит от тщательности выбора сигнатур и схем разграничения с целью провести различие между ошибочными и работоспособными устройствами в справочнике неисправностей. Выбранная стратегия успешно протестирована для обнаружения, как отказов, так и сбоев в операционных усилителях и схемах, построенных на их основе. Полученные во время моделирования экспериментальные результаты свидетельствуют о том, что предложенный метод использования наблюдателя, основанного на модели искусственных нейронных сетей, является достаточно надежным. |

||||||||

| Литература | ||||||||

|

[1] M. Soma and V. Kolarik, “A Design-for-Test Technique for Switched-Capacitors Filters”, in Proc. IEEE European Design & Test Conference, Paris, pp. 42-47, 1994.

[2] A.H. Bratt, A.M. Richardson, R.J. Harvey, and A.P. Dorey, “A Design-for-test Structure for Optimising Analogue and Mixed Signal IC Test”, in Proc. European Design and Test Conference,

[3] R. Spina and S. Upadhyaya, “Linear Circuit Fault Diagnosis using Neuro-morphic Analyzers”, IEEE Trans. on Circuits & Systems-II, Vol. CS-44, No. 3, pp. 188-196, 1997. [4] Y. Maidon, B.W. Jervis, N. Dutton and S. Lesage, “Diagnosis of Multi-faults in Analog Circuits using Multilayer Perceptrons”, IEE Proc.-Circuits Devices Syst., Vol. 144, pp. 149-154, 1997.

[5] J. Beasley, H. Ramamurthy, J. Ramirez-Angulo and M. Deyong, “IDD Pulse Response Testing: A Unified Approach to Testing Digital and Analog ICs”, Electronics Letters, Vol. 29, pp. 2101-

[6] D.K. Papakostos and A.A. Hatzopoulos, “Supply Current Testing in Linear Bipolar ICs”, Electronics Letters, Vol. 30, pp. 128-130, 1994. [7] A.K.B. A’Ain, A.H. Bratt and A.P. Dorey, “Testing Analog Circuits by Power Supply Voltage Control”, Electronics Letters, Vol. 30, pp. 214-215, 1994.

[8] C.-L. Wey and S. Krishnan, “Built-In Self-Test (BIST) Structures for Analogue Circuit Fault Diagnosis with Current Test Data”, IEEE Trans. On Instrumentation and Measurement, Vol. 41, No.

[9] L.T. Wurtz, “Built-In Self Test Structure for Mixed-Mode Circuits”, IEEE Trans. On Instrumentation and Measurement, Vol. 42, No. 1, pp. 25-29, 1993.

[10] M. Slamani, B. Kaminska and G. Quesna, “An Integrated Approach for Analog Circuit Testing with a Minimum Number of Detected Parameters”, in Proc. IEEE International Test Conference,

[11] A. Barua, P. Kabisatpathy, and S. Sinha, “A method to diagnose faults in analog integrated circuits using artificial neural networks with pseudorandom noise as stimulus”, in Proc. 10th IEEE

[12] P.M. Frank, “Fault diagnosis in dynamic systems using analytical and knowledge-based redundancy – A survey and some new results”, Automatica, Vol. 26, No. 3, pp. 459-474, 1990. [13] R. Isermann, “Process fault detection based on Modelling and estimation methods – A survey”, Automatica, Vol. 20, No. 4, pp. 387-404, 1984.

[14] B. Kaminska, K. Arabi, I. Bell, J.L. Heurtas, B. Kim, A. Rueda and M. Soma, “Analog and mixed-signal benchmark circuits – first release”, in Proc. IEEE International Test Conf. Washington

[15] B.A. Wooley, S.J. Wong and D.O. Pederson, “A computer-aided evaluation of the 741 amplifier”, IEEE Jour. Solid-State Circuits, Vol. SC-6, No. 6, pp. 357-366, 1971. |