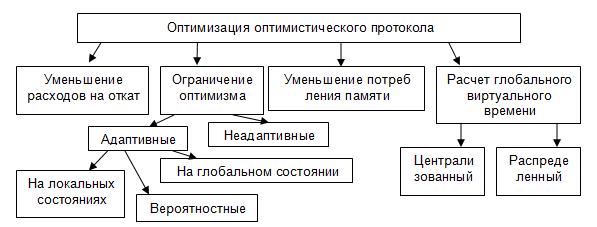

Рисунок 1 - Классификация методов оптимизации оптимистического протокола

Автор: Воротникова Ю.А., Попов Ю.В.

Источник:

A classification of methods to accelerate optimistic synchronization protocols for distributed logic simulation of digital systems is proposed. Approaches based on optimism limitation, memory saving, reducing the length and number of rollbacks are described.

В настоящее время цифровые схемы являются неотъемлемой частью в жизни каждого человека, поскольку компьютеры и бытовая техника используются повсеместно. В связи со значительным ростом размеров и усложнением топологии цифровых схем актуальным является вопрос о компьютерном моделировании и тестировании работы схемы. Разработано большое количество способов тестирования цифровых схем, наиболее перспективным является моделирование их работы с использованием оптимистического протокола.

Моделирование таких схем является длительным и ресурсоемким процессом, и оптимистический протокол решает только часть этих проблем. Поэтому предложено множество способов его оптимизации. На рис. 1 представлена классификация существующих способов оптимизации оптимистического протокола.

Рисунок 1 - Классификация методов оптимизации оптимистического протокола

Методы уменьшения расходов на откат управляют течением вычислительного процесса с тем, чтобы как можно раньше обнаружить некорректные вычисления, остановить их и тем самым уменьшить длину и ресурсоемкость откатов. Для этого применяются различные способы обнаружения некорректных вычислений [1, 2, 4].

Методы ограничения оптимизма уменьшают длину и ресурсоемкость откатов, что достигается по большей части установлением некоторых временных границ (временных окон), в пределах которых разрешено выполнять моделирование. Ограничение оптимизма (временное окно) может быть задано константно (в неадаптивных методах), либо меняться в зависимости от текущего состояния системы (адаптивные методы). При этом могут учитываться локальные состояния процессов (упрощает реализацию) или глобальные состояния (более точный метод, но ресурсоемкий) [2, 3, 4].

Методы экономии памяти решают задачу ресурсоемкости при тестировании больших цифровых схем. Эти методы применяют периодическое или частичное сохранение состояний, методы обратных вычислений, а также способы освобождения памяти для эффективной и быстрой работы моделирующей системы [2, 3, 4].

Различные методы вычисления глобального виртуального времени, прежде всего, влияют на освобождения памяти.

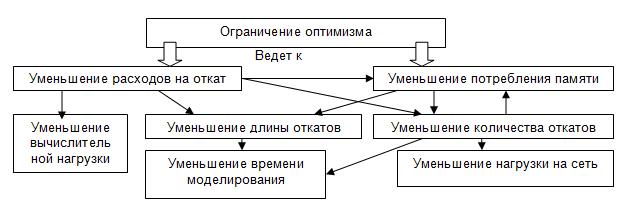

Однако нельзя четко разделить методы по способу решения конкретного недостатка протокола. Причинно-следственные связи в работе механизмов представлены на рис. 2.

Рисунок 2 - Причинно-следственные связи в работе механизмов ускорения

1. R. Rajan, R. Radhakrishnan, P. A. Wilsey. Dynamic Cancellation: Selecting Time Warp Cancellation Strategies at Runtime. VLSI DESIGN 1999, Vol. 9, No. 3, pp. 237–251.

2. C Tropper. Parallel discrete-event simulation applications. Volume 62, Issue 3, March 2002, Pages 327–335.

3. Voon-Yee Vee, Wen-Jing Hsu. Parallel Discrete Event Simulation: A Survey. Information Systems Journal. 1999. – 30 р.

4. Parallel discrete-event simulation, Jason Liu, Wiley Encyclopedia of Operations Research and Management Science. 2009 – 20 p.