Розробка і дослідження структури логічного аналізатора цифрових сигналів

Автор: Блінов Ю.В. , Зінченко Ю.Є.

Источник:

Автор: Блінов Ю.В. , Зінченко Ю.Є.

Источник:

Логічний аналізатор являє собою електронний інструмент, який відображає сигнали в цифрових схемах, які занадто швидкі, щоб спостерігати і представляє їх користувачеві, так, що користувач може легко перевірити роботу цифровою системи з великою точністю. Вони зазвичай використовуються для збору даних в системах, які мають занадто багато каналів, щоб бути дослідженими за допомогою осцилографа [3].

В даний час є дві категорії логічних аналізаторів:

В статті розглянуто логічний аналізатор другого виду, що є приставкою до ПК на базі FPGA плати Spartan-3E.

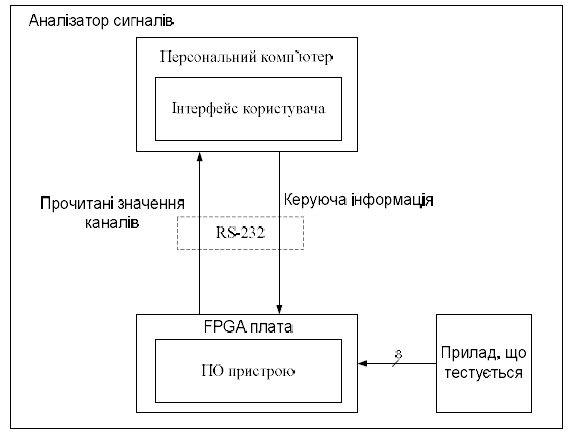

З рис. 1 видно, що аналізатор сигналів є комплексним пристроєм, що складається з двох частин.

1. Персональний комп’ютер з розробленим програмним забезпеченням слугує для завдання параметрів захвату сигналів з досліджуваного пристрою, для прийому та обробки значень каналів.

2. Приставка у виді FPGA плати слугує для відстеження умов початку опитування та збереження захоплених значень з досліджуваного пристрою.

Рисунок 1 — Загальна структура проекту

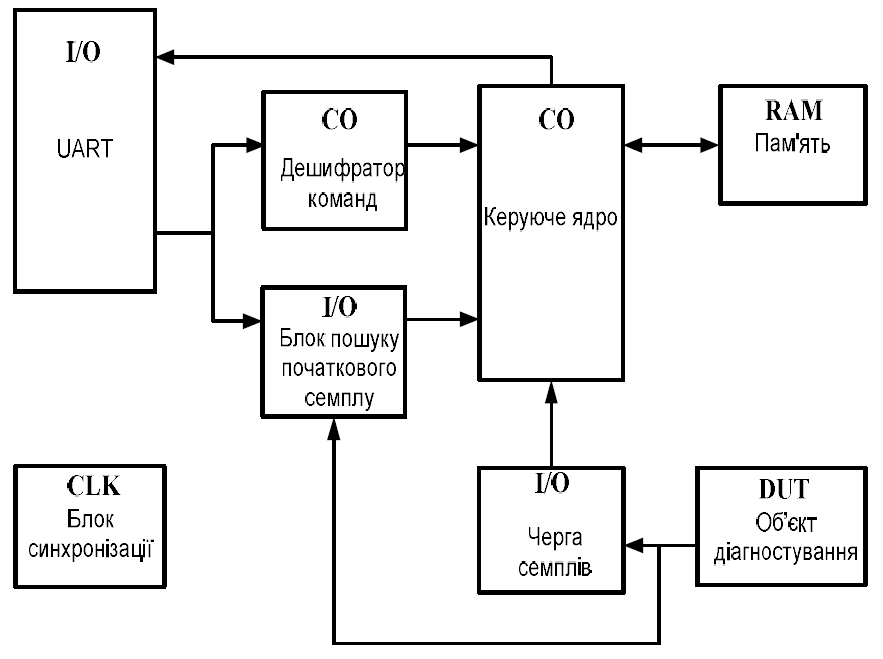

Структурна схема FPGA-пристрою аналізатора сигналів наведена на рис. 2.

До складу структурної схеми увійшли наступні компоненти:

Керуюче ядро — блок працюючий за принципом машини з кінцевою кількістю станів (FSM, Finite State Machine). Керуюче ядро призначене для організації коректної взаємодії між іншими складовими частинами пристрою, та взаємодією логічного аналізатора с клієнтською програмою на ПК;

Блок синхронізації — генерування синхросигналу завданої частоти на базі сигналу 50MHz;

UART — організація обміну інформацією між ПК та пристроєм ;

Дешифратор команд — в функції цього блоку входить аналіз команд з ПК та формування відповідних керуючих сигналів.

3. Черга семплів — черга завданої довжини, призначення якої полягає в збереженні передісторії до появлення потрібної комбінації на виходах приладу, що тестується, це дозволяє побачити стан приладу в попередніх тактах до того, як задана подія трапилася;

4. Блок пошуку початкового семплу — в залежності від встановленої маски, встановленого значення та поточного стану виходів приладу формує сигнал «HIT», що сигналізує про появлення потрібної комбінації на виходах об’єкту діагностики (ОД);

5. Пам’ять — призначена виключно для збереження семплів отриманих на виходах ОД, при виявленні на них потрібної комбінації, до пам’яті вони записуються не на пряму, а проходячи через чергу семплів;

Рисунок 2 — Структурна схема аналізатору сигналів на базі FPGA плати

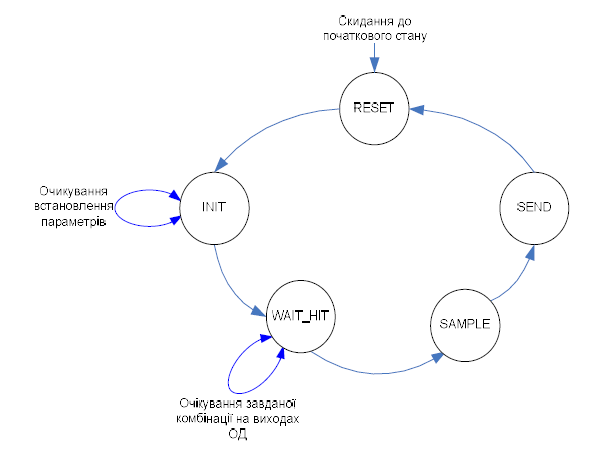

Розглянемо алгоритм функціонування блоку контролю (рис. 3). Згідно з алгоритмом виконується наступне:

Рисунок 3 — Діаграма станів логічного аналізатору сигналі

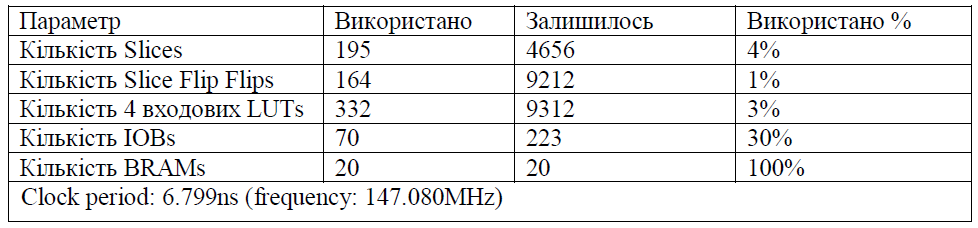

Таблиця 1 – Технічні параметри розробленої структури

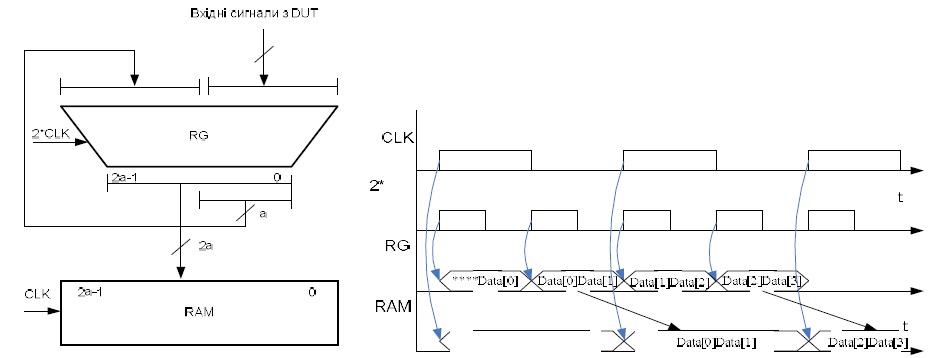

Виходячи з таблиці 1 максимальна частота з якою може працювати пристрій 147.080MH.підвищіти частоту семплування можна за допомогою швидкодіючої схеми регістру зсуву (рис. 4).

Рисунок 4 – Використання регістру зсуву для підвищення швидкодії

Результатом досліджень, проведених в рамках підготовки цієї статті, стала експериментальна поведінкова модель аналізатору сигналив на базі відлагоджувальної плати Xilinx Spartan-3E.

Виходячи з отриманих результатів, можна зробити висновок, що експериментальні структури, отримані під час розробки є задовільними. Також потрібно відмітити те, що вони є переносимими на інші FPGA плати. Це обумовлено тим, що для їх реалізації використано мову програмування VHDL.