Аннотация

Беседа Д.Г., Зинченко Ю.Е. Разработка метода эмуляции работы FPGA-платы с клавиатурой через порт PS/2. Проведено исследование организации microblaze-архитектуры FPGA-плат фирмы Xilinx. Выделен метод взаимодействие FPGA-платы фирмы Xilinx с периферийными устройствами. Проведено исследование работы порта PS/2. На основе проведенных исследований предложен метод эмуляции работы FPGA-платы с периферийными устройствами, подключенными к порту PS/2 Рассмотрены методы реализации движков для обслуживания и администрирования сайтов. При выполнении данного проекта

Ключевые слова: microblaze, processor local bus, ps/2, периферийное устройство, FPGA.

Постановка проблемы. Сегодня для молодого инженера существует множество направлений для исследования в различных областях. Одним из самых популярных направлений в области проектирования вычислительных систем являются FPGA-технологии. Однако данная область теряет свою привлекательность для украинского студента в связи с дороговизной FPGA-плат, а также трудоемкостью поиска и заказа необходимой FPGA-платы. Решить вышеупомянутые проблемы можно с помощью создания виртуальной FРGA-лаборатории, предоставив удаленный доступ к платам.

Практически любой проект, создаваемый на базе FPGA-технологий предполагает использование различных периферийных устройств. Поэтому, при проектировании виртуальной FPGA-лаборатории, одной из основных задач является разработка методов эмуляции периферийных устройств.

Анализ литературы. В мире существуют несколько реализованных проектов по созданию виртуальной FPGA-лаборатории. Реализация подобного проекта делится на аппаратную и программную части, каждая из которых включает в себя ряд специфических требований и подходов. Основными этапами проектирования являются:

- Программирование сервера, к которому подключаются FPGA-платы.

- Визуальный интерфейс.

- Эмуляция работы периферийных частей схем. [1]

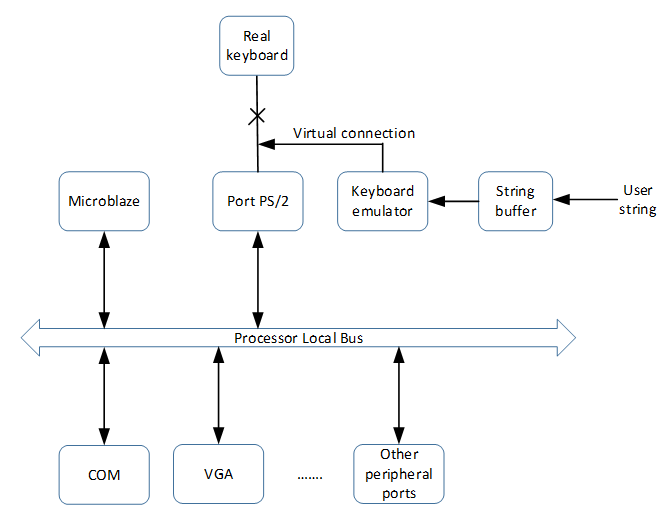

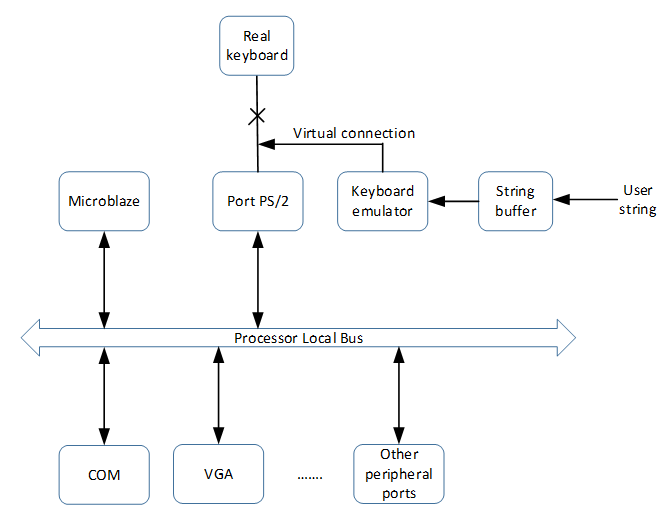

- Сервер принимает строку, введенную пользователем на клиентской стороне веб-ресурса виртуальной FPGA-лаборатории.

- Далее пользовательская строка передается в буфер на FPGA-плате.

- Далее строка посимвольно передается в имитатор клавиатуры.

- Имитатор клавиатуры осуществляет подключение к порту PS/2 на FPGA-плате.

- Имитатор осуществляет ввод пользовательской информации посимвольно непосредственно в порт PS/2.

- Беседа Д.Г., Зинченко Ю.Е. Исследование методов создания виртуальной FPGA-лаборатории 2013. С. 3

- Rod Jesman, Fernando Martinez Vallina, Jafar Saniie Microblaze Turtorial с.36

- Microblaze processor reference guide. –– Интернет ресурс. –– Режим доступа: http://www.xilinx.com/support/documentation/sw_manuals/mb_ref_guide.pdf.

- LogiCORE IP Processor Local Bus (PLB) v4.6 (v1.05a) –– Интернет ресурс. –– Режим доступа: http://www.xilinx.com/support/documentation/ip_documentation/plb_v46.pdf

- Беседа Д.Г. Проектирование виртуальной FPGA-лаборатории: Студенческая научная работа, ДонНТУ, Донецк, 2013 С. 11-19

При организации же работы с периферийными устройствами в подобных проектах, чаще всего, используются особенности шинной архитектуры FPGA-плат.

Цель статьи – провести исследование особенностей организации microblaze-архитектуры FPGA-плат фирмы Xilinx. Выявить методы взаимодействия FPGA-плат с периферийными устройствами. Исследовать организацию информационного обмена через порт PS/2. Предложить свой способ эмуляции работы периферийных устройств при работе с FPGA-платами на примере работы с клавиатурой через порт PS/2.

Постановка задачи исследования. Задачей исследование является выявление методов организации работы FPGA-плат с периферийным оборудованием. По результатам проведенных исследований необходимо разработать свой метода эмуляции периферийных устройств для виртуальной FPGA-лаборатории.

Решение задач и результаты исследований. FPGA-платы фирмы Xilinx делятся на 2 типа: платы с процессорами MicroBlaze и PowerPC. Исследуемая плата (Xilinx Spartan 3E Starter Kit) оснащена процессором Microblaze, поэтому остановимся подробнее на этой архитектуре.

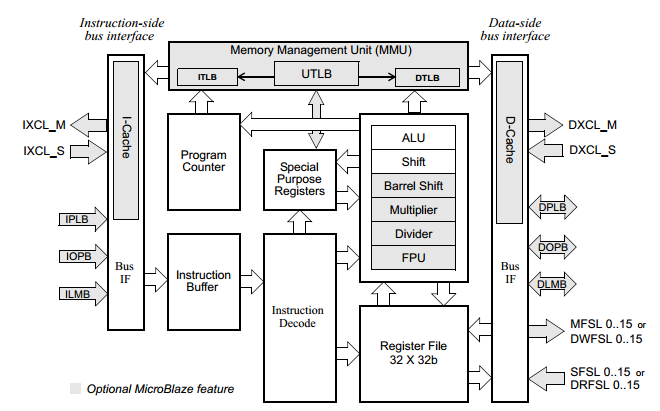

MicroBlaze – это виртуальный микропроцессор, который основан на объединение программных модулей. Преимущество такого подхода заключается в том, что разработчик получает ровно столько ресурсов системы, сколько ему необходимо для реализации поставленной задачи. [2]

Процессор Microblaze – это 32-битная RISC архитектура, которая была оптимизирована для FPGA-систем фирмы Xilinx с 32-битными шинами команд и данных, а также одновременным доступом как к встроенной, так и внешней памяти. Архитектура ядра процессора MicroBlaze приведена на рисунке 1. [3]

Основной интерес в этой структуре представляет шина PLB – Processor Local Bus. Это 128-битная шина для соединения произвольного числа периферийных устройств, работающих в режимах master и slave. Она состоит из модуля управления шиной, таймера, программных модулей чтения и записи данных, блока адресации и дополнительного DCL (Device Control Register) slave интерфейса для обеспечения доступа к регистру ошибок. [4]

Таким образом, все общение FPGA-платы с периферийными устройствами осуществляется посредством шины PLB.

Разработка метода эмуляции работы периферийных устройств с FPGA-платой происходит на примере порта PS/2, который взаимодействует с клавиатурой.

Для эмуляции работы порта PS/2 необходимо буфер, для хранения информации, поступающей от пользователя для дальнейшей передачи в порт, а также программный имитатор клавиатуры, который будет выполнять передачу пользовательской информации непосредственно в порт PS/2.

Алгоритм работы эмулятора порта PS/2 имеет следующий вид:

Функциональная схема работы FPGA-платы с виртуальной клавиатурой представлена на рисунке 3.

Имитатор клавиатуры должен передавать каждый пользовательский символ в 11-битном формате, который приведен в таблице 1.

Таблица 1 – Формат пакета данных от клавиатуры к FPGA-плате

| Биты | Значение |

| 1 | Старт бит. Всегда равен 0 |

| 2-9 | Посылаемая информация. Наименьший значащий бит – первый |

| 10 | Бит чётности |

| 11 | Бит четности. Всегда равен 1 |

Частота такта порта PS/2 10-16,7 кГц. Время от перехода Clock в “1? до смены Data должно быть не меньше 5 мкс. Время от смены Data до перехода Clock в “0? должно быть не меньше 5 мкс и не больше 25 мкс. Временная диаграмма, иллюстрирующая передачу данных от устройства к хосту посредством интерфейса PS/2, а также временные характеристики сигналов приведены на рисунке 2. [5]

Выводы. Проведены исследования организации работы FPGA-плат фирмы Xilinx с периферийными устройствами. Исследована организация информационного обмена между клавиатурой и FPGA-платой через порт PS/2. Предложен свой метод эмуляции порта PS/2 FPGA-платы Xilinx.