Разработка постбинарного интервального АЛУ для модифицированных форматов чисел с плавающей запятой

Автор: Ковалев А. А., Иваница С. В., Дорожко Л. И.

Источник: Матерiали науково-технiчної конференцiї студентiв, аспiрантiв та молодих вчених. — Донецьк, ДонНТУ — 2014

Аннотация

Ковалев А. А., Иваница С. В, Дорожко Л. И. Разработка постбинарного интервального АЛУ для модифицированных форматов чисел с плавающей запятой. Проведен анализ точности компьютерных вычислений с плавающей запятой. Рассмотрен интервальный подход для организации компьютерных вычислений и получения достоверных результатов. Выделены особенности постбинарной реализации интервальных вычислений. Предложена структурная схема постбинарного интервального арифметико-логического устройства.

Постановка проблемы.

Возникновение и накопление погрешности вычислений при выполнении арифметических операций с плавающей запятой является неотъемлемой частью современного компьютинга. Поэтому актуальным и востребованным является решение проблемы точности и достоверности компьютерных вычислений путем минимизации погрешностей, их учета и контроля при работе с числами в формате с плавающей запятой.

Анализ литературы.

В работе [1, с. 196–210] рассмотрены проблемы компьютерных вычислений, вызванных использованием стандарта IEEE 754, а также приведена классификация ошибок с примерами получения «неожиданных» результатов. Анализ материала показал, что к формату числа с плавающей запятой невозможно точно привести вещественное число в виду того, что формат содержит множество конечных значений (точек разрядной сетки) которыми невозможно представить бесконечное множество действительных чисел. Этот фактор является основным недостатком стандартного плавающего формата, что подтверждается и исследуется в целом сегменте научных публикаций, например в [2; 3].

Среди прочих решений данной проблемы можно выделить возможность перехода от числа «точечного» к числу интервальному, что подтверждается развитием интервального анализа [4] и распространением интервальных подходов при решении широкого круга задач [5]. Интервальный подход позволяет учитывать ошибки вычислений, а также решает проблему компьютерного представления и обработки иррациональных (в том числе и трансцендентных) чисел [6, рис. 1]. В исследованиях [6; 7] выделен недостаток перехода к машинным интервалам, поскольку при занесении значений границ интервального числа в память ЭВМ возникает необходимость вновь использовать вещественные форматы чисел, являющиеся стандартными форматами чисел с плавающей запятой одинарной или двойной точности.

В цикле научных работ, наиболее значимыми из которых являются монографии [1] и [7], предлагается решение поставленной проблемы. Авторами разработаны постбинарные представление и обработка числовых данных, а также предложены соответствующие форматы чисел.

Цель статьи.

Цель статьи – провести анализ возможностей постбинарного представления чисел. Выявить и проанализировать целесообразность применения постбинарных чисел в интервальной арифметике. В рамках обозначенного анализа предложить конфигурацию арифметико-логического устройства (АЛУ) как основной части специализированного математического сопроцессора [8].

Постановка задачи исследования.

Задачей исследования является анализ постбинарных форматов чисел с плавающей запятой с целью оптимального выбора для решения обозначенной проблемы. Также в рамках уже определенных постбинарных форматов для интервалов необходимо предложить аппаратную реализацию устройства, выполняющего постбинарные интервальные операции.

Решение задач и результаты исследований.

При анализе значений максимальной возможной ошибки для некоторых чисел в форматах с плавающей запятой одинарной и двойной точности [3] становится очевидно, что в ряде случаев операции с числами стандарта IEEE 754 [9] могут приводить к неточным результатам и быть бесполезными. Таким образом, математическая модель с плавающими числами может быть адекватной и работоспособной лишь в случае обеспечения контроля погрешностей вычислений.

Для реализации такого контроля возможно использование постбинарного представления чисел, а также использование интервальной математики. Ценность интервальных вычислений заключается в получении наиболее достоверных решений исходных задач, учитывая возможные изменения исходных и результирующих значений, связанные с неточностью арифметики с плавающей запятой. Но следует заметить, что для сложных вычислений результаты могут оказаться неудовлетворительными, прежде всего из-за слишком большой длины получаемых интервалов.

Одно из возможных решений этой проблемы лежит в переходе к постбинарным вычислениям. При этом появляется возможность максимально использовать тот научно-технический задел, который накоплен в рамках интервальных вычислений, но при этом устранить или минимизировать некоторые проблемы интервального анализа, связанные, например, с противоречием между точностью представления самих границ интервальных значений и фактической неточностью тех данных, которые они представляют.

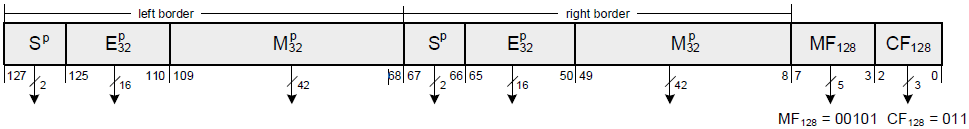

В этом случае целесообразно использовать постбинарные интервальные форматы одинарной (pbinary128/32ip) и двойной (pbinary256/64ip) точности [7, c. 216]. Структура формата одинарной точности приведена на рис. 1.

Рисунок 1 – Структура формата pbinary128/32ip (индекс р – постбинарное кодирование; S, E и M – поля знака, порядка и мантиссы; MF и CF – модификатор и код формата) [7, с. 207]

Согласно рис. 1, рассматриваемый формат имеет две части (условно «левую» – left border, диапазон [127:68] и «правую» – right border, диапазон [67:8]) для описания соответствующих границ интервала. Для преставления данных в этом формате используются принципы постбинарного кодирования, а в качестве кодовой системы применяется тетракод [7, c. 53–59].

Поскольку структура постбинарного интервального формата для каждой границы одинакова, то вычислительный блок АЛУ для поддержки этого формата может быть спроектирован так, чтобы в единый момент времени производить выборку одной границы каждого из двух операндов для выполнения арифметических (или, точнее, интервальных) и логических операций. Такой подход соответствует выполнению классических интервальных операций [4, с. 31–32].

Для разработки аппаратной модели постбинарного интервального АЛУ (в дальнейшем ПИАЛУ, PIALU) был выбран язык проектирования VHDL – язык описания аппаратуры интегральных схем, который является базовым языком при разработке аппаратуры современных вычислительных систем. В дальнейшем использование VHDL для рассматриваемого блока позволит спроектировать FPGA-решения, что на начальном этапе сделает продуктивными исследования модели устройства, а в последующих – выполнить его физическую реализацию.

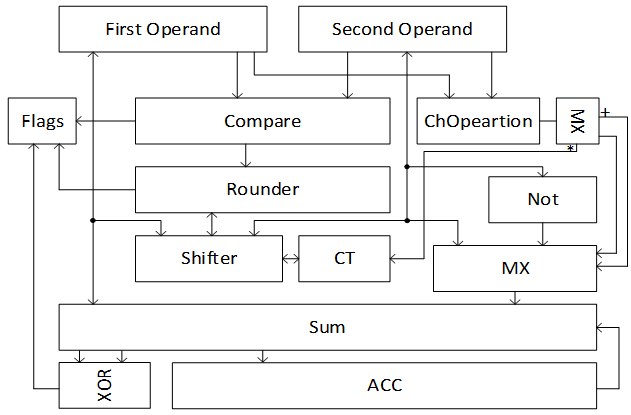

Текущий вариант ПИАЛУ предполагает реализацию четырех основных интервальных операций: сложения, вычитания, умножения и деления. Схема ПИАЛУ изображена на рис. 2.

Рисунок 2 – Структурная схема ПИАЛУ

Структурная схема на рис. 2 имеет обобщенный характер, но дает отчетливое представление о некоторых количественных и качественных показателей разрабатываемого вычислительного устройства. В ПИАЛУ все регистровые блоки («First Operand», «Second Operand», «ACC») имеют полное структурное соответствие формату pbinary128/32ip. Блок «Compare» – компаратор, способный сравнивать два тетракодовых слова, а блок «Rounder» – блок, в котором выполняется постбинарное округление [1, с. 211–219]. Блок «ChOperation» позволяет выбрать тип операции, а мультиплексоры MX, в зависимости от операции и знаков операндов, позволяют подать на сумматор «Sum» операнды в нужном порядке. В схеме также используются сдвигатель «Shifter», регистр флагов «Flags», счетчик «CT». Аккумулятор ACC используется для реализации постбинарного умножения [1, с. 254–255].

Выводы

Проведен анализ текущего состояния компьютерных вычислений с плавающей запятой. Рассмотрены возможность использования интервальных вычислений и особенности их постбинарной реализации. Предложено использование постбинарных интервальных форматов для организации компьютерных вычислений с плавающей запятой. Обосновано проектирование и реализация постбинарного интервального арифметико-логического устройства.

Список использованной литературы

- Аноприенко А. Я. Тетралогика, тетравычисления и ноокомпьютинг. Исследования 2010–2012. / А. Я. Аноприенко, С. В. Иваница — Донецк: ДонНТУ, Технопарк ДонНТУ УНИТЕХ, 2012. — 308 с.

- Юровицкий В. М. IEEE754-тика угрожает человечеству МФТИ, РГСУ, Москва. — Интернет-ресурс. — Режим доступа: http://www.yur.ru.

- IEEE 754 – стандарт двоичной арифметики с плавающей точкой. — Интернет-ресурс. — Режим доступа: http://www.softelectro.ru/teoriy.html.

- Добронец Б. С. Интервальная математика: Учеб. пособие / Б. С. Добронец; Краснояр. гос. ун-т — Красноярск, 2004. — 216 с.

- Moore R. E. Introduction to interval analysis. / R.E. Moore, R.B. Kearfott, M.J. Cloud — Philadelphia: SIAM, 2009. — p. 223.

- Аноприенко А. Я., Иваница С. В. Интервальные вычисления и перспективы их развития в контексте кодо-логической эволюции. / А. Я. Аноприенко, С. В. Иваница. // Научные труды Донецкого национального технического университета. Серия «Проблемы моделирования и автоматизации проектирования динамических систем» (МАП-2010). Выпуск 8 (168): Донецк: ДонНТУ, 2010. — С. 150–160.

- Аноприенко А. Я. Постбинарный компьютинг и интервальные вычисления в контексте кодо-логической эволюции. / А. Я. Аноприенко, С. В. Иваница — Донецк: ДонНТУ, УНИТЕХ, 2011. — 248 с.

- Анопрієнко О. Я. Принцип роботи, структура і моделювання блоку перетворювача форматів у складі постбінарного співпроцесора. / О. Я. Анопрієнко, С. В. Іваниця, С. В. Кулібаба // Міжнародний науково-технічний журнал «Інформаційні технології та комп’ютерна інженерія», № 1 (26). — Вінниця, 2013. — С. 59–65.

- Kahan W. Lecture Notes on the Status of IEEE Standard 754 for Binary Floating-Point Arithmetic / W. Prof. W. Kahan — Elect. Eng. & Computer Science, Berkeley, 1997 — р. 30.