Реферат по теме выпускной работы

Содержание

- Введение

- 1. Актуальность темы

- 2. Цель и задачи исследования, планируемые результаты

- 3. Обзор исследований и разработок

- 3.1 Обзор международных источников

- 3.2 Обзор национальных источников

- 3.3 Обзор локальных источников

- 4. Процесс проектирования ПЛИС с использованием FPGA

- 5. Анализ существующих САПР

- 5.1 Vivado от Xilinx

- 5.2 Quartus-Prime от Altera Intel

- 5.3 Active-HDL от Aldec

- 6. Анализ способов создания машин логического вывода

- 6.1 CLIPS

- 6.2 Protege

- 6.3 Использование ТМО для организации логического вывода

- 7. Постановка задачи и описание разрабатываемой надстройки

- Выводы

- Список источников

Введение

На сегодняшний день проектирование ПЛИС является одной из наиболее быстро растущих предметных областей. Это обусловлено тем, что количество различных гаджетов, для которых и нужны чипы, только растёт, и с каждым годом только сильнее. Необходимость обеспечивать рынок нужным объёмом продукции вынуждает инженеров уменьшать время изготовления конечного продукта, и, как следствие этого, автоматизировать процесс проектирования.

Эффективность процессов проектирования в любых предметных областях во многом определяется наличием и степенью развития средств, позволяющих проектировщику формализовать и повторно использовать экспертные методики для проектирования тех или иных изделий. Методики проектирования призваны существенно упростить проектировщику решение задачи проектирования, исходя из требований технического задания на изделие (ТЗ). Такие инструментальные средства позволяют создавать методики проектирования, сохранять их, редактировать и применять по мере надобности. Эффект в этом случае состоит в сокращении времени и трудоемкости процесса принятия проектных решений.

1. Актуальность темы

При проектировании ПЛИС инженеры используют самые передовые программные комплексы, которые берут

на себя такие трудозатратные операции как трассировка схемы, временной анализ, проверка на несоответствия

и ошибки и т.п. Но для работы с любым из пакетов, которые сейчас существуют на рынке, проектировщик

по–прежнему должен обладать высоким уровнем знаний предметной области. Кроме того, для ведущих компаний

в сфере проектирования вычислительной техники (и не только для них) имеет место проблема: Как сохранить

знания и опыт сотрудников?

и, более того: Как извлечь из этого практическую пользу?

.

В связи с этим возникает следующая задача: создание базы знаний проектирования ПЛИС. База знаний, на данный момент, является самым современным и технологичным решением в области хранения данных. Она позволит не только сохранить накопленный годами опыт сотрудников, но и сможет применить его для синтеза новых продуктов [1].

2. Цель и задачи исследования, планируемые результаты

Целью исследования данной работы является:

- Проанализировать существующие САПР FPGA и выявить их основные положительные качества.

- Проанализировать существующие подходы для создания машин логического вывода.

- Выбрать лучший подход для реализации базы знаний и обосновать решение.

- Описать структуру разрабатываемого программного продукта.

Объектом исследования данной работы является практическая реализация базы знаний в виде надстройки над САПР РЭА.

3. Обзор исследований и разработок

3.1 Обзор международных источников

В работе Automated sports rim design in CAD system

M.S. Abdul Karim и Ahmad Zulhakim Ab Rashid [2]

исследуют пути создания автоматизации на этапе проектирования для сокращения времени на проектирование

в рамках пакета автоматизированного проектирования (САПР). Выяснилось, что одним из наиболее эффективных

способов реализации автоматизации в проектировании является автоматизация повторяющихся шагов, которые

необходимо выполнять при каждом создании детали. Этот проект был нацелен на разработку способа автоматизации

повторяющихся шагов, и было проведено тематическое исследование конструкции обода колеса.

В работе A Methodology of Knowledge Management Based on Ontology in Collaborative Design

Junming Hou, Chong Su, Yingying Su, Wanshan Wang [3] предложена методология управления знаниями

в совместном дизайне, представляются концепции совместного проектирования и управления знаниями,

а также вводится выражение знаний, основанное на онтологии.

3.2 Обзор национальных источников

Книга Базы знаний интеллектуальных систем

Т.А. Гавриловой, В.Ф. Хорошевского [4] является

учебником для технических вузов по входящим в различные дисциплины вопросам разработки интеллектуальных

систем. Актуальность предмета определяется растущим применением инженерии знаний и системного анализа в

различных областях деятельности.

Особенностью изложения является его практическая направленность: освоения имеющегося материала достаточно для начала самостоятельной работы над созданием интеллектуальной системы, основанной на знаниях.

В учебнике учтена все возрастающая роль Интернета, и потому подробно рассматривается применение инженерии знаний в Сети.

3.3 Обзор локальных источников

Среди магистров ДонНТУ можно выделить следующие публикации.

В магистерской работе О.В. Малявки Исследование способов организации построения

инструментальной интеллектуальной оболочки для проектирования сложных объектов на

базе экспертных методик

[5] произведён анализ существующих инструментальных средств

построения САПР, усовершенствованы существующие алгоритмы. Осуществлена оценка их

эффективности и построен с их помощью инструментарий для автоматизации создания

проблемно–ориентированных САПР.

4. Процесс проектирования ПЛИС с использованием FPGA

Проектирование цифровых устройств представляет из себя итерационный процесс, основанный на принципах функциональной декомпозиции [6]. Проектирование традиционно разделяют на этапы:

- системный,

- структурно-алгоритмический,

- функционально-логический,

- конструкторско-технологический,

На системном этапе весь проект разбивается на части, определяются их назначение и взаимосвязь, принимается решение о способах реализации частей. Решение об использовании ПЛИС, принятое на системном этапе, позволяет выполнять конструкторско-технологическое проектирование модуля верхнего уровня параллельно с выполнением других этапов.

Структурно-алгоритмический и функционально–логический этапы проектирования на ПЛИС представляют из себя итерационный процесс ввода описаний с последующей их верификацией.

Современные САПР поддерживают несколько способов описания устройства:

- Описание с использованием языков описания аппаратных средств (VHDL, Verilog, AHDL и других) при помощи специализированного текстового редактора.

- Схемотехнический способ с помощью программы визуального проектирования, в которой разработчик помещает на рабочую область функциональные блоки и производит их соединение. По окончании визуального проектирования схема преобразуется в языковое описание.

- Графическое представление цифровых автоматов в специализированном редакторе, обеспечивающем преобразование полученного графического представление в языковое описание.

- Описание комбинационной логики с помощью таблиц истинности, карт Карно, функций алгебры логики.

Конструкторско–технологический этап проектирования с использованием ПЛИС разделяется на связанные подзадачи:

- Синтез (Synthesis).

- Глобальное размещение (Mapping).

- Локальное размещение (Placement).

- Трассировку (Routing).

Синтез (Synthesis) — отображение схемы в базис логических ресурсов ПЛИС. Цель синтеза — преобразование исходного схемотехнического или высокоуровневого описания устройства в описание, оптимально реализуемое на выбранной ПЛИС, а также пригодное для дальнейшего размещения и трассировки.

Глобальное размещение (Mapping) — назначение частям схемы макрообластей ПЛИС, представляющих из себя группы соседних логических блоков, макроячеек и блоков ввода/вывода. Цель глобального размещения: создание наилучших условий для локального размещения и трассировки. Для достижения этого используется информация о назначении сигналам внешних выводов, в большой мере влияющая на назначение свободных областей ПЛИС частям схемы. Как правило, назначение логических ресурсов кристалла макрообластям производят с избыточностью, облегчающей последующую трассировку.

Локальное размещение (Placement) — детальное назначение логических ресурсов макрообластей, выбранных на стадии глобального размещения, частям схемы. При этом преследуются цели: равномерное заполнение макрообластей элементами и трассами, минимизация суммарной длинны линий связи и другие. Основная цель локального размещения — создание наилучших условий для трассировки.

Трассировка (Routing) — определение связей между логическими блоками, макроячейками и блоками ввода-вывода в виде коммутированных участков трасс. На данной стадии преследуются цели: выбора трасс, обеспечивающих заданное время распространения сигнала; минимизации суммарного количества программируемых точек связи; минимизация времени распространения сигнала по самой длинной линии связи. Важной задачей стадии трассировки является определение временных параметров полученного варианта устройства и сравнение их с заданными ограничениями.

Процесс проектирования является итерационным. После выполнения каждой стадии производится верификация полученного описания, для чего применяются различные средства моделирования и анализа. В современных САПР обычно предусматривается моделирования на следующих этапах:

- Моделирование поведенческого описания.

- Моделирование описания на языке регистровых передач.

- Моделирование технологического описания (после синтеза).

- Моделирование на вентильном уровне.

- Моделирование после размещения.

- Моделирование после трассировки.

5. Анализ существующих САПР

5.1 Vivado от Xilinx

Vivado Design Suite — это программный пакет, разработанный Xilinx для синтеза и анализа HDL проектов, заменяющий Xilinx ISE дополнительными функциями для разработки систем на чипах (System on Chip, SoC) и высокоуровневого синтеза (High-Level Synthesis). В отличие от ISE, который использовал для моделирования ModelSim, Vivado System Edition включает встроенный логический симулятор [7].

Vivado позволяет разработчикам синтезировать проекты, выполнять временной анализ, изучать RTL–диаграммы, моделировать реакцию проекта на различные воздействия и настраивать целевое устройство с помощью программиста. Vivado — это среда разработки продуктов FPGA от Xilinx, тесно связанная с архитектурой таких чипов, и ее нельзя использовать с продуктами FPGA других производителей.

В состав Vivado входят следующие компоненты:

- Компилятор Vivado High-Level Synthesis позволяет описывать схемы на C, C++ и SystemC для устройств Xilinx без необходимости создавать RTL вручную. Vivado HLS широко рассматривается для повышения производительности труда разработчиков, и подтверждено, что он поддерживает классы C++, шаблоны, функции и перегрузки операторов. В Vivado 2014.1 появилась поддержка автоматического преобразования ядер OpenCL в IP для устройств Xilinx. Ядра OpenCL — это программы, которые выполняются на разных платформах CPU, GPU и FPGA.

- Vivado Simulator — симулятор скомпилированного языка, который поддерживает смешанные языки, сценарии TCL, зашифрованный IP и расширенную проверку.

- Vivado IP Integrator позволяет инженерам быстро интегрировать и настраивать IP из большой IP–библиотеки Xilinx. Интегратор также настроен для проектов MathWorks Simulink, созданных с помощью системного генератора Xilinx и высокоуровневого синтеза Vivado.

- Vivado TCL Store — это система сценариев для разработки дополнений к Vivado, и ее можно использовать для добавления и изменения возможностей Vivado. TCL расшифровывается как Tool Command Language и является языком сценариев, на котором основан сам Vivado. Все базовые функции Vivado могут вызываться и управляться через сценарии TCL.

Рисунок 1 — Упрощённый маршрут проектирования в Vivado HLS.

(анимация: 8 кадров, задержка 2 с, 8 циклов повторения, 39,8 КБ)

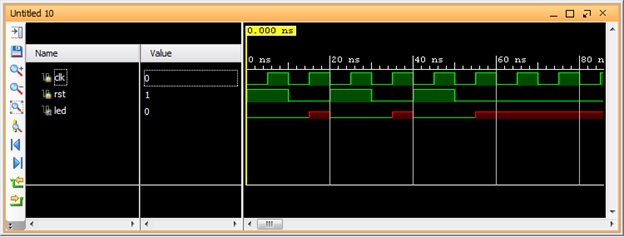

Рисунок 2 — Пример симуляции в Vivado Similator.

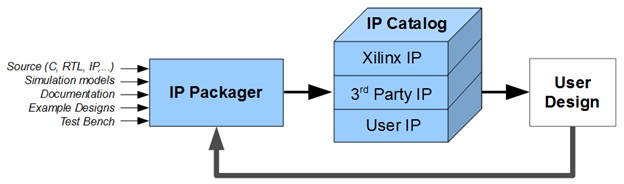

Рисунок 3 — Процесс проектирования с использованием Vivado IP Integrator.

Из всего вышесказанного можно выделить следующие достоинства и недостатки САПР Vivado Design Suite:

- Наличие мощных инструментов для автоматизации процесса трассировки, размещения, временного анализа схем.

- Наличие инструментов для высокоуровневого синтеза схем на языках С, С++ и System–C.

- Возможность управления всем циклом разработки с помощью скриптового языка Tcl.

- Возможность проектирования схем с помощью различных методологий: RTL–описаний, IP–ядер, языков описания аппаратуры, синтеза высокого уровня.

Достоинства:

- Нет возможности задания алгоритма проектирования как методики проектирования определённого класса устройств с последующим повторным использованием этого алгоритма.

- Для работы с САПР Vivado Design Suite проектировщик должен обладать высоким уровнем знания предметной области.

Недостатки:

5.2 Quartus-Prime от Altera Intel

Intel Quartus–Prime — это программное обеспечение для проектирования программируемых логических устройств, разработанное Intel; до приобретения Intel Altera инструмент назывался Altera Quartus II. Quartus–Prime позволяет анализировать и синтезировать проекты HDL, что позволяет разработчику скомпилировать проекты, выполнить временной анализ, изучить RTL–диаграммы, смоделировать реакцию проекта на различные воздействия и настроить целевое устройство с помощью программиста. Quartus–Prime включает в себя реализацию VHDL и Verilog для описания аппаратного обеспечения, визуального редактирования логических схем и моделирования векторных сигналов [8].

Quartus–Prime включает в себя такие программные функции:

- SOPC Builder, инструмент, который устраняет задачи ручной системной интеграции, автоматически генерируя логику межсоединений и создавая тестовую среду для проверки функциональности.

- Qsys, инструмент системной интеграции, являющийся следующим поколением SOPC Builder. Он использует оптимизированную FPGA архитектуру сети на кристалле, которая удваивает производительность fMAX по сравнению с SOPC Builder.

- SoCEDS, набор инструментов разработки, служебных программ, программ в реальном времени и примеров приложений, помогающих разрабатывать программное обеспечение для встроенных систем SoC FPGA.

- DSP Builder, инструмент, который создает плавный мост между инструментом MATLAB / Simulink и программным обеспечением Quartus Prime, поэтому разработчики FPGA имеют возможность разработки, моделирования и проверки алгоритмов инструментов проектирования на системном уровне MATLAB / Simulink.

- Инструментарий интерфейса внешней памяти, который определяет проблемы калибровки и измеряет поля для каждого сигнала DQS.

- Создание файлов JAM / STAPL для программистов внутрисхемных устройств JTAG.

- Также поддерживает скриптовые сценарии на языке Tcl.

SOPC Builder

SOPC Builder (система на программируемом чип–билдере) — это программное обеспечение, разработанное Intel, которое автоматизирует подключение программно–аппаратных компонентов для создания полноценной компьютерной системы, работающей на любом из ее различных чипов FPGA. SOPC Builder включает в себя библиотеку готовых компонентов (включая флагманский программный процессор Nios II, контроллеры памяти, интерфейсы и периферийные устройства) и интерфейс для включения пользовательских компонентов. Соединения осуществляются через шину Avalon. Арбитраж шины, согласование ширины шины и даже пересечение часового домена обрабатываются автоматически, когда SOPC Builder генерирует систему. GUI — это единственная вещь, используемая для настройки программно-аппаратных компонентов (которые часто имеют много опций) и для указания топологии шины.

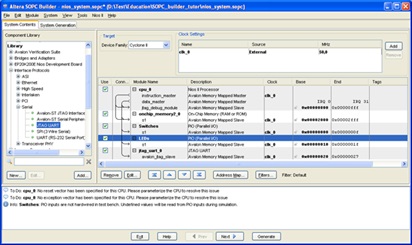

Рисунок 4 — Внешний вид окна SOPC Builder.

Получающаяся виртуальная

система может быть затем подключена к внешнему миру через

программируемые контакты FPGA или подключена внутри к другим программным компонентам.

Контакты FPGA направляются на разъемы, такие как PCI или DDR, или, как это часто бывает

во встроенных системах, на другие чипы, установленные на той же плате.

Использование ресурсов на FPGA, на которой размещена система SOPC Builder, очень скромно по современным стандартам. Устройства FPGA, поддерживающие системы SOPC, включают почти все FPGA Intel (и даже некоторые CPLD).

САПР Quartus–Prime очень похож на Vivado Design Suite, за небольшим исключением, поэтому и их достоинства и недостатки подобны:

- В Quartus–Prime также есть средства автоматизации процесса трассировки, размещения, временного анализа схем.

- Есть возможность создавать сценарии на языке Tcl для управления процессом разработки.

- Quartus–Prime может взаимодействовать с MATLAB / Simulink для создания и моделирования работы схемы.

- Проектировщик имеет возможность использовать различные методологии при разработке схемы: RTL–описание, IP–ядра, языки описания аппаратуры.

Достоинства:

- Отсутствуют инструменты для создания схем с помощью высокоуровневого синтеза на языках C, C++.

- Нет возможности задания алгоритма проектирования как методики проектирования определённого класса устройств с последующим повторным использованием этого алгоритма.

- Для работы с САПР Quartus–Prime проектировщик должен обладать высоким уровнем знания предметной области.

Недостатки:

5.3 Active-HDL от Aldec

Active–HDL — среда разработки ПЛИС, построенная на общем ядре симулятора HDL. Поддерживает инструменты ввода и отладки текстового и графического дизайна, обеспечивает симуляцию на разных языках (VHDL / Verilog / EDIF / SystemC / SystemVerilog) и предоставляет унифицированный интерфейс для различных инструментов синтеза и реализации. Также поддерживает проверку на основе утверждений с помощью утверждений Open Vera, PSL или Systemverilog Assertion. Доступны специальные версии программного обеспечения, которые поддерживают только одного поставщика ПЛИС, например, Active–HDL Lattice Edition.

- Наличие таких инструментов как Language Assistant и IP Core Generator для синтеза VHDL и Verilog кода.

- Есть инструменты для автоматизированной трассировки, размещения, временного анализа схем.

Достоинства:

- Отсутствуют инструменты для создания схем с помощью высокоуровневого синтеза на языках C, C++.

- Нет возможности задания алгоритма проектирования как методики проектирования определённого класса устройств с последующим повторным использованием этого алгоритма.

- Для работы с САПР Active–HDL проектировщик должен обладать высоким уровнем знания предметной области.

Недостатки:

6. Анализ способов создания машин логического вывода.

6.1 CLIPS

CLIPS — программная среда для разработки экспертных систем. Синтаксис и название предложены Чарльзом Форги (Charles Forgy) в OPS (Official Production System). CLIPS является продукционной системой. Реализация вывода использует алгоритм Rete.

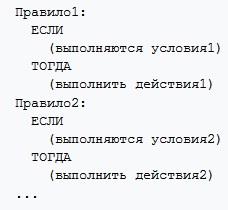

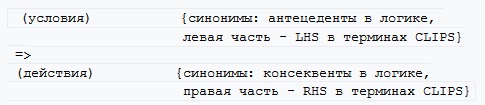

Основная идея состоит в представлении знаний в виде такой формы:

Рисунок 5 — Представление знаний в CLIPS.

Такое представление близко к человеческому мышлению и отличается от программ, написанных на традиционных алгоритмических языках, где действия упорядочены и выполняются строго придерживаясь алгоритма.

CLIPS является одной из наиболее широко используемых инструментальных сред для разработки экспертных систем благодаря своей скорости, эффективности и бесплатности. Являясь общественным достоянием, она до сих пор обновляется и поддерживается своим изначальным автором, Гэри Райли (Gary Riley).

CLIPS включает полноценный объектно–ориентированный язык COOL для написания экспертных систем. Хотя она написана на языке Си, её интерфейс намного ближе к языку программирования LISP. Расширения можно создавать на языке Си, кроме того, можно интегрировать CLIPS в программы на языке Си [9].

CLIPS разработан для применения в качестве языка прямого логического вывода (forward chaining) и в своей оригинальной версии не поддерживает обратного вывода (backward chaining).

Как и другие экспертные системы, CLIPS имеет дело с правилами и фактами.

Факты.

Информация, на основании которой экспертная система делает логический вывод, называется фактами. В CLIPS есть 2 вида фактов: упорядоченные и шаблонные. Шаблонные факты имеют шаблон, задаваемый конструкцией deftemplate. Упорядоченные не имеют явной конструкции deftemplate, однако она подразумевается. Шаблонный факт напоминает структуру в языке C или запись в языке Pascal, поля называются слотами и объявляются конструкцией slot.

Правила.

Знания предметной области представляются в CLIPS в виде правил, которые имеют следующую структуру:

Рисунок 6 — Правила в Clips.

Левая часть правила — это условие его срабатывания, а правая часть — это те действия, которые должны выполниться в случае выполнения условий. Знак => специальный символ, разделяющий LHS и RHS. Правила объявляются с помощью команды defrule.

6.2 Protege

Protege — это свободный, открытый редактор онтологий и фреймворк для построения баз знаний.

Платформа Protege поддерживает два основных способа моделирования онтологий посредством редакторов Protege–Frames и Protege–OWL. Онтологии, построенные в Protege, могут быть экспортированы во множество форматов, включая RDF (RDF Schema), OWL и XML Schema. Protege имеет открытую, легко расширяемую архитектуру за счёт поддержки модулей расширения функциональности.

Protege поддерживается значительным сообществом, состоящим из разработчиков и учёных, правительственных и корпоративных пользователей, использующих его для решения задач, связанных со знаниями, в таких разнообразных областях, как биомедицина, сбор знаний и корпоративное моделирование.

Редактор Protege–Frames

Редактор Protege–Frames позволяет пользователям строить и заполнять онтологии, основанные на фреймах, в соответствии с OKBC (Open Knowledge Base Connectivity protocol — прикладной интерфейс программирования для доступа к базам знаний систем представления знаний). В этой модели онтология состоит из набора классов, организованных в категоризованную иерархию, для представления важных понятий области, набора слотов, связанных с классами для описания их свойств и отношений между ними, и набора экземпляров этих классов — отдельных экземпляров понятий, которые имеют определенные значения своих свойств.

Редактор Protege–OWL

Редактор Protege–OWL позволяет пользователям строить онтологии для семантической паутины, в частности на OWL. OWL–онтология может включать описания классов, свойств и их экземпляров. Давая такую онтологию, формальная семантика OWL определяет как получать логические следствия, т.е. факты, которые не присутствуют непосредственно в онтологии, но могут быть выведены из существующих посредством семантики. Эти выводы могут быть основаны на одном документе или на множестве распределенных документов, которые были объединены с использованием определенных механизмов OWL.

6.3 Использование ТМО для организации логического вывода.

Использование Теоретико–множественных операций (ТМО) для организации логического вывода было подробно описано в работах А.В. Григорьева [10–12].

Коротко представить принцип работы машины логического вывода, основанной на ТМО можно следующим образом:

- Выполняются (ТМО) над имеющимися прототипами как совокупностями структурных компонент, имеющими те или иные признаки.

- Классификация отдельного уровня есть И–ИЛИ–дерево, где каждый узел имеет список прототипов, имеющих данный признак (

вход–выход

). - Поиск требуемого решения (прототипа) выполняется путём диалога, где каждый шаг предполагает выбор конкретного ИЛИ–узла с последующим продолжением диалога.

- После шага выбора происходит сужение оставшихся в рассмотрении прототипов, а также удаление тех ИЛИ–узлов, где число прототипов дошло до 0.

7. Постановка задачи и описание разрабатываемой надстройки

Так как во всех рассмотренных САПР есть такие недостатки как: 1) отсутствие возможности задания алгоритма проектирования как методики проектирования определённого класса устройств с последующим повторным использованием этого алгоритма; 2) высокие требования к уровню знания проектировщиком предметной области; то возникает соответствующая задача: создать программную надстройку над САПР FPGA для возможности создания алгоритма проектирования для его многократного использования.

Разрабатываемое ПО должно соответствовать следующим требованиям:

- Программная надстройка создаётся с целью обобщения пользовательского опыта, который в дальнейшем будет использован для создания новых продуктов. Следовательно, на вход системы должны подаваться существующие библиотеки компонентов. Предполагается, что они уже отлажены и не нуждаются в проверке.

- Надстройка должна упростить процесс проектирования путём его автоматизации.

- Система должна снизить требования к уровню знаний проектировщика.

- Процесс работы программной надстройки заключается в том, что она при помощи диалога с пользователем узнаёт нужные ему структурные компоненты, и на основании этой информации выдаёт ему необходимую схему в виде VHDL кода или ссылки на схему.

- Логический вывод программы должен быть организован при помощи ТМО. Выбор в пользу этого похода сделан по следующим причинам:

- При использовании таких пакетов как CLIPS и Protege повышаются требования к проектировщику в области организации знаний.

- Кроме того, возникает необходимость настройки программного взаимодействия между Clips/Protege и надстройкой над САПР.

- Подход с применением ТМО требует от нас только программной реализации самого подхода.

- Система должна реализовывать так называемый подход

глупого эксперта

[13].Глупый эксперт

— это проектировщик, у которого отсутствуют навыки в области организации знаний. В таком случае сама система берёт на себя всю работу по организации знаний (обучение, построение дерева решений, логический вывод). - Система должна быть реализована в качестве надстройки над САПР Vivado Design Suite, поскольку он является наиболее продвинутым из всех рассмотренных пакетов и одним из наиболее популярных среди проектировщиков.

Выводы

В результате научно–исследовательской работы были собраны и изучены материалы по вопросам, связанным с темой магистерской работы.

В исследовании были проанализированы существующие САПР РЭА, методы создания машин логического вывода, описана структура разрабатываемого программного продукта.

Автоматизация процесса проектирования является актуальной задачей, поскольку позволит существенно сократить время разработки конечного продукта. Кроме того на сегодняшний день она полностью не реализована, и тот кто сделает это первым будет иметь существенное преимущество над конкурентами.

Список источников

- Хвищук, А.Ю. Современные средства генерирования VHDL описаний аппаратуры при проектировании программируемых схем FPGA / Хвищук А.Ю., Григорьев А.В. // Микроелектроника и информатика — 2018. 25–я Всеросийская межвузовская научно–техническая конференция студентов и аспирантов: тезисы докладов. — М.:МИЭТ, 2018. — 316 с.

- Automated sports rim design in CAD system [Электронный ресурс] // IEEE Xplore Digital Library. — Режим доступа: https://ieeexplore.ieee.org/document/8376856/ — Загл. с экрана.

- A Methodology of Knowledge Management Based on Ontology in Collaborative Design [Электронный ресурс] // IEEE Xplore Digital Library. — Режим доступа: https://ieeexplore.ieee.org/document/4739796 — Загл. с экрана.

- Базы знаний интеллектуальных систем / Т.А. Гаврилова, В.Ф. Хорошевский — СПб: Питер, 2000. — 384 с.

- Исследование способов организации построения инструментальной интеллектуальной оболочки для проектирования сложных объектов на базе экспертных методик [Электронный ресурс] // Портал магистров ДонНТУ. — Режим доступа: http://masters.donntu.ru/2009/fvti/malyavka/diss/index.htm — Загл. с экрана.

- Процесс проектирования цифровых устройств с использованием ПЛИС [Электронный ресурс] // Электронная Образовательная Система МГТУ им. Н.Э.Баумана — Режим доступа: http://e-learning.bmstu.ru/moodle/pluginfile.php/2910/mod_resource/content/3/%D0%AD%D0%92%D0%9C_5.pdf — Загл. с экрана.

- Wikipedia contributors. (2018, December 26). Xilinx Vivado. In Wikipedia, The Free Encyclopedia. Retrieved 23:09, January 8, 2019, from https://en.wikipedia.org/w/index.php?title=Xilinx_Vivado&oldid=875403824 — Загл. с экрана.

- Wikipedia contributors. (2018, November 22). Intel Quartus Prime. In Wikipedia, The Free Encyclopedia. Retrieved 23:12, January 8, 2019, from https://en.wikipedia.org/w/index.php?title=Intel_Quartus_Prime&oldid=870064844 — Загл. с экрана.

- CLIPS [Электронный ресурс] : Материал из Википедии — свободной энциклопедии : Версия 95978215, сохранённая в 12:57 UTC 29 октября 2018 / Авторы Википедии // Википедия, свободная энциклопедия. — Электрон. дан. — Сан-Франциско: Фонд Викимедиа, 2018. — Режим доступа: https://ru.wikipedia.org/?oldid=95978215 — Загл. с экрана.

- Григорьев А.В. Методы поиска новых решений в специализированной инструментальной оболочке для создания интеллектуальных САПР // Десятая национальная конференция по искусственному интеллекту с международным участием КИИ–2006 (25–28 сентября 2006г., Обнинск): Труды конференции. — №. 3. — С. 1031–1046.

- Григорьев А.В. Теоретико–множественные операции над грамматиками как инструментарий для построения интеллектуальных САПР // XIII национальная конференция по искусственному интеллекту с международным участием КИИ–2012 (16–20 октября 2012 г., Белгород, Россия): Труды конференции. В 4–т., Белгород: Изд–во БГТУ, 2012, Т.3, с.202–209

- Григорьев А.В., Каспаров А.А. И/ИЛИ-ДЕРЕВО КАК СРЕДСТВО АБСТРАКТНОГО ПРЕДСТАВЛЕНИЯ БАЗЫ ЗНАНИЙ. — 2002.

- Григорьев А.В. Пути создания интеллектуальных САПР при различных уровнях квалификации экспертов //Донецк: ИПИИ МОН и НАН Украины

Наука и образование

. — 2005. — С. 758–763.

При написании данного реферата магистерская работа ещё не завершена. Окончательное завершение: июнь 2019 года. Полный текст работы и материалы по теме могут быть получены у автора или его руководителя после указанной даты.