Конфигурация ПЛИС с использованием высокоскоростной NOR flash памяти

Автор:Cliff Zitlaw

Автор перевода:Кудояр В.И.

Источник:

FPGA configuration using high-speed NOR flash | Embedded

Введение

Флэш-память NOR широко используется в качестве устройств конфигурации для ПЛИС. Использование ПЛИС в промышленных, коммуникационных и автомобильных приложениях ADAS обусловлено малыми задержками и высокой пропускной способностью NOR Flash. Хорошим примером приложения, требующего быстрого обмена данными с памятью, является система камер в автомобиле. Скорость, с которой изображение заднего вида появляется на дисплее приборной панели при включении зажигания, является задачей первого порядка.

Сразу после включения питания FPGA загружает конфигурацию, которая была сохранена в устройстве NOR. Когда передача завершена, FPGA переходит в активное (настроенное) состояние. FPGA включают в себя несколько вариантов настройки интерфейса памяти, которые часто включают в себя шину параллельного NOR, а также шину последовательного периферийного интерфейса (SPI). Устройства памяти, поддерживающие эти шины, всегда имели незначительную несовместимость между предложениями разных производителей, что затрудняло их многократное использование.

Недавно выпущенная спецификация JEDEC xSPI была разработана совместно со всеми основными производителями флэш-памяти NOR. Новый стандарт завершает десятилетия, когда производители NOR Flash самостоятельно разрабатывают продукты, не придерживаясь единого определения. Хотя незначительные различия все еще существуют, основные функциональные возможности JEDEC xSPI теперь идентичны в предложениях от всех производителей. Спецификация JEDEC xSPI стандартизирует шинные транзакции, команды и широкий набор внутренних функций. В сочетании с высокой пропускной способностью флэш-память следующего поколения обеспечивает целый ряд новых приложений и возможностей. Например, семейство Semper NOR Flash от Cypress соответствует спецификации JEDEC xSPI и обеспечивает постоянную скорость чтения 400 МБ / с, которая хорошо подходит для использования в качестве конфигурационной памяти FPGA. Для сравнения: скорость передачи данных 400 МБ / с позволяет передавать содержимое устройства 128 МБ (1 ГБ) за 320 мс.

История конфигурации ПЛИС

Когда ПЛИС впервые стали доступны, предпочтительной конфигурационной памятью была либо параллельная EPROM, либо параллельная EEPROM. Со временем появилась технология NOR Flash, получившая широкое распространение благодаря встроенной функции перепрограммирования и экономичности. Второй эволюционный переход состоял в том, что интерфейс памяти SPI сместил параллельный интерфейс NOR в большинстве приложений. Сегодняшние предложения памяти SPI предлагают высокую плотность, небольшие размеры пакетов, высокую пропускную способность чтения и, возможно, самое главное, эффективный интерфейс с низким числом выводов.

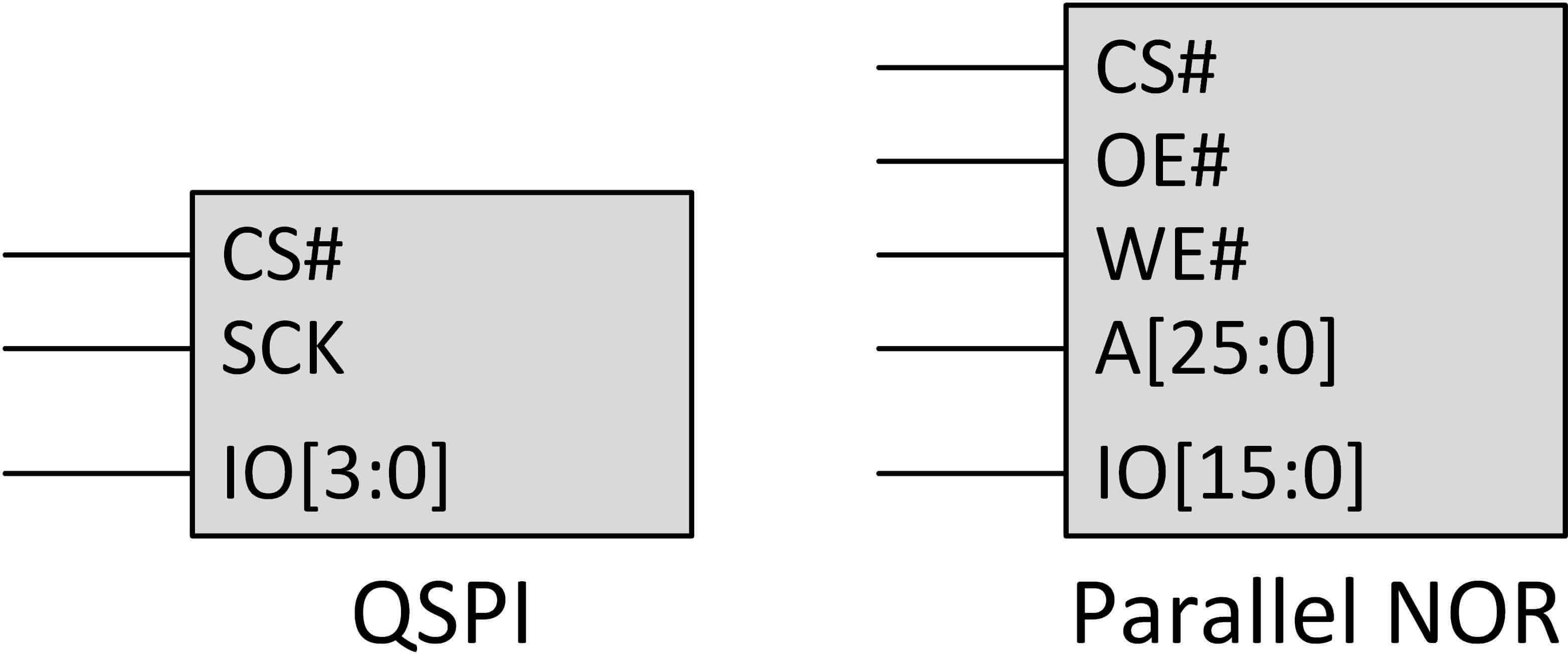

Рисунок 1 - Интерфейсы Gigabit Quad SPI (6-контактный) и Parallel NOR (45-контактный)

На рисунке 1 показана схема расположения одного гигабитного SPI-устройства в сравнении с одним гигабитным продуктом Parallel NOR. Для одной гигабитной памяти устройство Quad Serial Peripheral Interface (QSPI) имеет шестиконтактный интерфейс, а для устройства Parallel NOR требуется 45 контактов. Это резкое различие в количестве выводов привело к тому, что устройства QSPI стали широко использоваться в качестве предпочтительного интерфейса конфигурации. Интерфейс QSPI позволяет изменять плотность без изменения занимаемой площади устройства.

Скорость настройки FPGA

По мере сокращения узлов процесса устройства ПЛИС продолжают увеличивать объем доступной программируемой логики. В свою очередь, это приводит к требованию более высокой плотности и более быстрой конфигурации памяти. Современные FPGA требуют до 128 МБ данных для загрузки в течение периода конфигурации. Эти битовые потоки конфигурации высокой плотности требуют более длительного периода времени для передачи с устройства NOR Flash на FPGA. Интерфейс конфигурации не только оптимизирован для максимизации пропускной способности чтения, но и направлен на облегчение взаимодействия между различными производителями NOR Flash.

SPI пропускная способность чтения

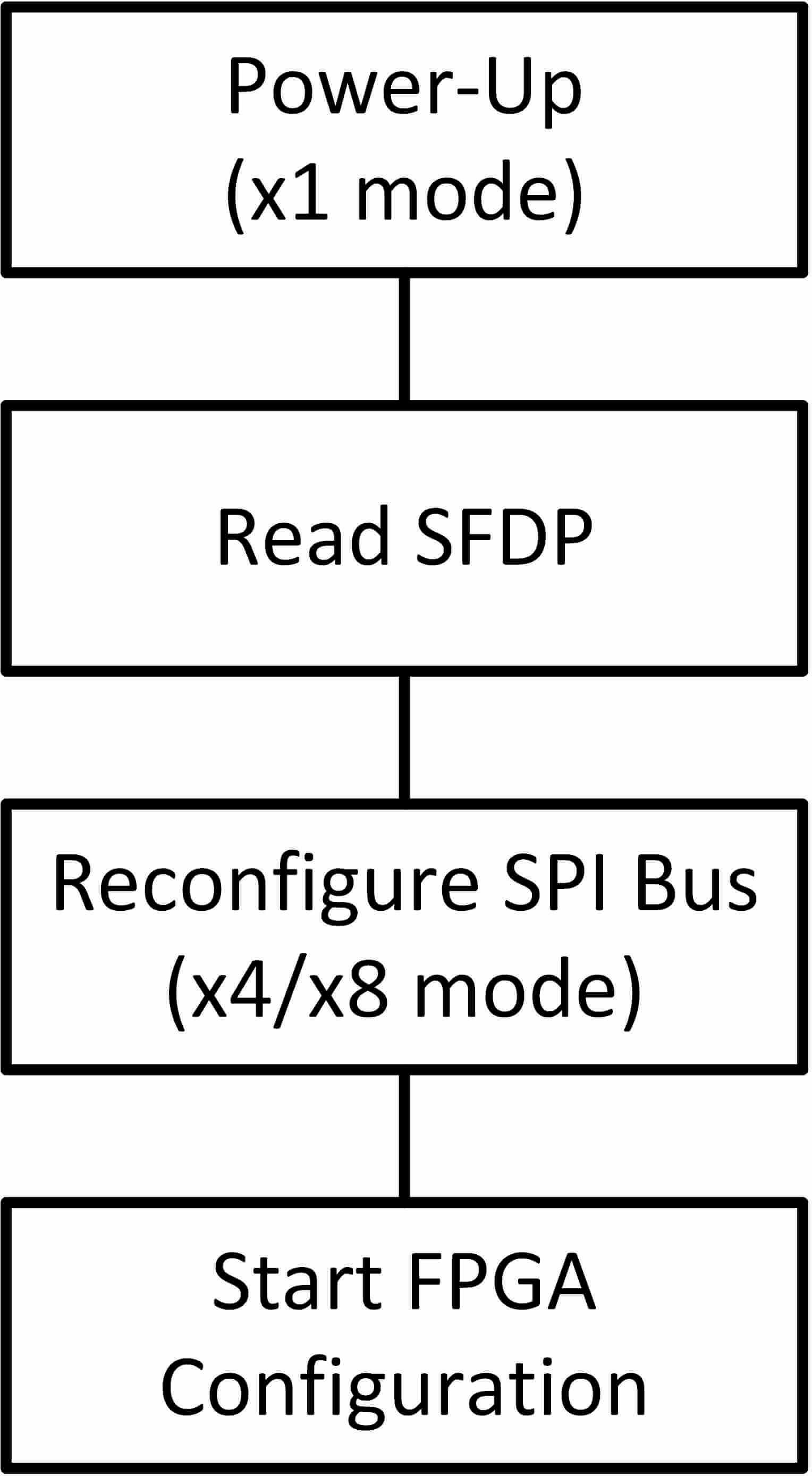

За последние несколько лет пропускная способность чтения SPI значительно увеличилась, начиная с оригинального интерфейса SPI, работающего в режиме x1, вплоть до современных предложений QSPI, использующих x4 DDR. Как видно из таблицы 1, флэш-устройства следующего поколения способны обеспечить еще одно повышение производительности шины SPI.

Таблица 1 - Параметры пропускной способности чтения SPI для устройств флэш-памяти.

Современные устройства SPI имеют возможность постоянной настройки на фиксированную ширину шины и тип передачи, которые сразу же включаются при включении питания. Эта постоянная конфигурация также должна поддерживаться FPGA, чтобы позволить процессу конфигурации начаться сразу после включения питания.

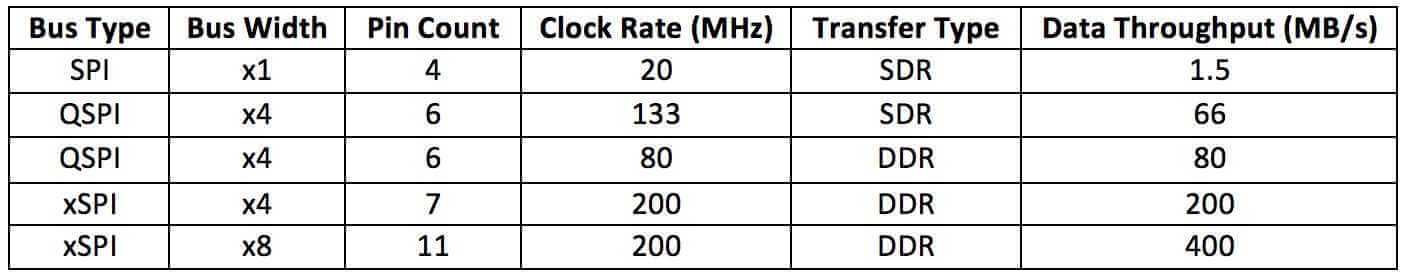

В качестве альтернативы, память SPI может отключаться при включении питания в режиме x1, который позволяет хост-системе (FPGA) запрашивать память о характеристиках, находящихся в таблице Serial Flash Discoverable Parameters (SFDP). Этот режим x1 стал стандартной функцией, поддерживаемой несколькими поставщиками памяти, и позволяет FPGA извлекать критическую информацию о функциональности устройства. После того, как характеристики устройства были получены, контроллер памяти FPGA и устройство памяти SPI могут быть быстро перенастроены для максимальной производительности чтения.

Рисунок 2 - Последовательность флэш-памяти (SFDP) используется для настройки функциональности шины SPI при включении питания.

Поиск ключевой информации об устройстве с использованием встроенной таблицы SFDP будет иметь решающее значение при использовании устройств флэш-памяти следующего поколения, которые могут работать с шинами x1, x4 или x8, а также с типами передачи SDR или DDR. Выбор ширины шины и типа передачи должен соответствовать инфраструктуре интерфейса шины, реализованной в FPGA.

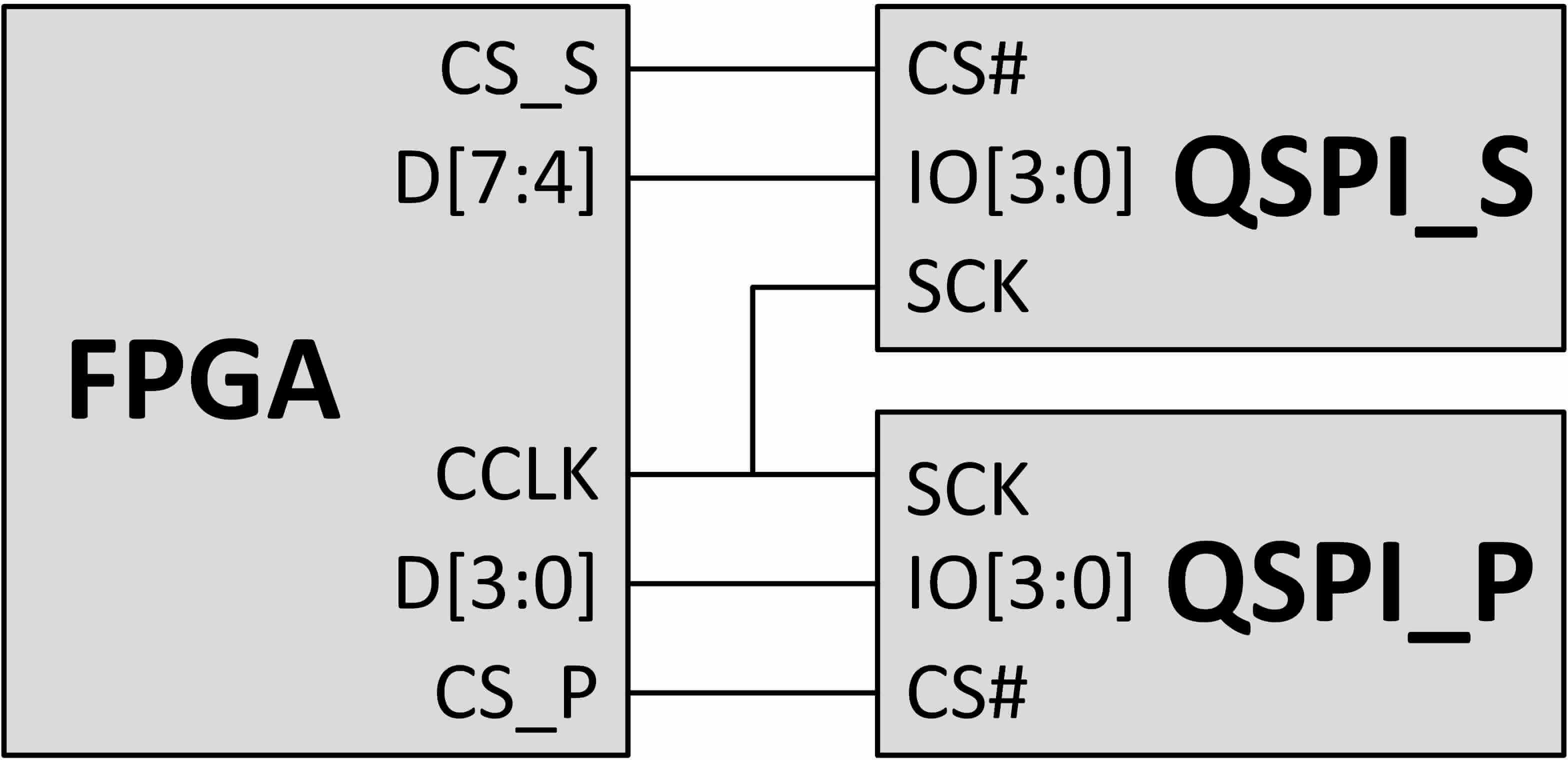

Двойной интерфейс конфигурации QSPI

Чтобы сократить время настройки ПЛИС, многие современные ПЛИС позволяют разделить поток битов конфигурации на два устройства QSPI (рисунок 3). Эти два устройства QSPI подключены параллельно, где нижний полубайт битового потока сохраняется в «первичном» устройстве QSPI (QSPI_P), а верхний полубайт битового потока сохраняется во «вторичном» устройстве QSPI (QSPI_S). Эти два устройства работают параллельно при загрузке потока битов, что фактически удваивает скорость передачи считанных данных.

Обратите внимание, что интерфейс в значительной степени независим для обоих устройств, за исключением общей линии SCK. Совместно используемая линия SCK реализована для минимизации перекосов синхронизации при чтении устройств в параллельном (то есть одновременном) режиме. Доступ к устройствам может происходить по одному или к обоим устройствам одновременно при выполнении одной и той же операции с идентичным целевым адресом.

Рисунок 3 - Интерфейс двойной конфигурации QSPI (11 контактов) позволяет разделить поток битов конфигурации на два устройства QSPI, чтобы эффективно удвоить скорость передачи считанных данных.

Эта 11-контактная конфигурация с двумя QSPI привлекательна, когда большие устройства FPGA требуют, чтобы биты большой конфигурации передавались максимально быстро.