Abstract

Introduction

The purpose and problems of work

Prospective scientific novelty

Planned practical value

The review of existing development on a theme

Current and planned results

Conclusion

The list of sources

Introduction

The major part of any digital device is the operating automatic device. The device of management can be realized in the form of the automatic device with programmed logic or the automatic device with rigid logic. Recently even more often programmed logic integrated schemes are applied to realization of operating automatic devices with rigid logic (FPGA).

It is connected by that for last thirty years there was an explosive growth of density of integration of schemes that has led to an opportunity of release of schemes containing on one crystal millions logic gates. As a result there was possible a realization of complex digital devices on several, or even to one LSI.

Now let out by industry LSI it is possible to divide into 2 classes: standard LSI and specialized LSI. To standard LSI widely duplicated microprocessors and sets of their support, a microcircuit of memory, alarm processors, etc. concern

Specialized LSI are divided into some subclasses: completely custom-made (Full Custom), semicustom (Semi - Custom) and programmed by the user (Field Programmable). The main lack custom-made and semicustom specialized LSI is high cost of development of devices on their base (the order of tens-hundreds thousand dollars).

Complex FPGA (CPLD) represent blocks of logic gates incorporated by a programmed switching matrix. Influencing programmed connections of switching matrix ПМЛ , it is possible to realize the demanded scheme. Modern CPLD, as a rule, are electrically programmed . CPLD save logic structure after disconnect of a feed.

Microcircuits programmed by users вентильных matrixes FPGA (Field Programmable Gate Arrays) consist of the big number of configured logic blocks (foreign term LUT), and the route-making resources providing their interconnections. Reception of concrete logic structure on the basis of FPGA, is realized by прошивания in triggers operating programmed interconnections (the shadow RAM) corresponding values. Leading developers of microcircuits CPLD and FPGA are firms Altera, Atmel, Lattice Semiconductor, Cypress Semiconductor, Xilinx.

Recently two tendencies are observed: constant increase in complexity of developed digital devices and simultaneous increase of flexibility and computing capacity of accessible hardware decisions. The first tendency has made demanded occurrence of essentially new means of designing and modelling of hardware digital devices, and the second has made its possible. During the development of system of the automated designing (CAD) intended for development of digital devices have passed some stages.

The first CAD for development of hardware devices simulated their manual development by the engineer – the mechanism of circuit editors and libraries of microcircuits was used.

At the second stage (in 80 – the beginning of 90th years of XX century) there were languages of the description of the equipment (HDL – Hardware Description Language) and CAD with support of these languages. As the precondition to transition to this stage mass release of programmed logic schemes (FPGA) and occurrence reconfigured chips of class FPGA has served.

The purpose and problems of work

- The analysis of efficiency of the application of existing methods of optimization of operating automatic devices from the point of view of hardware expenses, to the operating automatic devices, constructed on базеCPLD and FPGA.

- Research of existing means of the automated development of digital devices (in particular operating automatic devices).

- Development of new methods of the automated designing operating automatic devices and development of the software supporting these methods.

Prospective scientific novelty

Scientific novelty of the given job consists in development of new methods of the automated designing operating automatic devices. These methods are under construction on already developed both widely applied methods of development and designing of the software, such as the architecture operated by models (MDA - Model-Driven Design) and universal language of modelling (UML - Unified Modelling Language). Also it is carried out research of efficiency of existing methods of optimization of structure of the operating automatic devices developed for custom-made microcircuits, for modern standard FPGA.

Planned practical value

Development the software can be used as one of elements of a workplace of the developer of digital devices. Existing products realizing the given function differ with much effort. At the same time as the base environment for the developed software the environment of development of applications and systems Eclipse has been chosen crossplatform. This environment is developed and supported by world famous company IBM. Environment extends on principles OpenSource (free of charge with the open initial code of system, with a legal opportunity of the subsequent expansion of functionality users of system) that favourably distinguishes it from other means of modelling now in use.

The review of existing development on a theme

Now for the description of logic structure of digital devices, as a rule, are used highlevel languages of the description of the equipment (Hardware Description Languages - HDL). The Most widespread among them are languages VHDL and Verilog. However direct realization of operating automatic devices in these languages is labour-intensive process. Therefore the special tools have been included in structure of many foreign CAD, allowing to simplify development of operating automatic devices. So module FSM is included in structure CAD Active - HDL firms Aldec. This module possesses the multipurpose graphic interface, for the description of operating automatic devices. However module FSM possesses a number of lacks. In particular, the form of record of the operating automatic device demands knowledge of language HDL. So, conditions and signals given out in operational tops should be written down in the form of синтаксически correct expressions of the chosen language of the description of the equipment. The main lack of the module is absence of any optimization of structure of the received operating automatic device. The code generated by this subsystem, is not optimum from the point of view of expenses of the area of a crystal.

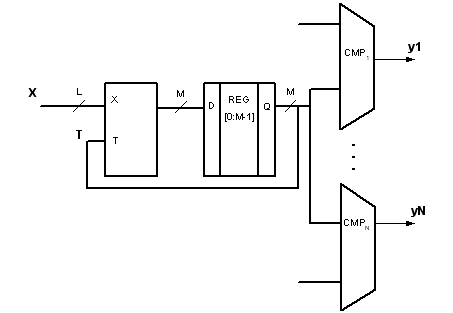

During carrying out of research it has been established, that the behavioural description of the operating automatic device generated by module FSM is realized by means of synthesis (Synplify) as Moore 's automatic device with monadic coding statuses. Advantage of such realization is the raised speed, lack greater hardware expenses. The block diagram of this realization is resulted in figure 1 [7].

Figure 1. Structure of the automatic device with monadic coding statuses

For such structure a plenty of used triggers, in comparison with traditional realizations is characteristic. Number of used triggers equally: R = M, where M – number of statuses the column. However at such structure functions of excitation of the automatic device and, accordingly, their logic schemes realizing become simpler. It occurs owing to monadic coding of statuses as at this coding each term of functions of excitation includes only one category of a code of statuses T. That is the formula of function of excitation (1) for such structure generally contains smaller quantity of terms, than at binary coding statuses of the automatic device (2) (according to statistics [job 1] the average length of chain X is in an interval from 1 up to 1,2) [6]:

Also at monadic coding statuses of the automatic device the quantity necessary for realization of the scheme of inverters decreases. It occurs due to absence of necessity of inverting of categories of a code of statuses.

Thus, advantages of this method, smaller complexity of functions of excitation (it is especially shown at reduction разветленности the automatic device) and соответсвенно higher speed of the automatic device is. Lacks are considerably a plenty of used trigger schemes (it is especially shown at increase in statuses the column: R M, at monadic coding; R log 2 M, at binary coding); and a greater equipment room затратность schemes of formation of target signals (at absence in FPGA elements XOR).

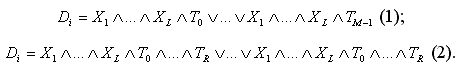

Are known, however, and other methods of optimization of structure of automatic devices on FPGA. Classification of these methods [1] is resulted in figure 2.

Figure 2. Classification of methods of optimization of automatic devices.

However recently becomes more and more obvious, that the similar approach to designing is close to exhaustion of the opportunities. Occurrence of logic cells new, more and more high-speed and containing a lot on a crystal of microcircuits FPGA displaces a priority by development of devices from minimization of hardware expenses in the received device or maximization of speed of the received device – on maintenance of reliability and excellent job of the received device at as much as possible short cycle to development.

One of the most perspective ways of the sanction of this problem is use for designing hardware systems, means based on earlier developed means of designing of complex systems for the software, such as use of architecture operated by models (MDA – Model - Driven Architecture) and the unified language modelling (UML – Unified Modeling Language).

MDA it has been offered by group OMG (Object Management Group) in 2000 [3]. Main idea MDA is the description of complex systems in the form of a set of the models costing at various levels of abstraction, rather each other, and an opportunity of transformation of models of one level in model of other level of abstraction [3]. Result of such transformations is reception of realizations of model independent of a platform, for various platforms.

Now there is a set of environments of the designing supporting architecture operated by models and language UML for the description of models which are focused on development of the software (Eclipse, Poseidon, ArgoUML, etc.). Many of these environments are expanded products (i.e. it is possible to connect additional modules of foreign developers to them), the decision to construct CAD for operating automatic devices on the basis of one of available environments of designing therefore was accepted.

As the base environment it is chosen Eclipse, it мотивировано by that, what is it environment is legally free-of-charge crossplatform a product with the open initial code. Except for it Eclipse it was initially developed as the base expanded environment, therefore the developed, well documentary interface of connection of additional modules is included in it. A number of similar modules is already developed, in particular it is possible to allocate module UniMod – intended for automatic (SWITCH) programming. [4]

Current and planned results

At the first stage of job above магистерской job it has been carried out research of applicability of existing methods [1,6] optimizations of structure of operating automatic devices to modern standard FPGA [7].

As investigated structures of the automatic device were it is chosen PYC – structure and structure with monadic coding. As base FPGA for research are chosen FPGA companies Altera: EP1K10 (family ACEX1K) and EPM3032A (family MAX3000A). Microcircuit EP1K10 concerns to class FPGA, microcircuit EPM3032A concerns to class CPLD. Both these microcircuits distinguishes high speed (frequency of clocking up to 250 MHz) and low cost (for EP1K10 – from 10 $ up to 20 $, for EPM3032A from 1,7 $ up to 4 $). More detailed data about these FPGA are resulted in the application 3. Logic capacity of these microcircuits makes: EP1K10 – 600 equivalent logic gates; EPM3032A – 600 logic cells (LUT).

Necessity of program realization of methods of generation of a structural code of columns-automatic devices and application of optimization of this code follows from the analysis of existing problems and requirements.

The software product should possess the set forth above advantages (generation of a structural code on set the column, calculation of the demanded area of a crystal, etc.).

During the analysis of methods of optimization and constant expansion of their number there are certain requirements to realization of software product, the certain structure is formed.

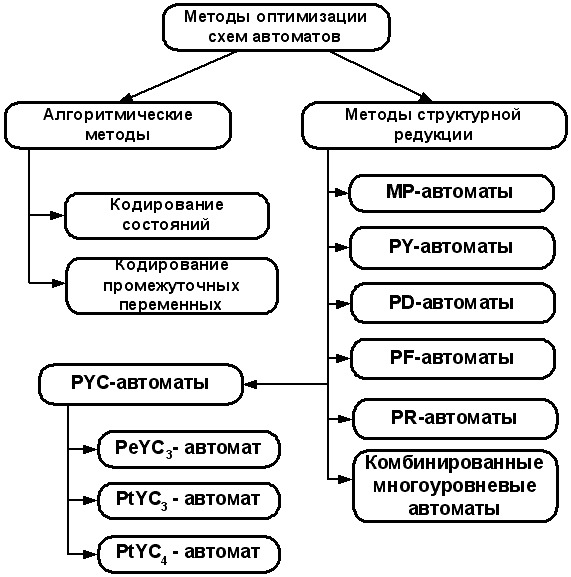

Figure 3 - Structure developed CAD (animation of 30 staff, 6 to/with, 3 recurrences, 6 KB)

The developed system should consist of following parts:

The Graphic editor who realizes an opportunity of graphic display, editing and creations demanded columns-schemes (FSM).

The Compiler which the column and reduction of textual representation internal language of the program (XML enables a textual set, XMI, or др .).

The Generator of a code with various optimisators , which will transform an internal code the column in concrete ( Moore or Mile) realization of the automatic device. [7]

After realization of software product will be carried out researches concerning efficiency of the generated code for various existing FPGA microcircuits, schedules of dependences, and also results of integration of the program with various existing means of synthesis will be constructed.

Conclusion

Result of job will be the software constructed on platform Eclipse with an open code and realizing generation of a code in language HDL. The program code will be generated in view of existing algorithms of optimization of operating automatic devices and FPGA is specified under concrete. Entrance parameters for software will be UML the scheme of realization of the operating automatic device.

The list of sources

1) А.А. Баркалов. Синтез устройств управления на программируемых логических устройствах. – Донецк. 2002.

2) В.М. Карпов. Теория автоматов. СПб. Питер. 2002.

3) OMG specifications, http://www. omg .org

4) Official website of UniMod , http://unimod.sourceforge.org

5) Часть 1. Технический обзор Платформы Eclipse – http://khpi-iip.mipk.kharkiv.edu/library/extent/prog/ETO/I.html

6) Зеленева И.Я. – «Методы синтеза многоуровневых структур управляющих автоматов на программируемых логических устройствах» – диссертационная работа.

7) Войтенко С.А. "Исследование методов проектирования управляющих автоматов на современных ПЛИС"

At a writing of the given author's abstract master job is not completed yet. Final end: January 2007г. The full text of job and all materials on a subject can be received at the author or the head after the specified date.