Элементная база нейровычислителей

В. Шахнов, А. Власов, А. Кузнецов.

Введение

Элементной базой нейровычислительных систем второго и третьего направлений (см. часть 1, часть 2) являются соответственно транспьютеры, цифровые сигнальные процессоры (DSP), ПЛИС и нейрочипы. Причем использование, как тех, так и других, позволяет сегодня реализовывать нейровычислители, функционирующие в реальном масштабе времени.

Элементной базой перспективных нейровычислителей являются нейрочипы. Их производство ведется во многих странах мира, причем большинство из них на сегодня ориентированны на закрытое использование (т.е. создавались для конкретных специализированных управляющих систем). Основные характеристики коммерчески доступных нейрочипов приведены в таблице 1 [1-8].

Прежде чем перейти рассмотрению наиболее интересных нейрочипов остановимся на их классификации.

По типу логики их можно разделить на цифровые, аналоговые и гибридные.

По типу реализации нейроалгоритмов: с полностью аппаратной реализаций и с программно-аппаратной реализацией (когда нейроалгоритмы хранятся в ПЗУ).

По характеру реализации нелинейных преобразований: на нейрочипы с жесткой структурой нейронов (аппаратно реализованных) и нейрочипы с настраиваемой структурой нейронов (перепрограммируемые).

По возможностям построения нейросетей: нейрочипы с жесткой и переменной нейросетевой структурой (т.е. нейрочипы в которых топология нейросетей реализована жестко или гибко).

Процессорные матрицы (систолические процессоры) - это чипы, обычно близкие к обычным RISC процессорам и объединяющее в своем составе некоторое число процессорных элементов, вся же остальная логика, как правило, должна быть реализована на базе периферийных схем.

В отдельный класс следует выделить так называемые нейросигнальные процессоры, ядро которых представляет собой типовой сигнальный процессор, а реализованная на кристалле дополнительная логика обеспечивает выполнение нейросетевых операций (например, дополнительный векторный процессор и т.п.).

Обобщенная классификация нейрочипов приведена на рис.1.

Рис.1. Обобщенная классификация нейрочипов.

Кроме широко спектра фирм и корпораций (таблица 1), исследования в области современных нейропроцессоров проводят многие лаборатории и университеты, среди которых можно отметить [2]:

- В США: Naval Lab, MIT Lab, Пенсельванский Университет, Колумбийский Университет, Аризонский Университет, Иллинойский Университет и др.

- В Европе: Берлинский Технический Университет, Технический Университет в Карлсруе и др.

- В России: МФТИ, Ульяновский Государственный Технический Университет, МГТУ им.Н.Э.Баумана (более десятка лабораторий занимающихся вопросами нейровычислителей на четырех факультетах: "Информатики и систем управления", "Специального машиностроения", "Радиоэлектроники и лазерной техники", "Биомедицинских систем"), Красноярский Государственный Технический Университет, Ростовский Государственный Университет и др.

Для оперативного информарования научной общественности и создании единого образовательного пространства в области нейроинформатики на кафедре "Конструирование и технология производства электронной аппаратуры" в рамках программ министерства образования России: Научно-методическая программа "Научно-методическое обеспечение дистаницонного образования" и Научно-технической программы "вычислительная техника, автоматизация, и интеграция сетей" проводятся работы по созданию интерактивной глобальной информационно-обучающей системы в области нейрокомпьютеров и нейроинформатикии (http://neurnews.iu4.bmstu.ru, http://cdl.iu4.bmstu.ru).

Разработка нейрочипов ведется во многих странах мира. На сегодня [2] выделяют две базовые линии развития вычислительных систем с массовым параллелизмом (ВСМП) : ВСМП с модифицированными последовательными алгоритмами, характерными для однопроцессорных фоннеймановских алгоритмов и ВСМП на основе принципиально новых сверпараллельных нейросетевых алгоритмов решения различных задач (на базе нейроматематике).

Таблица 1. Характеристики нейрочипов.

| Наименование | Фирма изготовитель | Разряд-ность, бит | Максимальное количество синапсов* | Максимальное число слоев** | Примечание |

|---|---|---|---|---|---|

| MA16 | Siemens | 48 (умножители и сумматоры) | - | - | 400 ММАС. |

| NNP (Neural Networks Processor) | Accurate Automation | Nx16 | - | - | MIMD, N - число процессоров. |

| СNAPS-1064 | Adaptive Solutions | 16 | 128 Кбайт | 64 | |

| 100 NAP Chip | HNC | 32 | 512 Кбайт | 4 | Плав. Арифм. 4 процессорных элемента |

| Neuro Matrix NM6403, Такт. частота 50 МГц. | Модуль, Россия | 64 (вект. процессор), 32 RISC ядро | 4096 шт. | 24 | Совместим с портами TMS320C4x |

| Neuro Matrix NM6404, Такт. частота 133 МГц. | Модуль, Россия | 64 (вект. процессор), 32 RISC ядро | 4096 шт. | ~48 | Совместим с портами TMS320C4x |

| CLNN 32 CLNN 64 | Bellcore | 32 64 |

496 1024 |

32 нейрона | 108 перекл./с 2 x 108 перекл./с |

| NC 3001 | NeuriGam | 16 | 4096 шт. | 32 | |

| ZISC 036 (Zero Instruction Set Computer) | IBM | 64 разр. входного вектора | - | 36 нейронов | Частота 20МГц, Векторно-прототипный нейрочип |

| ETANN 80170NW | Intel | 64 входа | Два банка весов 64х80 | 64 нейрона в слое, 3 слоя. | Аналоговая |

| MD-1220 | Micro Devices | 16 | 64 шт. | 8 | 8 нейронов |

| MT 19003 - Neural Instruction Set Processor | Micro Circuit Engineering (MCE) | 16 разр. Умножитель 35 разр. сумматор | - | 1 | RISC МП c 7 специальными командами |

| Neuro Fuzzu | National Semiconductor | - | - | - | |

| NI 1000 | Nestor | 5-16 (одного нейрона) | - | 1024 прототипных 256 мерных векторов | Векторно-прототипный нейрочип |

| NLX420 (NLX 110, 230) | Adaptive Logic | 16 | 1 Мбайт | 16 | 16 процессорных элементов |

| OBL Chip | Oxford Computer | 16 | 16 Мбайт | - | |

| L-Neuro 1.0 L-Neuro 2.3 |

Philips | 16 16 |

1536 |

16 нейронов 192 (12х16) |

26 МГц 60 МГц |

| RSC (Speech Recognition Chip) - 164 | Sensory Circuits | - | - | - | |

| ORC 110xx (Object Recognizer Chip) | Synaptics | - | - | - | |

| Pram-256 Chip | UCLi Ltd. | 8 (одного нейрона) | - | 256 нейронов | 33МГц. |

| SAND | Datafactory | 16 | - | 4 | 200 MCPS |

| ACC | 16 | - | - | ||

| Геркулес | Россия | 16 | 1 Мбайт | 64 | |

| Neuro Classifier | Университет Твента, DESY | 70 вх. нейронов | - | 6 (внутр) 1 вх., 1 вых. | 2 х 1010 перекл./с |

| ANNA | AT&T | Число нейроннов 16-256 | 4096 весов | - | Число входов у нейрона 256-16. |

| WSC (Wafer Scale Integration) | Hitachi | - | 64 связи на нейрон | 576 нейронов | |

| SASLM2 | Mitsubishi | 2 (одного нейрона) | - | 4096(64x64) нейронов | 50 МГц |

| TOTEM | Kent (Univer UK), di Trento (Italy) | 16 (одного нейрона) | - | 64 нейрона | 30 МГц |

| Neuron 3120, Neurom 3150 | Echelon (США) | 8 бит (шина данных) | - | - | Наличие параллельных, последовательных и коммуникацинных портов |

- * - максимальное число синапсов определяет размер внутрикристалльной памяти весов.

- ** - максимальное число слоёв определяется числом операций умножения с накоплением, выполняемых за один такт для операндов длиной 8 бит.

Для оценки производительности нейровычислителей используются следующие показатели:

- CUPS (connections update per second) - число измененных значений весов в секунду (оценивает скорость обучения).

- CPS (connections per second) - число соединений (умножений с накоплением) в секунду (оценивает производительность).

- CPSPW = CPS/Nw, где Nw - число синапсов в нейроне.

- CPPS - число соединений примитовов в секунду, CPPS=CPS*Bw*Bs, где Bw, Bs - разрядность весов и синапсов.

- MMAC - миллионов умножений с накоплением в секунду.

Ориентация в выполнении нейросетевых операций обуславливает с одной стороны повышение скоростей обмена между памятью и параллельными арифметическими устройствами, а с другой стороны уменьшение времени весового суммирования (умножения и накопления) за счет применения фиксированного набора команд типа регистр-регистр.

Нейрочипы: анализ и сравнительные характеристики.

Нейросигнальный процессор NeuroMatrix NM6403 (фирма Модуль [9], Россия).

Рис.2. Стуктура NeuroMatrix NM6403.

Основой NeuroMatrix NM6403 является процессорное ядро NeuroMatrixCore (NMC), которое представляет собой синтезабильную модель высокопроизводительного DSP процессора с архитектурой VLIM/SIMD (язык Verilog). Ядро состоит из двух базовых блоков: 32-битного RISC процессора и 64 битного векторного процессора, обеспечивающего выполнение векторных операций над данными переменной разрядности (патент РФ.N2131145). Имеются два идентичных программируемых интерфейса для работы с внешней памятью различного типа и два коммуникационных порта, аппаратно совместимых с портами ЦПС TMS320C4x, для возможности построения многопроцессорных систем.

Основные характеристики:

- тактовая частота - 50 MГц (20нс - время выполнения любой инструкции);

- технология КМОП 0.5 мкм;

- корпус 256BGA;

- напряжение питания от 2.7 до 3.6 В;

- потребляемая мощность при 50MHz около 1.3 Вт;

- условия эксплуатации: -60...+85 C.

RISC-ядро

- 5-ти ступенчатый 32-разрядный конвейер;

- 32- и 64-разрядные команды (обычно выполняется две операции в одной команде);

- два адресных генератора, адресное пространство - 16 GB;

- два 64-разрядных программируемых интерфейса с SRAM/DRAM-разделяемой памятью;

- формат данных - 32-разрядные целые;

- регистры:

- 8 32-разрядных регистров общего назначения;

- 8 32-разрядных адресных регистров;

- специальные регистры управления и состояния;

- два высокоскоростных коммуникационных порта ввода/вывода,

- аппаратно совместимых с портами TMS320C4x.

VECTOR-сопроцессор

- переменная 1-64-разрядная длина векторных операндов и результатов;

- формат данных - целые числа, упакованные в 64-разрядные блоки, в форме слов переменной длины от 1 до 64 разрядов каждое;

- поддержка векторно-матричных и матрично-матричных операций;

- два типа функций насыщения на кристалле;

- три внутренних 32x64-разрядных RAM-блока.

Производительность:

- скалярные операции:

- 50 MIPS;

- 200 MOPS для 32-разрядных данных;

- векторные операции:

- I/O и интерфейсы с памятью:

- пропускная способность двух 64-разрядных интерфейсов с памятью - до 800 Мбайт/сек;

- I/O коммуникационные порты - до 20 Мбайт/сек каждый.

от 50 до 50.000+ MMAC (миллионов умножений с накоплением в секунду);

Базовыми для нейропроцессора являются вычисления вида: Zi= f(Yi) = f (Ui+е(XjWij), (i=1, .. , M;j=, ..,N), где Zi - выходной сигнал i-ro нейрона, Xj - j-й входной сигнал слоя, Ui - смещение i-ro нейрона,Wij -весовой коэффициент j-го входа 1-го нейрона, Yi - сумма взвешенных входов i-го нейрона, f- функция активации, N - количество входных сигналов слоя, М - количество нейронов в слое; Операнды Zi, Xi, Ui и Wij представлены в дополнительном параллельном коде и могут иметь произвольную разрядность. Основными особенностями данного нейропроцессора являются:

- возможность работы с входными сигналами (синапсами) и весами переменной разрядности (от 1 до 64 бит), задаваемой программно, что обеспечивает уникальную способность нейропроцессора увеличивать производительность с уменьшением разрядности операндов;

- быстрая подкачка новых весов на фоне вычислений;

- (24 операции умножения с накоплением за один такт при длине операндов 8 бит);

- V аппаратная поддержка эмуляции нейросетей большой размерности;

- реализация функции активации в виде пороговой функции или функции ограничения;

- наличие двух широких шин (по 64 разряда) для работы с внешней памятью любого типа: до 4Мб SRAM и до 16 Гб DRAM;

- наличие двух байтовых коммуникационных портов ввода/вывода, аппаратно совместимых с коммуникационными портами TMS320C4x для реализации параллельных распределенных вычислительных систем большой производительности.

- возможность работать с данными переменной разрядности по различным алгоритмам, реализуемым с помощью хранящихся во внешнем ОЗУ программ.

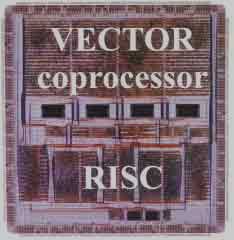

Рис.3. Конструктивная реализация NeuroMatrix 6403.

Технические характеристики:

- число вентилей на кристалле - 100.000;

- размер кристалла - 10 мм * 10.5 мм при технологии 0.7 мкм;

- потребляемая мощность - не более 3 Вт;

- пиковая производительность для байтных операндов - 720 MCPS (миллионов соединений или умножений с накоплением в сек.) при тактовой частоте 30 Мгц; при бинарных операциях - 8640 MCPS.

Нейропроцессор благодаря своей универсальности сможет применяться как базовый элемент для плат нейроускорителей PC, для создания нейрокомпьютерных параллельных вычислительных систем большой производительности, а также для аппаратной поддержки операций над матрицами большой размерности и в задачах цифровой обработки сигналов. Используется в нейроускорителях фирмы Модуль (Россия) [9].

Процессор NeuroMatrixR NM6404

Рис.4 Конструктивная реализация NeuroMatrixR NM6404

NeuroMatrixR NM6404 [9] представляет собой высокопроизводительный DSP-ориентированный RISC микропроцессор. В его состав входят два основных блока: 32-разрядное RISC-ядро и 64-разрядное VECTOR-сопроцессор для поддержки операций над векторами с элементами переменной разрядности. NM6404 по системе команд совместим с предыдущей версией NM6403. Имеются два идентичных программируемых интерфейса для работы с внешней памятью различного типа и два коммуникационных порта, аппаратно совместимых с портами ЦПС TMS320C4x, для возможности построения многопроцессорных систем.

Особенности:

- тактовая частота - 133 MГц (8нс - время выполнения любой инструкции);

- технология КМОП 0.25 мкм;

- корпус PQFP256;

- напряжение питания от 2.5 В, 3.3 В, 5 В;

- потребляемая мощность - около 1.0 Вт; условия эксплуатации: -40...+80 C.

RISC-ядро:

- 5-ти ступенчатый 32-разрядный конвейер;

- 32- и 64-бит команды (обычно выполняется две операции в одной команде);

- 2 Мбит внутреннее ОЗУ;

- доступ к внутренней памяти соседей;

- два адресных генератора, адресное пространство - 16 GB;

- два 64-разрядных программируемых интерфейса с SDRAM/SRAM/DRAM/Flash ROM разделяемой памятью;

- 4 одновременных доступа к внутренней памяти; широковещательный режим доступа к внешней памяти;

- 64 К Boot ROM; формат данных - 32-разрядные целые; 4 канала DMA;

- два коммуникационных порта ввода/вывода, аппаратно совместимых с портами TMS320C4x; JTAG-совместимый отладочный интерфейс; система управления потребляемой мощностью.

VECTOR-сопроцессор

- от 1 до 64-разрядная длина векторных операндов и результатов;

- формат данных - целые числа, упакованные в 64-разрядные блоки, в форме слов переменной длины от 1 до 64 разрядов каждое;

- поддержка векторно-матричных и матрично-матричных операций; 16 тактов на перезагрузку матрицы коэффициентов;

- свопирование рабочей и теневой матрицы; два типа функций насыщения на кристалле.

Производительность:

скалярные операции:

- 133 MIPS;

- 399 MOPS для 32-разрядных данных;

векторные операции:

- от 133 до 38.000+ MMAC (миллионов умножений с накоплением в секунду);

- I/O и интерфейсы с памятью:

- пропускная способность двух 64-разрядных интерфейсов с памятью - 2128 Мбайт/сек;

- I/O коммуникационные порты - до 20 Мбайт/сек каждый.

Neural Networks Processor - NNP (Accurate Automation Corp.)

Процессор NNP (Neural Networks Processor) построен по MIMD архитектуре, то есть состоит из нескольких миниатюрных процессоров, работающих параллельно. Каждый из этих процессоров представляет собой быстрый 16 разрядный вычислитель с памятью для хранения синаптических весов. Процессор имеет всего 9 простых команд. Процессоры на кристалле связаны друг с другом локальной шиной. NNP создан в коммерческих целях и доступен на рынке.

В комплект поставки процессора включены средства разработки программ, а так же библиотека подпрограмм с реализованными нейросетевыми алгоритмами, такими как сети Хопфилда, сети Кохенена и другими. Процессор поставляется на платах под шины ISA, VME. Производительность - 140MCPS для однопроцессорной системы, 1.4GCPS для 10-и процессорной системы.

Нейропроцессор МА16 (фирма Siemens).

Рис.5. Нейрочип МА16 (Siemens).

МА16 изготовлен по технологии КМОП (1 мкм), состоит из 610 тыс. транзисторов и выполняет до 400 млн. операций умножения и сложения в секунду. Используется в качестве элементной базы нейрокомпьютера Synaps 1 и нейроускорителей Synaps 2 и Synaps 3 (распространяемых сегодня на рынке французской фирмой Tiga Technologies).

МА16 представляет собой программируемый каскадируемый процессор для векторных и матричных операций. Он поддерживает на аппаратном уровне следующие операции:

- матричное умножение;

- матричное сложение/вычитание;

- нормировка результата;

- вычисление векторной нормы (метрики L1 и L2);

- вычисление векторного расстояния (мера Манхэтэнна, геометрическое расстояние).

Рис.6. Функциональная схема МА16.

Процессор содержит четыре идентичных процессорных элемента, работающих параллельно. Входные данные имеют точность 16 бит, тактовая частота 50 мГц. Для операций матричного умножения/сложения скорость вычислений достигает 8_108 операций/с. Программное обеспечение работает в среде UNIX/XWIND и реализовано на C++. Нейронная сеть тоже описывается на С++ или может вводится интерактивно с помощью графического интерфейса типа OSF/Motif, что позволяет визуализировать конфигурацию чипа после отображения на него структуры сети. Хорошо развиты средства тестирования и эмуляции. С 1995 года МА16 является коммерчески доступным продуктом.

MD1220 (Micro Devices)

Цифровой нейрочип MD1220 фирмы Micro Devices содержит восемь неронов с 8 связями и 16 разрядные сумматоры. В внутрикристалльной памяти хранятся 16 разрядные веса. Входы имеют одноразрядные последовательные умножители с продолжительностью такта 7.2. мкс. Средняя производительность около 9 MCPS.

L-Neuro Philips

Нейропроцессор L-Neuro фирмы Philips один из первых нейропроцессоров. На сегодня широко известны две его модификации L-Neuro 1.0 и L-Neuro 2.3. Вторая версия имеет 12 слоев, а первая один слой из шестнадцати одноразрядных, или двух восьмиразрядных, или четырех 4-х разрядных, или двух восьмиразрядных процессорных элементов, т.е. имеет возможность работать мультиразрядном режиме. На кристалле реализован 1Кбайт памяти для хранения 1024 8 разрядных или 512 16 разрядных весов. Гибкая каскадируемая структура нейрочипа позволяет использовать его при реализации различных нейросетевых парадигм. При реализации 64 восьми разрядных процессорных элементов средняя производительность составляет 26 MCPS (32 MCUPS).

NLX-420 фирмы NeuroLogix

Каждый из 16 процессорных элементов нейрочипа NLX-420 фирмы NeuroLogix содержит 32 разрядный сумматор, логику параллельного выполнения 16 умножений. Средняя производительность 300 MCPS. Также имеется возможность каскадирования и мультиразрядных вычислений.

СБИС ETANN 80170NX фирмы INTEL

Аналоговая СБИС ETANN 80170NX фирмы INTEL содержит 64 входа, 16 внутренних уровней и 64 нейрона (пороговый усилитель с сигмоидной передаточной функцией). Каждый вход соединен с 64 синапсами. Передаточная функция нейрона в СБИС близка к сигмоиде.

Усиление передаточной функции определяет чувствительность нейрона. Низкое значение усиления позволяет интерпретировать выход нейрона как аналоговый, а высокое - как цифровой. Максимальное значение выхода нейрона определяется напряжением Vrefo. Веса ограничены интервалом [-2.5, 2.5]. Скорость прохождения сигнала по одному слою зависит от усиления и примерно равна 1,5 мкс, что и определяет быстродействие. Точность выполнения операций примерно эквивалентна 6 бит, быстродействие - 1,3-109 переключений/с. Обучение выполняется методом Back Propagation с помощью Intel Neural Network Training System (INNTS). Применяемое системное окружение представляет собой специальную версию пакета DynaMind. Обучение выполняется до получения приемлемого уровня ошибки выхода сети, и после достижения удовлетворительной работы веса загружаются в СБИС. Для реальной работы такого обучения недостаточно, так как программа симуляции не может точно смоделировать аналоговую работу СБИС и, например, не отслеживает флуктуации в передаточной функции каждого нейрона. Поэтому следующий этап обучения представляет собой так называемый chip-in-loop (CIL) training, когда после каждого цикла веса записываются в СБИС, и выход сети непосредственно используется в процессе обучения. ТочностьETANN 5-6 разрядов для весов и выходов.

Поскольку ETANN представляет собой аналоговую СБИС, то для ее надежной работы важны стабильные внешние условия. Специально сконструированный для этого модуль обеспечивает низкую пульсацию источника питания 5V < 5 мВ (напряжение питания 5 В) и температурную стабильность при 18°С 8Т < 1°С (потребляемая мощность ETANN 5 Вт).

СБИС CLNN32/CLNN64 фирмы Bellcore

Гибридный нейрочип CLNN32 состоит из 32 нейронов и 496 двунаправленных адаптивных синапсов. CLNN64 содержит только 1024 адаптивных синапсов. В наборе CLNN32/CLNN64 все нейроны взаимосвязаны, так что любая топология сети отображается подбором синапсов. Динамика сети полностью аналоговая, но значения синапсов хранятся/обновляются в цифровом виде с точностью 5 бит. На аппаратном уровне реализовано обучение сети - подбор весов происходит по алгоритму обучения машины Больцмана или Mean Field. Внутри также имеется некоррелированный генератор шума (32 канала), используемый при обучении по методу машины Больцмана. CLNN32 может быть использован независимо или совместно с CLNN64 для построения более сложной архитектуры сети. Производительность достигает 108 переключений/с (при работе с CLNN64 удваивается). Для CLNN32 это означает, что примерно 105 32-бит образцов/с или 32 аналоговых канала (с полосой пропускания 50 кГц) могут быть использованы для быстрого распознавания/обучения. Время распространения для одного слоя нейронов < 1 мкс. "Охлаждение" (по методу Больцмана) или MF обучение требует 10 -20 мкс. По сравнению с ETANN СБИС CLNN32 имеет следующие очевидные преимущества:

- быстрое обучение (микросекунды по сравнению с часами при C1L процессе);

- эффективный алгоритм обучения Больцмана, обеспечивающий быстрое нахождение "почти оптимального" решения;

- простые и быстрые процедуры чтения/записи весов, выполняемые в цифровом виде, что значительно увеличивает скорость обмена между сетевым сервером и клиентами в сети;

- легкая каскадируемостъ.

СБИС ANNA

Другим примером реализации гибридного нейрочипа является нейрочип ANNA фирмы AT&T. Логика нейрочипа - цифровая, хранение весов - аналоговое (на элементах динамической (конденсаторной) памяти). Чип содержит 4096 весов максимальное число нейронов 256. Точность весов 6 разрядов, для однослойной сети 64x64 производительность достигает 2.1. GCPS.

СБИС NeuroClassifier

Аналоговая СБИС NeuroClassifier создана в университете Твенте совместно с DESY. Ее архитектура состоит из входного слоя (70 входов, полоса пропускания до 4 Гбайт/с), шести внутренних слоев и одного выходного нейрона. Точность аналогового умножения 5 бит, время решения всего лишь 20 нс, что позволяет использовать NeuroClassifier в триггере первого уровня. Эквивалентное быстродействие примерно 2_1010 переключений/с.

SAND/1 (Simple Applicable Neural Device)

Компания Datafactory (бывшая INCO) выпустила на рынок SAND/1 (Simple Applicable Neural Device). SAND/1 представляет собой каскадно соединенные систолические процессоры оптимизированные для быстрого решения задач в нейросетевом базисе. Производительность одного процессора составляет 200 MCPS (миллионов связей в секунду). Процессор имеет четыре 16-и битных потока и 40 битный сумматор. SAND/1 был разработан Исследовательским центром в Карлсруе и Институтом микроэлектроники Штутгарта.

Inova N64000

Этот нейрочип фирмы Inova SIMD архитектуры относится также, как и предыдущий, к классу систолических нейропроцессоров. Он содержит 80 процессорных элементов, из которых 64 образуют основную матрицу, а 16 являются резервом, 4 Кбайта памяти весов и 32 регистра общего назначения. Арифметический модуль процессора имеет девять параллельных 16 разрядных умножителя и один 32 разрядный сумматор.

100 NAP (Hecht-Nielson Computer)

Другой систолический нейрочип 100 NAP фирмы Hecht-Nielson Computer содержит 4 32 разрядных процессорных элемента с плавающей точкой. Средняя производительность около 150 MFLOPS, адресуемое адресное пространство внекристалльной памяти 512 Кбайт.

MT19003 (Micro Circuit Engineering)

Нейрочип MT19003 фирмы Micro Circuit Engineering, также относится к классу систолических нейропроцессоров. Основой архитектуры является RISC ядро с семью специальными командами, 16 разрядный векторный умножитель и 32 разрядный сумматор, внутрикристалльная память для хранения весов отсутствует. Точность входов и весов 13 разрядов. Средняя производительность 50 MCPS.

NEURON - нейропроцессор фирмы Echelon (США).

Рис.7. Структурная схема нейрочипа NEURON 3150 фирмы Echelon (США).

Нейропроцессор NEURON ориентирован на создание кластерно-параллельных вычислительных систем. Программно-алгоритмическое обеспечение по управлению кластерной структурой реализовано внутри кристалла. Предложенная архитектура кристалла стала в настоящее время основой стандарта ANSI/EIA 709.1-1999 построения различных АСУ технологическими процессами [2].

В семействе нейрочипов NEURON выделяют: NEURON 3120 и NEURON 3150. Структурная схема NEURON 3150 приведена на рис7. Кристал содержит 2К динамической памяти для хранения весов и данных, 512 байт (EEPROM), для размещения управляющих программ. Для выполнения специализированных сетевых и управляющих операций в структуре кристалла имеется два спецвычислителя: Applications CPU, Network CPU. Так же следует отметить широкие коммуникационные возможности реализованные на кристалле.

ZISC036 - нейропроцессор фирмы IBM

Нейрочип ZISC036 (Zero Instructions Set Computer) фирмы IBM относится к нейрочипам векторно-прототипной архитектуры, т.е. алгоритм обучения стоится на соотношении входного вектора и запомненными прототипными векторами весов входов нейронов. Он содержит 36 нейронов. Ориентирован на решение широкого круга задач, в том числе задач распознавания образов и классификации. Каждый нейрон представляет собой независимый процессор. ZISC способен решать и real-time задачи (рис.8).

Рис.8. Функциональная схема процессора ZISC

Характеристики ZISC036:

- 36 нейронов

- Возможность соединения нескольких процессоров (каскадирования).

- От 1 до 64 компонент во входном векторе

- Наряжение питания 5V

- Потребляемая мощность - 1W при 16MHz

- Частота - 0-20MHz

- CMOS технология

- Входной вектор загружается через 3.5. мкс., результат появляется через 0.5 мкс.

Для увеличения производительности фирма IBM разработала ISA и PCI модули параллельно работающих ZISC процессоров.

Выводы:

Рассмотрев основные характеристики элементной базы нейровычислителей, от сигнальных процессоров, ПЛИС до нейрочипов в третьей части обзора мы перейдем к анализу вопросов структурно-функционального построения конкретных нейроускорителей и нейрокомпьютеров на элементной базе , рассмотренной в данном разделе.

Подводя итоги приведем сводные данные по производительности некоторых, наиболее интереснных, нейропроцессоров [1,10-12].

| Наименование нейрочипа | конфигурация | CPS | CPSPW | CPPS | CUPS |

|---|---|---|---|---|---|

| NLX420 | 32-16, 8 bit mode | 10M | 20K | 640M | - |

| 100 NAP | 4 chips, 2M wts, 16 bit mantissa | 250M | 125 | 256G | 64M |

| WSI (Hitachi) | 576 neuron Hopfield | 138M | 3.7 | 10G | - |

| N64000 (Inova) | 64-64-1, 8 bit mode | 871M | 128K | 56G | 220M |

| MA16 | 1 chip, 25MHz | 400M | 15M | 103G | - |

| ZISC036 | 64 8 bit element inp. Vector | - | - | - | - |

| MT19003 | 4-4-1-, 32 MHz | 32M | 32M | 6.8G | - |

| MD1220 | 8-8 | 9M | 1M | 142M | - |

| NI 1000 | 256 5 bit element inp. Vector | 40 000 vec in sec. | - | - | - |

| L-neuro-1 | 1-chip, 8 bit mode | 26M | 26K | 1.6G | 32M |

| NM6403 | 8 bit mode, 50MHz | 1200M | 150M | 77G | - |

* В таблице приведены средние округленные показатели производительности.

Литература:

- Проблемы построения и обучения нейронных сетей / под ред. А.И.Галушкина и В.А.Шахнова. - М. Изд-во Машиностроение. Библиотечка журнала Информационные технологии №1. 1999. 105 с.

- А.И.Галушкин Некоторые исторические аспекты развития элементной базы вычислительных систем с массовым параллелизмом (80- и 90- годы) // Нейрокомпьютер, №1. 2000. - С.68-82

- А.Н.Горбань, Д.А.Россиев Нейронные сети на персональном компьютере. - Новосибирск: Наука. Сибирская издательская фирма РАН, 1996. - 276 с.

- Э.Ю. Кирсанов Цифровые нейрокомпьютеры: Архитектура и схемотехника / Под ред. А.И.Галушкина. - Казань: Казанский Гос. У-т. 1995. 131 с.

- А.И. Власов. Аппаратная реализация нейровычислительных управляющих систем //Приборы и системы управления - 1999, №2, С.61-65.

- Роберт Хехт-Нильсен Нейрокомпьютинг: история, состояние, перспективы // Открытые системы. N4. 1998.

- А.И. Власов Нейросетевая реализация микропроцессорных систем активной акусто- и виброзащиты// Нейрокомпьютеры:разработка и применение, №1, 2000. С.40-44.

- http://neurnews.iu4.bmstu.ruu

- http://www.module.ru.

- П.А. Шевченко, Д.В.Фомин, В.М. Черников, П.Е. Виксне Применение микропроцессора NM6403 для эмуляции нейронных сетей // Нейрокомпьютеры и их применение 99. М.: ИПУ РАН, 1999. - С.81-90.

- C.Lindsey, T.Lindblat. Survey of neural network hardware. SPIE. Vol 2492. PP.1194-1205.

- K.Tahir Shah Automata, neural networks and parallel machines: some emerging principles. - World Scientific. 1999.